devicekb936929

kb936929 时间:2021-02-28 阅读:()

W9725G6KB4M4BANKS16BITDDR2SDRAMPublicationReleaseDate:Sep.

03,2012-1-RevisionA03TableofContents-1.

GENERALDESCRIPTION42.

FEATURES.

43.

ORDERINFORMATION54.

KEYPARAMETERS55.

BALLCONFIGURATION66.

BALLDESCRIPTION.

77.

BLOCKDIAGRAM88.

FUNCTIONALDESCRIPTION.

98.

1Power-upandInitializationSequence.

98.

2ModeRegisterandExtendedModeRegistersOperation108.

2.

1ModeRegisterSetCommand(MRS)108.

2.

2ExtendModeRegisterSetCommands(EMRS)118.

2.

2.

1ExtendModeRegisterSetCommand(1),EMR(1)118.

2.

2.

2DLLEnable/Disable.

128.

2.

2.

3ExtendModeRegisterSetCommand(2),EMR(2)138.

2.

2.

4ExtendModeRegisterSetCommand(3),EMR(3)148.

2.

3Off-ChipDriver(OCD)ImpedanceAdjustment158.

2.

3.

1ExtendedModeRegisterforOCDImpedanceAdjustment168.

2.

3.

2OCDImpedanceAdjust.

168.

2.

3.

3DriveMode178.

2.

4On-DieTermination(ODT)188.

2.

5ODTrelatedtimings188.

2.

5.

1MRScommandtoODTupdatedelay.

188.

3CommandFunction.

208.

3.

1BankActivateCommand.

208.

3.

2ReadCommand.

208.

3.

3WriteCommand218.

3.

4BurstReadwithAuto-prechargeCommand.

218.

3.

5BurstWritewithAuto-prechargeCommand.

218.

3.

6PrechargeAllCommand218.

3.

7SelfRefreshEntryCommand218.

3.

8SelfRefreshExitCommand.

228.

3.

9RefreshCommand.

228.

3.

10No-OperationCommand.

238.

3.

11DeviceDeselectCommand.

238.

4ReadandWriteaccessmodes238.

4.

1Posted23W9725G6KBPublicationReleaseDate:Sep.

03,2012-2-RevisionA038.

4.

1.

1Examplesofpostedoperation.

238.

4.

2Burstmodeoperation.

248.

4.

3Burstreadmodeoperation.

258.

4.

4Burstwritemodeoperation258.

4.

5Writedatamask268.

5BurstInterrupt268.

6Prechargeoperation.

278.

6.

1Burstreadoperationfollowedbyprecharge.

278.

6.

2Burstwriteoperationfollowedbyprecharge278.

7Auto-prechargeoperation278.

7.

1BurstreadwithAuto-precharge.

288.

7.

2BurstwritewithAuto-precharge288.

8RefreshOperation.

298.

9PowerDownMode.

298.

9.

1PowerDownEntry308.

9.

2PowerDownExit.

308.

10Inputclockfrequencychangeduringprechargepowerdown309.

OPERATIONMODE319.

1CommandTruthTable319.

2ClockEnable(CKE)TruthTableforSynchronousTransitions.

329.

3DataMask(DM)TruthTable.

329.

4FunctionTruthTable.

339.

5SimplifiedStatedDiagram.

3610.

ELECTRICALCHARACTERISTICS3710.

1AbsoluteMaximumRatings.

3710.

2OperatingTemperatureCondition.

3710.

3RecommendedDCOperatingConditions3810.

4ODTDCElectricalCharacteristics3810.

5InputDCLogicLevel.

3810.

6InputACLogicLevel.

3810.

7Capacitance3910.

8LeakageandOutputBufferCharacteristics3910.

9DCCharacteristics4010.

10IDDMeasurementTestParameters4210.

11ACCharacteristics.

4310.

11.

1ACCharacteristicsandOperatingConditionfor-18speedgrade4310.

11.

2ACCharacteristicsandOperatingConditionfor-25/25I/25A/25K/-3speedgrade.

4510.

12ACInputTestConditions.

6610.

13DifferentialInput/OutputACLogicLevels.

6610.

14ACOvershoot/UndershootSpecification6710.

14.

1ACOvershoot/UndershootSpecificationforAddressandControlPins:6710.

14.

2ACOvershoot/UndershootSpecificationforClock,Data,StrobeandMaskpins:6711.

TIMINGWAVEFORMS68W9725G6KBPublicationReleaseDate:Sep.

03,2012-3-RevisionA0311.

1CommandInputTiming.

6811.

2ODTTimingforActive/StandbyMode.

6911.

3ODTTimingforPowerDownMode6911.

4ODTTimingmodeswitchatenteringpowerdownmode.

7011.

5ODTTimingmodeswitchatexitingpowerdownmode7111.

6Dataoutput(read)timing7211.

7Burstreadoperation:RL=5(AL=2,CL=3,BL=4)7211.

8Datainput(write)timing7311.

9Burstwriteoperation:RL=5(AL=2,CL=3,WL=4,BL=4)7311.

10Seamlessburstreadoperation:RL=5(AL=2,andCL=3,BL=4)7411.

11Seamlessburstwriteoperation:RL=5(WL=4,BL=4)7411.

12Burstreadinterrupttiming:RL=3(CL=3,AL=0,BL=8)7511.

13Burstwriteinterrupttiming:RL=3(CL=3,AL=0,WL=2,BL=8)7511.

14WriteoperationwithDataMask:WL=3,AL=0,BL=4)7611.

15Burstreadoperationfollowedbyprecharge:RL=4(AL=1,CL=3,BL=4,tRTP≤2clks)7711.

16Burstreadoperationfollowedbyprecharge:RL=4(AL=1,CL=3,BL=8,tRTP≤2clks)7711.

17Burstreadoperationfollowedbyprecharge:RL=5(AL=2,CL=3,BL=4,tRTP≤2clks)7811.

18Burstreadoperationfollowedbyprecharge:RL=6(AL=2,CL=4,BL=4,tRTP≤2clks)7811.

19Burstreadoperationfollowedbyprecharge:RL=4(AL=0,CL=4,BL=8,tRTP>2clks)7911.

20Burstwriteoperationfollowedbyprecharge:WL=(RL-1)=37911.

21Burstwriteoperationfollowedbyprecharge:WL=(RL-1)=48011.

22BurstreadoperationwithAuto-precharge:RL=4(AL=1,CL=3,BL=8,tRTP≤2clks)8011.

23BurstreadoperationwithAuto-precharge:RL=4(AL=1,CL=3,BL=4,tRTP>2clks)8111.

24BurstreadwithAuto-prechargefollowedbyanactivationtothesamebank(tRCLimit):RL=5(AL=2,CL=3,internaltRCD=3,BL=4,tRTP≤2clks)8111.

25BurstreadwithAuto-prechargefollowedbyanactivationtothesamebank(tRPLimit):RL=5(AL=2,CL=3,internaltRCD=3,BL=4,tRTP≤2clks)8211.

26BurstwritewithAuto-precharge(tRCLimit):WL=2,WR=2,BL=4,tRP=3.

8211.

27BurstwritewithAuto-precharge(WR+tRPLimit):WL=4,WR=2,BL=4,tRP=3.

8311.

28SelfRefreshTiming8311.

29ActivePowerDownModeEntryandExitTiming.

8411.

30PrechargedPowerDownModeEntryandExitTiming.

8411.

31ClockfrequencychangeinprechargePowerDownmode8512.

PACKAGESPECIFICATION8613.

REVISIONHISTORY.

87W9725G6KBPublicationReleaseDate:Sep.

03,2012-4-RevisionA031.

GENERALDESCRIPTIONTheW9725G6KBisa256MbitsDDR2SDRAM,organizedas4,194,304words4banks16bits.

Thisdeviceachieveshighspeedtransferratesupto1066Mb/sec/pin(DDR2-1066)forgeneralapplications.

W9725G6KBissortedintothefollowingspeedgrades:-18,-25,25I,25A,25Kand-3.

The-18gradepartsiscomplianttotheDDR2-1066(7-7-7)specification.

The-25/25I/25A/25KgradepartsarecomplianttotheDDR2-800(5-5-5)orDDR2-800(6-6-6)specification(the25Iindustrialgradepartswhichisguaranteedtosupport-40°C≤TCASE≤95°C).

The-3gradepartsiscomplianttotheDDR2-667(5-5-5)specification.

Theautomotivegradepartstemperature,ifoffered,hastwosimultaneousrequirements:ambienttemperature(TA)surroundingthedevicecannotbelessthan-40°Corgreaterthan+95°C(for25A),+105°C(for25K),andthecasetemperature(TCASE)cannotbelessthan-40°Corgreaterthan+95°C(for25A),+105°C(for25K).

JEDECspecificationsrequiretherefreshratetodoublewhenTCASEexceeds+85°C;thisalsorequiresuseofthehigh-temperatureselfrefreshoption.

Additionally,ODTresistanceandtheinput/outputimpedancemustbederatedwhenTCASEis+85°C.

Allofthecontrolandaddressinputsaresynchronizedwithapairofexternallysupplieddifferentialclocks.

Inputsarelatchedatthecrosspointofdifferentialclocks(CLKrisingandfalling).

AllI/OsaresynchronizedwithasingleendedDQSordifferentialDQS-pairinasourcesynchronousfashion.

2.

FEATURESPowerSupply:VDD,VDDQ=1.

8V0.

1VDoubleDataRatearchitecture:twodatatransfersperclockcycleCASLatency:3,4,5,6and7BurstLength:4and8Bi-directional,differentialdatastrobes(DQSand)aretransmitted/receivedwithdataEdge-alignedwithReaddataandcenter-alignedwithWritedataDLLalignsDQandDQStransitionswithclockDifferentialclockinputs(CLKand)Datamasks(DM)forwritedataCommandsenteredoneachpositiveCLKedge,dataanddatamaskarereferencedtobothedgesofDQSPostedprogrammableadditivelatencysupportedtomakecommandanddatabusefficiencyReadLatency=AdditiveLatencyplusCASLatency(RL=AL+CL)Off-Chip-Driverimpedanceadjustment(OCD)andOn-Die-Termination(ODT)forbettersignalqualityAuto-prechargeoperationforreadandwriteburstsAutoRefreshandSelfRefreshmodesPrechargedPowerDownandActivePowerDownWriteDataMaskWriteLatency=ReadLatency-1(WL=RL-1)Interface:SSTL_18PackagedinWBGA84Ball(8X12.

5mm2),usingLeadfreematerialswithRoHScompliantW9725G6KBPublicationReleaseDate:Sep.

03,2012-5-RevisionA033.

ORDERINFORMATIONPARTNUMBERSPEEDGRADEOPERATINGTEMPERATUREW9725G6KB-18DDR2-1066(7-7-7)0°C≤TCASE≤85°CW9725G6KB-25DDR2-800(5-5-5)orDDR2-800(6-6-6)0°C≤TCASE≤85°CW9725G6KB25IDDR2-800(5-5-5)orDDR2-800(6-6-6)-40°C≤TCASE≤95°CW9725G6KB25ADDR2-800(5-5-5)orDDR2-800(6-6-6)-40°C≤TA,TCASE≤95°CW9725G6KB25KDDR2-800(5-5-5)orDDR2-800(6-6-6)-40°C≤TA,TCASE≤105°CW9725G6KB-3DDR2-667(5-5-5)0°C≤TCASE≤85°C4.

KEYPARAMETERSSYM.

SPEEDGRADEDDR2-1066DDR2-800DDR2-667Bin(CL-tRCD-tRP)7-7-75-5-5/6-6-65-5-5PartNumberExtension-18-25/25I/25A/25K-3tCK(avg)Averageclockperiod@CL=7Min.

1.

875nSMax.

7.

5nS@CL=6Min.

2.

5nS2.

5nSMax.

7.

5nS8nS@CL=5Min.

3nS2.

5nS3nSMax.

7.

5nS8nS8nS@CL=4Min.

3.

75nS3.

75nS3.

75nSMax.

7.

5nS8nS8nS@CL=3Min.

5nS5nSMax.

8nS8nStRCDActivetoRead/WriteCommandDelayTimeMin.

13.

125nS12.

5nS15nStREFIAverageperiodicrefreshInterval-40°C≤TCASE≤85°CMax.

*27.

8μS*2,3*20°C≤TCASE≤85°C7.

8μS*17.

8μS*17.

8μS*185°CIdleaftertRPLHHHXNOPNOP->IdleaftertRPLHLHBA,CA,A10READ/READAILLEGAL1LHLLBA,CA,A10WRIT/WRITAILLEGAL1LLHHBA,RAACTILLEGAL1LLHLBA,A10PRE/PREANOP->IdleaftertRP1LLLHXREF/SELFILLEGALLLLLOp-CodeMRS/EMRSILLEGALRowActivatingHXXXXDSLNOP->RowactiveaftertRCDLHHHXNOPNOP->RowactiveaftertRCDLHLHBA,CA,A10READ/READAILLEGAL1LHLLBA,CA,A10WRIT/WRITAILLEGAL1LLHHBA,RAACTILLEGAL1LLHLBA,A10PRE/PREAILLEGAL1LLLHXREF/SELFILLEGALLLLLOp-CodeMRS/EMRSILLEGALW9725G6KBPublicationReleaseDate:Sep.

03,2012-35-RevisionA03FunctionTruthTable,continuedCURRENTSTATEADDRESSCOMMANDACTIONNOTESWriteRecoveringHXXXXDSLNOP->BankactiveaftertWRLHHHXNOPNOP->BankactiveaftertWRLHLHBA,CA,A10READ/READAILLEGAL1LHLLBA,CA,A10WRIT/WRITANewwriteLLHHBA,RAACTILLEGAL1LLHLBA,A10PRE/PREAILLEGAL1LLLHXREF/SELFILLEGALLLLLOp-CodeMRS/EMRSILLEGALWriteRecoveringwithAuto-prechargeHXXXXDSLNOP->PrechargeaftertWRLHHHXNOPNOP->PrechargeaftertWRLHLHBA,CA,A10READ/READAILLEGAL1LHLLBA,CA,A10WRIT/WRITAILLEGAL1LLHHBA,RAACTILLEGAL1LLHLBA,A10PRE/PREAILLEGAL1LLLHXREF/SELFILLEGALLLLLOp-CodeMRS/EMRSILLEGALRefreshingHXXXXDSLNOP->IdleaftertRCLHHHXNOPNOP->IdleaftertRCLHLHBA,CA,A10READ/READAILLEGALLHLLBA,CA,A10WRIT/WRITAILLEGALLLHHBA,RAACTILLEGALLLHLBA,A10PRE/PREAILLEGALLLLHXREF/SELFILLEGALLLLLOp-CodeMRS/EMRSILLEGALModeRegisterAccessingHXXXXDSLNOP->IdleaftertMRDLHHHXNOPNOP->IdleaftertMRDLHLHBA,CA,A10READ/READAILLEGALLHLLBA,CA,A10WRIT/WRITAILLEGALLLHHBA,RAACTILLEGALLLHLBA,A10PRE/PREAILLEGALLLLHXREF/SELFILLEGALLLLLOp-CodeMRS/EMRSILLEGALNotes:1.

Thiscommandmaybeissuedforotherbanks,dependingonthestateofthebanks.

2.

Allbanksmustbein"IDLE".

3.

ReadorWriteburstinterruptionisprohibitedforburstlengthof4andonlyallowedforburstlengthof8.

Burstread/writecanonlybeinterruptedbyanotherread/writewith4bitburstboundary.

Anyothercaseofread/writeinterruptisnotallowed.

Remark:H=Highlevel,L=Lowlevel,X=HighorLowlevel(DontCare),V=Validdata.

W9725G6KBPublicationReleaseDate:Sep.

03,2012-36-RevisionA039.

5SimplifiedStatedDiagramW9725G6KBPublicationReleaseDate:Sep.

03,2012-37-RevisionA0310.

ELECTRICALCHARACTERISTICS10.

1AbsoluteMaximumRatingsPARAMETERSYMBOLRATINGUNITNOTESVoltageonVDDpinrelativetoVSSVDD-1.

0~2.

3V1,2VoltageonVDDQpinrelativetoVSSVDDQ-0.

5~2.

3V1,2VoltageonVDDLpinrelativetoVSSVDDL-0.

5~2.

3V1,2VoltageonanypinrelativetoVSSVIN,VOUT-0.

5~2.

3V1,2StorageTemperatureTSTG-55~150°C1,3Notes:1.

Stressesgreaterthanthoselistedunder"AbsoluteMaximumRatings"maycausepermanentdamagetothedevice.

Thisisastressratingonlyandfunctionaloperationofthedeviceattheseoranyotherconditionsabovethoseindicatedintheoperationalsectionsofthisspecificationisnotimplied.

Exposuretoabsolutemaximumratingconditionsforextendedperiodsmayaffectreliability.

2.

WhenVDDandVDDQandVDDLarelessthan500mV;VREFmaybeequaltoorlessthan300mV.

3.

Storagetemperatureisthecasesurfacetemperatureonthecenter/topsideoftheDRAM.

10.

2OperatingTemperatureConditionPARAMETERSYMBOLMIN.

MAX.

UNITNOTESOperatingTemperature(for-18/-25/-3)TCASE085°C1,3,5OperatingTemperature(for25I/25A)TCASE-4095°C1,3,4,5,6,7OperatingTemperature(for25A)TA-4095°C2OperatingTemperature(for25K)TCASE-40105°C1,3,4,5,6,8OperatingTemperature(for25K)TA-40105°C2Notes:1.

Operatingcasetemperatureisthecasesurfacetemperatureonthecenter/topsideoftheDRAM.

2.

OperatingambienttemperatureisthesurroundingtemperatureoftheDRAM.

3.

Supporting0°C≤TCASE≤85°CwithfullJEDECACandDCspecifications.

4.

Supporting-40°C≤TCASE≤85°CwithfullJEDECACandDCspecifications.

5.

Supporting0~85°Candbeingabletoextendto95°CwithdoublingAutoRefreshcommandsinfrequencytoa32mSperiod(tREFI=3.

9S)andtoentertoSelfRefreshmodeatthishightemperaturerangeviaA7"1"onEMR(2).

6.

Supporting-40°C≤TCASE≤85°Candbeingabletoextendto95°C(for25I/25A)or105°C(for25K)withdoublingAutoRefreshcommandsinfrequencytoa32mSperiod(tREFI=3.

9S)andtoentertoSelfRefreshmodeatthishightemperaturerangeviaA7"1"onEMR(2).

7.

Duringoperation,theDRAMcasetemperaturemustbemaintainedbetween-40to95°Cfor25I/25Apartsunderallspecificationparameters.

8.

Duringoperation,theDRAMcasetemperaturemustbemaintainedbetween-40to105°Cfor25Kpartsunderallspecificationparameters.

W9725G6KBPublicationReleaseDate:Sep.

03,2012-38-RevisionA0310.

3RecommendedDCOperatingConditionsSYM.

PARAMETERMIN.

TYP.

MAX.

UNITNOTESVDDSupplyVoltage1.

71.

81.

9V1VDDLSupplyVoltageforDLL1.

71.

81.

9V5VDDQSupplyVoltageforOutput1.

71.

81.

9V1,5VREFInputReferenceVoltage0.

49xVDDQ0.

5xVDDQ0.

51xVDDQV2,3VTTTerminationVoltage(System)VREF-0.

04VREFVREF+0.

04V4Notes:1.

ThereisnospecificdeviceVDDsupplyvoltagerequirementforSSTL_18compliance.

HoweverunderallconditionsVDDQmustthanorequaltoVDD.

2.

ThevalueofVREFmaybeselectedbytheusertoprovideoptimumnoisemargininthesystem.

TypicallythevalueofVREFisexpectedtobeabout0.

5xVDDQofthetransmittingdeviceandVREFisexpectedtotrackvariationsinVDDQ.

3.

PeaktopeakACnoiseonVREFmaynotexceed2%VREF(dc).

4.

VTToftransmittingdevicemusttrackVREFofreceivingdevice.

5.

VDDQtrackswithVDD,VDDLtrackswithVDD.

ACparametersaremeasuredwithVDD,VDDQandVDDDLtiedtogether.

10.

4ODTDCElectricalCharacteristicsPARAMETER/CONDITIONSYM.

MIN.

NOM.

MAX.

UNITNOTESRtteffectiveimpedancevalueforEMRS(A6,A2)=0,1;75ΩRtt1(eff)607590Ω1RtteffectiveimpedancevalueforEMRS(A6,A2)=1,0;150ΩRtt2(eff)120150180Ω1RtteffectiveimpedancevalueforEMRS(A6,A2)=1,1;50ΩRtt3(eff)405060Ω1,2DeviationofVMwithrespecttoVDDQ/2ΔVM-6+6%1Notes:1.

TestconditionforRttmeasurements.

2.

OptionalforDDR2-667,mandatoryforDDR2-800andDDR2-1066.

MeasurementDefinitionforRtt(eff):ApplyVIH(ac)andVIL(ac)totestpinseparately,thenmeasurecurrentI(VIH(ac))andI(VIL(ac))respectively.

VIH(ac),VIL(ac),andVDDQvaluesdefinedinSSTL_18.

Rtt(eff)=(VIH(ac)–VIL(ac))/(I(VIHac)–I(VILac))MeasurementDefinitionforΔVM:Measurevoltage(VM)attestpin(midpoint)withnoload.

ΔVM=((2xVm/VDDQ)–1)x100%10.

5InputDCLogicLevelPARAMETERSYM.

MIN.

MAX.

UNITDCinputlogicHIGHVIH(dc)VREF+0.

125VDDQ+0.

3VDCinputlogicLOWVIL(dc)-0.

3VREF-0.

125V10.

6InputACLogicLevelPARAMETERSYM.

-18-25/25I/25A/25K/-3UNITMIN.

MAX.

MIN.

MAX.

ACinputlogicHIGHVIH(ac)VREF+0.

200VREF+0.

200VDDQ+VPEAK1VACinputlogicLOWVIL(ac)VREF-0.

200VSSQ-VPEAK1VREF-0.

200VNote:1.

Refertothepage67sections10.

14.

1and10.

14.

2ACOvershoot/UndershootspecificationtableforVPEAKvalue:maximumpeakamplitudeallowedforOvershoot/Undershoot.

W9725G6KBPublicationReleaseDate:Sep.

03,2012-39-RevisionA0310.

7CapacitanceSYM.

PARAMETERMIN.

MAX.

UNITCCKInputCapacitance,CLKand1.

02.

0pFCDCKInputCapacitancedelta,CLKand0.

25pFCIinputCapacitance,allotherinput-onlypins1.

01.

75pFCDIInputCapacitancedelta,allotherinput-onlypins0.

25pFCIOInput/outputCapacitance,DQ,LDM,UDM,LDQS,,UDQS,2.

53.

5pFCDIOInput/outputCapacitancedelta,DQ,LDM,UDM,LDQS,,UDQS,0.

5pF10.

8LeakageandOutputBufferCharacteristicsSYM.

PARAMETERMIN.

MAX.

UNITNOTESIILInputLeakageCurrent(0V≤VIN≤VDD)-22A1IOLOutputLeakageCurrent(Outputdisabled,0V≤VOUT≤VDDQ)-55A2VOHMinimumRequiredOutputPull-upVTT+0.

603VVOLMaximumRequiredOutputPull-downVTT-0.

603VVOTROutputTimingMeasurementReferenceLevel0.

5xVDDQV3IOH(dc)OutputMinimumSourceDCCurrent-13.

4mA4,6IOL(dc)OutputMinimumSinkDCCurrent13.

4mA5,6Notes:1.

Allotherpinsnotundertest=0V.

2.

DQ,LDQS,,UDQS,aredisabledandODTisturnedoff.

3.

TheVDDQofthedeviceundertestisreferenced.

4.

VDDQ=1.

7V;VOUT=1.

42V.

(VOUT-VDDQ)/IOHmustbelessthan21ΩforvaluesofVOUTbetweenVDDQandVDDQ-0.

28V.

5.

VDDQ=1.

7V;VOUT=0.

28V.

VOUT/IOLmustbelessthan21ΩforvaluesofVOUTbetween0Vand0.

28V.

6.

ThevaluesofIOH(dc)andIOL(dc)arebasedontheconditionsgiveninNotes3and4.

TheyareusedtotestdrivecurrentcapabilitytoensureVIHminplusanoisemarginandVILmaxminusanoisemarginaredeliveredtoanSSTL_18receiver.

W9725G6KBPublicationReleaseDate:Sep.

03,2012-40-RevisionA0310.

9DCCharacteristicsSYM.

CONDITIONS-18-25/25I/25A/25K-3UNITNOTESMAX.

MAX.

MAX.

IDD0OperatingCurrent-OneBankActive-PrechargetCK=tCK(IDD),tRC=tRC(IDD),tRAS=tRASmin(IDD);CKEisHIGH,isHIGHbetweenvalidcommands;AddressandcontrolinputsareSWITCHING;DatabusinputsareSWITCHING.

706055mA1,2,3,4,5,6IDD1OperatingCurrent-OneBankActive-Read-PrechargeIOUT=0mA;BL=4,CL=CL(IDD),AL=0;tCK=tCK(IDD),tRC=tRC(IDD),tRAS=tRASmin(IDD),tRCD=tRCD(IDD);CKEisHIGH,isHIGHbetweenvalidcommands;AddressandcontrolinputsareSWITCHING;DatabusinputsareSWITCHING.

807065mA1,2,3,4,5,6IDD2PPrechargePower-DownCurrentAllbanksidle;tCK=tCK(IDD);CKEisLOW;OthercontrolandaddressinputsareSTABLE;DataBusinputsareFLOATING.

(TCASE≤85°C)666mA1,2,3,4,5,6,7IDD2NPrechargeStandbyCurrentAllbanksidle;tCK=tCK(IDD);CKEisHIGH,isHIGH;OthercontrolandaddressinputsareSWITCHING;DatabusinputsareSWITCHING.

454035mA1,2,3,4,5,6IDD2QPrechargeQuietStandbyCurrentAllbanksidle;tCK=tCK(IDD);CKEisHIGH,isHIGH;OthercontrolandaddressinputsareSTABLE;DatabusinputsareFLOATING.

353530mA1,2,3,4,5,6IDD3PFActivePower-DownCurrentAllbanksopen;tCK=tCK(IDD);CKEisLOW;OthercontrolandaddressinputsareSTABLE;DatabusinputsareFLOATING.

(TCASE≤85°C)FastPDNExitMRS(12)=0151515mA1,2,3,4,5,6IDD3PSSlowPDNExitMRS(12)=1101010mA1,2,3,4,5,6,7IDD3NActiveStandbyCurrentAllbanksopen;tCK=tCK(IDD);tRAS=tRASmax(IDD),tRP=tRP(IDD);CKEisHIGH,isHIGHbetweenvalidcommands;OthercontrolandaddressinputsareSWITCHING;DatabusinputsareSWITCHING.

605045mA1,2,3,4,5,6W9725G6KBPublicationReleaseDate:Sep.

03,2012-41-RevisionA03IDD4ROperatingBurstReadCurrentAllbanksopen,Continuousburstreads,IOUT=0mA;BL=4,CL=CL(IDD),AL=0;tCK=tCK(IDD);tRAS=tRASmax(IDD),tRP=tRP(IDD);CKEisHIGH,isHIGHbetweenvalidcommands;AddressinputsareSWITCHING;DataBusinputsareSWITCHING.

12510595mA1,2,3,4,5,6IDD4WOperatingBurstWriteCurrentAllbanksopen,Continuousburstwrites;BL=4,CL=CL(IDD),AL=0;tCK=tCK(IDD);tRAS=tRASmax(IDD),tRP=tRP(IDD);CKEisHIGH,isHIGHbetweenvalidcommands;AddressinputsareSWITCHING;DataBusinputsareSWITCHING.

130110100mA1,2,3,4,5,6IDD5BBurstRefreshCurrenttCK=tCK(IDD);RefreshcommandeverytRFC(IDD)interval;CKEisHIGH,isHIGHbetweenvalidcommands;OthercontrolandaddressinputsareSWITCHING;DatabusinputsareSWITCHING.

757065mA1,2,3,4,5,6IDD6SelfRefreshCurrentCKE≤0.

2V,externalclockoff,CLKandat0V;OthercontrolandaddressinputsareFLOATING;DatabusinputsareFLOATING.

(TCASE≤85°C)666mA1,2,3,4,5,6,7IDD7OperatingBankInterleaveReadCurrentAllbankinterleavingreads,IOUT=0mA;BL=4,CL=CL(IDD),AL=tRCD(IDD)-1xtCK(IDD);tCK=tCK(IDD),tRC=tRC(IDD),tRRD=tRRD(IDD),tFAW=tFAW(IDD),tRCD=tRCD(IDD);CKEisHIGH,isHIGHbetweenvalidcommands;AddressbusinputsareSTABLEduringdeselects;DataBusinputsareSWITCHING.

160135115mA1,2,3,4,5,6Notes:1.

VDD=1.

8V0.

1V;VDDQ=1.

8V0.

1V.

2.

IDDspecificationsaretestedafterthedeviceisproperlyinitialized.

3.

InputslewrateisspecifiedbyACParametricTestCondition.

4.

IDDparametersarespecifiedwithODTdisabled.

5.

DataBusconsistsofDQ,LDM,UDM,LDQS,,UDQSand.

6.

DefinitionsforIDDLOW=Vin≤VIL(ac)(max)HIGH=Vin≥VIH(ac)(min)STABLE=inputsstableataHIGHorLOWlevelFLOATING=inputsatVREF=VDDQ/2SWITCHING=inputschangingbetweenHIGHandLOWeveryotherclockcycle(oncepertwoclocks)foraddressandcontrolsignals,andinputschangingbetweenHIGHandLOWeveryotherdatatransfer(onceperclock)forDQsignalsnotincludingmasksorstrobes.

7.

ThefollowingIDDvaluesmustbederated(IDDlimitsincrease),whenTCASE≥85°CIDD2Pmustbederatedby20%;IDD3P(slow)mustbederatedby30%andIDD6mustbederatedby80%.

(IDD6willincreasebythisamountifTCASE2clks)11.

20Burstwriteoperationfollowedbyprecharge:WL=(RL-1)=3W9725G6KBPublicationReleaseDate:Sep.

03,2012-80-RevisionA0311.

21Burstwriteoperationfollowedbyprecharge:WL=(RL-1)=411.

22BurstreadoperationwithAuto-precharge:RL=4(AL=1,CL=3,BL=8,tRTP≤2clks)W9725G6KBPublicationReleaseDate:Sep.

03,2012-81-RevisionA0311.

23BurstreadoperationwithAuto-precharge:RL=4(AL=1,CL=3,BL=4,tRTP>2clks)11.

24BurstreadwithAuto-prechargefollowedbyanactivationtothesamebank(tRCLimit):RL=5(AL=2,CL=3,internaltRCD=3,BL=4,tRTP≤2clks)W9725G6KBPublicationReleaseDate:Sep.

03,2012-82-RevisionA0311.

25BurstreadwithAuto-prechargefollowedbyanactivationtothesamebank(tRPLimit):RL=5(AL=2,CL=3,internaltRCD=3,BL=4,tRTP≤2clks)11.

26BurstwritewithAuto-precharge(tRCLimit):WL=2,WR=2,BL=4,tRP=3W9725G6KBPublicationReleaseDate:Sep.

03,2012-83-RevisionA0311.

27BurstwritewithAuto-precharge(WR+tRPLimit):WL=4,WR=2,BL=4,tRP=311.

28SelfRefreshTimingNotes:1.

Devicemustbeinthe"Allbanksidle"statepriortoenteringSelfRefreshmode.

2.

ODTmustbeturnedofftAOFDbeforeenteringSelfRefreshmode,andcanbeturnedonagainwhentXSRDtimingissatisfied.

3.

tXSRDisappliedforaReadoraReadwithAuto-prechargecommand.

tXSNRisappliedforanycommandexceptaReadoraReadwithAuto-prechargecommand.

W9725G6KBPublicationReleaseDate:Sep.

03,2012-84-RevisionA0311.

29ActivePowerDownModeEntryandExitTiming11.

30PrechargedPowerDownModeEntryandExitTimingW9725G6KBPublicationReleaseDate:Sep.

03,2012-85-RevisionA0311.

31ClockfrequencychangeinprechargePowerDownmodeW9725G6KBPublicationReleaseDate:Sep.

03,2012-86-RevisionA0312.

PACKAGESPECIFICATIONPackageOutlineWBGA-84(8x12.

5mm2)W9725G6KBPublicationReleaseDate:Sep.

03,2012-87-RevisionA0313.

REVISIONHISTORYVERSIONDATEPAGEDESCRIPTIONA01Apr.

25,2012AllInitialformaldatasheetA02Jul.

06,20124,5,13,37,38,40~42,45,46Added25Aand25KautomotivegradepartsA03Sep.

03,20129AddedVTTvoltageramptimerequiredconditioninsection8.

1power-upandinitializationsequence83Addednotesfor11.

28selfrefreshtimingdiagram86Added"ddd"and"eee"symbolsinWBGA84packageoutlinedrawingdiagramImportantNoticeWinbondproductsarenotdesigned,intended,authorizedorwarrantedforuseascomponentsinsystemsorequipmentintendedforsurgicalimplantation,atomicenergycontrolinstruments,airplaneorspaceshipinstruments,transportationinstruments,trafficsignalinstruments,combustioncontrolinstruments,orforotherapplicationsintendedtosupportorsustainlife.

Furthermore,WinbondproductsarenotintendedforapplicationswhereinfailureofWinbondproductscouldresultorleadtoasituationwhereinpersonalinjury,deathorseverepropertyorenvironmentaldamagecouldoccur.

WinbondcustomersusingorsellingtheseproductsforuseinsuchapplicationsdosoattheirownriskandagreetofullyindemnifyWinbondforanydamagesresultingfromsuchimproperuseorsales.

03,2012-1-RevisionA03TableofContents-1.

GENERALDESCRIPTION42.

FEATURES.

43.

ORDERINFORMATION54.

KEYPARAMETERS55.

BALLCONFIGURATION66.

BALLDESCRIPTION.

77.

BLOCKDIAGRAM88.

FUNCTIONALDESCRIPTION.

98.

1Power-upandInitializationSequence.

98.

2ModeRegisterandExtendedModeRegistersOperation108.

2.

1ModeRegisterSetCommand(MRS)108.

2.

2ExtendModeRegisterSetCommands(EMRS)118.

2.

2.

1ExtendModeRegisterSetCommand(1),EMR(1)118.

2.

2.

2DLLEnable/Disable.

128.

2.

2.

3ExtendModeRegisterSetCommand(2),EMR(2)138.

2.

2.

4ExtendModeRegisterSetCommand(3),EMR(3)148.

2.

3Off-ChipDriver(OCD)ImpedanceAdjustment158.

2.

3.

1ExtendedModeRegisterforOCDImpedanceAdjustment168.

2.

3.

2OCDImpedanceAdjust.

168.

2.

3.

3DriveMode178.

2.

4On-DieTermination(ODT)188.

2.

5ODTrelatedtimings188.

2.

5.

1MRScommandtoODTupdatedelay.

188.

3CommandFunction.

208.

3.

1BankActivateCommand.

208.

3.

2ReadCommand.

208.

3.

3WriteCommand218.

3.

4BurstReadwithAuto-prechargeCommand.

218.

3.

5BurstWritewithAuto-prechargeCommand.

218.

3.

6PrechargeAllCommand218.

3.

7SelfRefreshEntryCommand218.

3.

8SelfRefreshExitCommand.

228.

3.

9RefreshCommand.

228.

3.

10No-OperationCommand.

238.

3.

11DeviceDeselectCommand.

238.

4ReadandWriteaccessmodes238.

4.

1Posted23W9725G6KBPublicationReleaseDate:Sep.

03,2012-2-RevisionA038.

4.

1.

1Examplesofpostedoperation.

238.

4.

2Burstmodeoperation.

248.

4.

3Burstreadmodeoperation.

258.

4.

4Burstwritemodeoperation258.

4.

5Writedatamask268.

5BurstInterrupt268.

6Prechargeoperation.

278.

6.

1Burstreadoperationfollowedbyprecharge.

278.

6.

2Burstwriteoperationfollowedbyprecharge278.

7Auto-prechargeoperation278.

7.

1BurstreadwithAuto-precharge.

288.

7.

2BurstwritewithAuto-precharge288.

8RefreshOperation.

298.

9PowerDownMode.

298.

9.

1PowerDownEntry308.

9.

2PowerDownExit.

308.

10Inputclockfrequencychangeduringprechargepowerdown309.

OPERATIONMODE319.

1CommandTruthTable319.

2ClockEnable(CKE)TruthTableforSynchronousTransitions.

329.

3DataMask(DM)TruthTable.

329.

4FunctionTruthTable.

339.

5SimplifiedStatedDiagram.

3610.

ELECTRICALCHARACTERISTICS3710.

1AbsoluteMaximumRatings.

3710.

2OperatingTemperatureCondition.

3710.

3RecommendedDCOperatingConditions3810.

4ODTDCElectricalCharacteristics3810.

5InputDCLogicLevel.

3810.

6InputACLogicLevel.

3810.

7Capacitance3910.

8LeakageandOutputBufferCharacteristics3910.

9DCCharacteristics4010.

10IDDMeasurementTestParameters4210.

11ACCharacteristics.

4310.

11.

1ACCharacteristicsandOperatingConditionfor-18speedgrade4310.

11.

2ACCharacteristicsandOperatingConditionfor-25/25I/25A/25K/-3speedgrade.

4510.

12ACInputTestConditions.

6610.

13DifferentialInput/OutputACLogicLevels.

6610.

14ACOvershoot/UndershootSpecification6710.

14.

1ACOvershoot/UndershootSpecificationforAddressandControlPins:6710.

14.

2ACOvershoot/UndershootSpecificationforClock,Data,StrobeandMaskpins:6711.

TIMINGWAVEFORMS68W9725G6KBPublicationReleaseDate:Sep.

03,2012-3-RevisionA0311.

1CommandInputTiming.

6811.

2ODTTimingforActive/StandbyMode.

6911.

3ODTTimingforPowerDownMode6911.

4ODTTimingmodeswitchatenteringpowerdownmode.

7011.

5ODTTimingmodeswitchatexitingpowerdownmode7111.

6Dataoutput(read)timing7211.

7Burstreadoperation:RL=5(AL=2,CL=3,BL=4)7211.

8Datainput(write)timing7311.

9Burstwriteoperation:RL=5(AL=2,CL=3,WL=4,BL=4)7311.

10Seamlessburstreadoperation:RL=5(AL=2,andCL=3,BL=4)7411.

11Seamlessburstwriteoperation:RL=5(WL=4,BL=4)7411.

12Burstreadinterrupttiming:RL=3(CL=3,AL=0,BL=8)7511.

13Burstwriteinterrupttiming:RL=3(CL=3,AL=0,WL=2,BL=8)7511.

14WriteoperationwithDataMask:WL=3,AL=0,BL=4)7611.

15Burstreadoperationfollowedbyprecharge:RL=4(AL=1,CL=3,BL=4,tRTP≤2clks)7711.

16Burstreadoperationfollowedbyprecharge:RL=4(AL=1,CL=3,BL=8,tRTP≤2clks)7711.

17Burstreadoperationfollowedbyprecharge:RL=5(AL=2,CL=3,BL=4,tRTP≤2clks)7811.

18Burstreadoperationfollowedbyprecharge:RL=6(AL=2,CL=4,BL=4,tRTP≤2clks)7811.

19Burstreadoperationfollowedbyprecharge:RL=4(AL=0,CL=4,BL=8,tRTP>2clks)7911.

20Burstwriteoperationfollowedbyprecharge:WL=(RL-1)=37911.

21Burstwriteoperationfollowedbyprecharge:WL=(RL-1)=48011.

22BurstreadoperationwithAuto-precharge:RL=4(AL=1,CL=3,BL=8,tRTP≤2clks)8011.

23BurstreadoperationwithAuto-precharge:RL=4(AL=1,CL=3,BL=4,tRTP>2clks)8111.

24BurstreadwithAuto-prechargefollowedbyanactivationtothesamebank(tRCLimit):RL=5(AL=2,CL=3,internaltRCD=3,BL=4,tRTP≤2clks)8111.

25BurstreadwithAuto-prechargefollowedbyanactivationtothesamebank(tRPLimit):RL=5(AL=2,CL=3,internaltRCD=3,BL=4,tRTP≤2clks)8211.

26BurstwritewithAuto-precharge(tRCLimit):WL=2,WR=2,BL=4,tRP=3.

8211.

27BurstwritewithAuto-precharge(WR+tRPLimit):WL=4,WR=2,BL=4,tRP=3.

8311.

28SelfRefreshTiming8311.

29ActivePowerDownModeEntryandExitTiming.

8411.

30PrechargedPowerDownModeEntryandExitTiming.

8411.

31ClockfrequencychangeinprechargePowerDownmode8512.

PACKAGESPECIFICATION8613.

REVISIONHISTORY.

87W9725G6KBPublicationReleaseDate:Sep.

03,2012-4-RevisionA031.

GENERALDESCRIPTIONTheW9725G6KBisa256MbitsDDR2SDRAM,organizedas4,194,304words4banks16bits.

Thisdeviceachieveshighspeedtransferratesupto1066Mb/sec/pin(DDR2-1066)forgeneralapplications.

W9725G6KBissortedintothefollowingspeedgrades:-18,-25,25I,25A,25Kand-3.

The-18gradepartsiscomplianttotheDDR2-1066(7-7-7)specification.

The-25/25I/25A/25KgradepartsarecomplianttotheDDR2-800(5-5-5)orDDR2-800(6-6-6)specification(the25Iindustrialgradepartswhichisguaranteedtosupport-40°C≤TCASE≤95°C).

The-3gradepartsiscomplianttotheDDR2-667(5-5-5)specification.

Theautomotivegradepartstemperature,ifoffered,hastwosimultaneousrequirements:ambienttemperature(TA)surroundingthedevicecannotbelessthan-40°Corgreaterthan+95°C(for25A),+105°C(for25K),andthecasetemperature(TCASE)cannotbelessthan-40°Corgreaterthan+95°C(for25A),+105°C(for25K).

JEDECspecificationsrequiretherefreshratetodoublewhenTCASEexceeds+85°C;thisalsorequiresuseofthehigh-temperatureselfrefreshoption.

Additionally,ODTresistanceandtheinput/outputimpedancemustbederatedwhenTCASEis+85°C.

Allofthecontrolandaddressinputsaresynchronizedwithapairofexternallysupplieddifferentialclocks.

Inputsarelatchedatthecrosspointofdifferentialclocks(CLKrisingandfalling).

AllI/OsaresynchronizedwithasingleendedDQSordifferentialDQS-pairinasourcesynchronousfashion.

2.

FEATURESPowerSupply:VDD,VDDQ=1.

8V0.

1VDoubleDataRatearchitecture:twodatatransfersperclockcycleCASLatency:3,4,5,6and7BurstLength:4and8Bi-directional,differentialdatastrobes(DQSand)aretransmitted/receivedwithdataEdge-alignedwithReaddataandcenter-alignedwithWritedataDLLalignsDQandDQStransitionswithclockDifferentialclockinputs(CLKand)Datamasks(DM)forwritedataCommandsenteredoneachpositiveCLKedge,dataanddatamaskarereferencedtobothedgesofDQSPostedprogrammableadditivelatencysupportedtomakecommandanddatabusefficiencyReadLatency=AdditiveLatencyplusCASLatency(RL=AL+CL)Off-Chip-Driverimpedanceadjustment(OCD)andOn-Die-Termination(ODT)forbettersignalqualityAuto-prechargeoperationforreadandwriteburstsAutoRefreshandSelfRefreshmodesPrechargedPowerDownandActivePowerDownWriteDataMaskWriteLatency=ReadLatency-1(WL=RL-1)Interface:SSTL_18PackagedinWBGA84Ball(8X12.

5mm2),usingLeadfreematerialswithRoHScompliantW9725G6KBPublicationReleaseDate:Sep.

03,2012-5-RevisionA033.

ORDERINFORMATIONPARTNUMBERSPEEDGRADEOPERATINGTEMPERATUREW9725G6KB-18DDR2-1066(7-7-7)0°C≤TCASE≤85°CW9725G6KB-25DDR2-800(5-5-5)orDDR2-800(6-6-6)0°C≤TCASE≤85°CW9725G6KB25IDDR2-800(5-5-5)orDDR2-800(6-6-6)-40°C≤TCASE≤95°CW9725G6KB25ADDR2-800(5-5-5)orDDR2-800(6-6-6)-40°C≤TA,TCASE≤95°CW9725G6KB25KDDR2-800(5-5-5)orDDR2-800(6-6-6)-40°C≤TA,TCASE≤105°CW9725G6KB-3DDR2-667(5-5-5)0°C≤TCASE≤85°C4.

KEYPARAMETERSSYM.

SPEEDGRADEDDR2-1066DDR2-800DDR2-667Bin(CL-tRCD-tRP)7-7-75-5-5/6-6-65-5-5PartNumberExtension-18-25/25I/25A/25K-3tCK(avg)Averageclockperiod@CL=7Min.

1.

875nSMax.

7.

5nS@CL=6Min.

2.

5nS2.

5nSMax.

7.

5nS8nS@CL=5Min.

3nS2.

5nS3nSMax.

7.

5nS8nS8nS@CL=4Min.

3.

75nS3.

75nS3.

75nSMax.

7.

5nS8nS8nS@CL=3Min.

5nS5nSMax.

8nS8nStRCDActivetoRead/WriteCommandDelayTimeMin.

13.

125nS12.

5nS15nStREFIAverageperiodicrefreshInterval-40°C≤TCASE≤85°CMax.

*27.

8μS*2,3*20°C≤TCASE≤85°C7.

8μS*17.

8μS*17.

8μS*185°CIdleaftertRPLHHHXNOPNOP->IdleaftertRPLHLHBA,CA,A10READ/READAILLEGAL1LHLLBA,CA,A10WRIT/WRITAILLEGAL1LLHHBA,RAACTILLEGAL1LLHLBA,A10PRE/PREANOP->IdleaftertRP1LLLHXREF/SELFILLEGALLLLLOp-CodeMRS/EMRSILLEGALRowActivatingHXXXXDSLNOP->RowactiveaftertRCDLHHHXNOPNOP->RowactiveaftertRCDLHLHBA,CA,A10READ/READAILLEGAL1LHLLBA,CA,A10WRIT/WRITAILLEGAL1LLHHBA,RAACTILLEGAL1LLHLBA,A10PRE/PREAILLEGAL1LLLHXREF/SELFILLEGALLLLLOp-CodeMRS/EMRSILLEGALW9725G6KBPublicationReleaseDate:Sep.

03,2012-35-RevisionA03FunctionTruthTable,continuedCURRENTSTATEADDRESSCOMMANDACTIONNOTESWriteRecoveringHXXXXDSLNOP->BankactiveaftertWRLHHHXNOPNOP->BankactiveaftertWRLHLHBA,CA,A10READ/READAILLEGAL1LHLLBA,CA,A10WRIT/WRITANewwriteLLHHBA,RAACTILLEGAL1LLHLBA,A10PRE/PREAILLEGAL1LLLHXREF/SELFILLEGALLLLLOp-CodeMRS/EMRSILLEGALWriteRecoveringwithAuto-prechargeHXXXXDSLNOP->PrechargeaftertWRLHHHXNOPNOP->PrechargeaftertWRLHLHBA,CA,A10READ/READAILLEGAL1LHLLBA,CA,A10WRIT/WRITAILLEGAL1LLHHBA,RAACTILLEGAL1LLHLBA,A10PRE/PREAILLEGAL1LLLHXREF/SELFILLEGALLLLLOp-CodeMRS/EMRSILLEGALRefreshingHXXXXDSLNOP->IdleaftertRCLHHHXNOPNOP->IdleaftertRCLHLHBA,CA,A10READ/READAILLEGALLHLLBA,CA,A10WRIT/WRITAILLEGALLLHHBA,RAACTILLEGALLLHLBA,A10PRE/PREAILLEGALLLLHXREF/SELFILLEGALLLLLOp-CodeMRS/EMRSILLEGALModeRegisterAccessingHXXXXDSLNOP->IdleaftertMRDLHHHXNOPNOP->IdleaftertMRDLHLHBA,CA,A10READ/READAILLEGALLHLLBA,CA,A10WRIT/WRITAILLEGALLLHHBA,RAACTILLEGALLLHLBA,A10PRE/PREAILLEGALLLLHXREF/SELFILLEGALLLLLOp-CodeMRS/EMRSILLEGALNotes:1.

Thiscommandmaybeissuedforotherbanks,dependingonthestateofthebanks.

2.

Allbanksmustbein"IDLE".

3.

ReadorWriteburstinterruptionisprohibitedforburstlengthof4andonlyallowedforburstlengthof8.

Burstread/writecanonlybeinterruptedbyanotherread/writewith4bitburstboundary.

Anyothercaseofread/writeinterruptisnotallowed.

Remark:H=Highlevel,L=Lowlevel,X=HighorLowlevel(DontCare),V=Validdata.

W9725G6KBPublicationReleaseDate:Sep.

03,2012-36-RevisionA039.

5SimplifiedStatedDiagramW9725G6KBPublicationReleaseDate:Sep.

03,2012-37-RevisionA0310.

ELECTRICALCHARACTERISTICS10.

1AbsoluteMaximumRatingsPARAMETERSYMBOLRATINGUNITNOTESVoltageonVDDpinrelativetoVSSVDD-1.

0~2.

3V1,2VoltageonVDDQpinrelativetoVSSVDDQ-0.

5~2.

3V1,2VoltageonVDDLpinrelativetoVSSVDDL-0.

5~2.

3V1,2VoltageonanypinrelativetoVSSVIN,VOUT-0.

5~2.

3V1,2StorageTemperatureTSTG-55~150°C1,3Notes:1.

Stressesgreaterthanthoselistedunder"AbsoluteMaximumRatings"maycausepermanentdamagetothedevice.

Thisisastressratingonlyandfunctionaloperationofthedeviceattheseoranyotherconditionsabovethoseindicatedintheoperationalsectionsofthisspecificationisnotimplied.

Exposuretoabsolutemaximumratingconditionsforextendedperiodsmayaffectreliability.

2.

WhenVDDandVDDQandVDDLarelessthan500mV;VREFmaybeequaltoorlessthan300mV.

3.

Storagetemperatureisthecasesurfacetemperatureonthecenter/topsideoftheDRAM.

10.

2OperatingTemperatureConditionPARAMETERSYMBOLMIN.

MAX.

UNITNOTESOperatingTemperature(for-18/-25/-3)TCASE085°C1,3,5OperatingTemperature(for25I/25A)TCASE-4095°C1,3,4,5,6,7OperatingTemperature(for25A)TA-4095°C2OperatingTemperature(for25K)TCASE-40105°C1,3,4,5,6,8OperatingTemperature(for25K)TA-40105°C2Notes:1.

Operatingcasetemperatureisthecasesurfacetemperatureonthecenter/topsideoftheDRAM.

2.

OperatingambienttemperatureisthesurroundingtemperatureoftheDRAM.

3.

Supporting0°C≤TCASE≤85°CwithfullJEDECACandDCspecifications.

4.

Supporting-40°C≤TCASE≤85°CwithfullJEDECACandDCspecifications.

5.

Supporting0~85°Candbeingabletoextendto95°CwithdoublingAutoRefreshcommandsinfrequencytoa32mSperiod(tREFI=3.

9S)andtoentertoSelfRefreshmodeatthishightemperaturerangeviaA7"1"onEMR(2).

6.

Supporting-40°C≤TCASE≤85°Candbeingabletoextendto95°C(for25I/25A)or105°C(for25K)withdoublingAutoRefreshcommandsinfrequencytoa32mSperiod(tREFI=3.

9S)andtoentertoSelfRefreshmodeatthishightemperaturerangeviaA7"1"onEMR(2).

7.

Duringoperation,theDRAMcasetemperaturemustbemaintainedbetween-40to95°Cfor25I/25Apartsunderallspecificationparameters.

8.

Duringoperation,theDRAMcasetemperaturemustbemaintainedbetween-40to105°Cfor25Kpartsunderallspecificationparameters.

W9725G6KBPublicationReleaseDate:Sep.

03,2012-38-RevisionA0310.

3RecommendedDCOperatingConditionsSYM.

PARAMETERMIN.

TYP.

MAX.

UNITNOTESVDDSupplyVoltage1.

71.

81.

9V1VDDLSupplyVoltageforDLL1.

71.

81.

9V5VDDQSupplyVoltageforOutput1.

71.

81.

9V1,5VREFInputReferenceVoltage0.

49xVDDQ0.

5xVDDQ0.

51xVDDQV2,3VTTTerminationVoltage(System)VREF-0.

04VREFVREF+0.

04V4Notes:1.

ThereisnospecificdeviceVDDsupplyvoltagerequirementforSSTL_18compliance.

HoweverunderallconditionsVDDQmustthanorequaltoVDD.

2.

ThevalueofVREFmaybeselectedbytheusertoprovideoptimumnoisemargininthesystem.

TypicallythevalueofVREFisexpectedtobeabout0.

5xVDDQofthetransmittingdeviceandVREFisexpectedtotrackvariationsinVDDQ.

3.

PeaktopeakACnoiseonVREFmaynotexceed2%VREF(dc).

4.

VTToftransmittingdevicemusttrackVREFofreceivingdevice.

5.

VDDQtrackswithVDD,VDDLtrackswithVDD.

ACparametersaremeasuredwithVDD,VDDQandVDDDLtiedtogether.

10.

4ODTDCElectricalCharacteristicsPARAMETER/CONDITIONSYM.

MIN.

NOM.

MAX.

UNITNOTESRtteffectiveimpedancevalueforEMRS(A6,A2)=0,1;75ΩRtt1(eff)607590Ω1RtteffectiveimpedancevalueforEMRS(A6,A2)=1,0;150ΩRtt2(eff)120150180Ω1RtteffectiveimpedancevalueforEMRS(A6,A2)=1,1;50ΩRtt3(eff)405060Ω1,2DeviationofVMwithrespecttoVDDQ/2ΔVM-6+6%1Notes:1.

TestconditionforRttmeasurements.

2.

OptionalforDDR2-667,mandatoryforDDR2-800andDDR2-1066.

MeasurementDefinitionforRtt(eff):ApplyVIH(ac)andVIL(ac)totestpinseparately,thenmeasurecurrentI(VIH(ac))andI(VIL(ac))respectively.

VIH(ac),VIL(ac),andVDDQvaluesdefinedinSSTL_18.

Rtt(eff)=(VIH(ac)–VIL(ac))/(I(VIHac)–I(VILac))MeasurementDefinitionforΔVM:Measurevoltage(VM)attestpin(midpoint)withnoload.

ΔVM=((2xVm/VDDQ)–1)x100%10.

5InputDCLogicLevelPARAMETERSYM.

MIN.

MAX.

UNITDCinputlogicHIGHVIH(dc)VREF+0.

125VDDQ+0.

3VDCinputlogicLOWVIL(dc)-0.

3VREF-0.

125V10.

6InputACLogicLevelPARAMETERSYM.

-18-25/25I/25A/25K/-3UNITMIN.

MAX.

MIN.

MAX.

ACinputlogicHIGHVIH(ac)VREF+0.

200VREF+0.

200VDDQ+VPEAK1VACinputlogicLOWVIL(ac)VREF-0.

200VSSQ-VPEAK1VREF-0.

200VNote:1.

Refertothepage67sections10.

14.

1and10.

14.

2ACOvershoot/UndershootspecificationtableforVPEAKvalue:maximumpeakamplitudeallowedforOvershoot/Undershoot.

W9725G6KBPublicationReleaseDate:Sep.

03,2012-39-RevisionA0310.

7CapacitanceSYM.

PARAMETERMIN.

MAX.

UNITCCKInputCapacitance,CLKand1.

02.

0pFCDCKInputCapacitancedelta,CLKand0.

25pFCIinputCapacitance,allotherinput-onlypins1.

01.

75pFCDIInputCapacitancedelta,allotherinput-onlypins0.

25pFCIOInput/outputCapacitance,DQ,LDM,UDM,LDQS,,UDQS,2.

53.

5pFCDIOInput/outputCapacitancedelta,DQ,LDM,UDM,LDQS,,UDQS,0.

5pF10.

8LeakageandOutputBufferCharacteristicsSYM.

PARAMETERMIN.

MAX.

UNITNOTESIILInputLeakageCurrent(0V≤VIN≤VDD)-22A1IOLOutputLeakageCurrent(Outputdisabled,0V≤VOUT≤VDDQ)-55A2VOHMinimumRequiredOutputPull-upVTT+0.

603VVOLMaximumRequiredOutputPull-downVTT-0.

603VVOTROutputTimingMeasurementReferenceLevel0.

5xVDDQV3IOH(dc)OutputMinimumSourceDCCurrent-13.

4mA4,6IOL(dc)OutputMinimumSinkDCCurrent13.

4mA5,6Notes:1.

Allotherpinsnotundertest=0V.

2.

DQ,LDQS,,UDQS,aredisabledandODTisturnedoff.

3.

TheVDDQofthedeviceundertestisreferenced.

4.

VDDQ=1.

7V;VOUT=1.

42V.

(VOUT-VDDQ)/IOHmustbelessthan21ΩforvaluesofVOUTbetweenVDDQandVDDQ-0.

28V.

5.

VDDQ=1.

7V;VOUT=0.

28V.

VOUT/IOLmustbelessthan21ΩforvaluesofVOUTbetween0Vand0.

28V.

6.

ThevaluesofIOH(dc)andIOL(dc)arebasedontheconditionsgiveninNotes3and4.

TheyareusedtotestdrivecurrentcapabilitytoensureVIHminplusanoisemarginandVILmaxminusanoisemarginaredeliveredtoanSSTL_18receiver.

W9725G6KBPublicationReleaseDate:Sep.

03,2012-40-RevisionA0310.

9DCCharacteristicsSYM.

CONDITIONS-18-25/25I/25A/25K-3UNITNOTESMAX.

MAX.

MAX.

IDD0OperatingCurrent-OneBankActive-PrechargetCK=tCK(IDD),tRC=tRC(IDD),tRAS=tRASmin(IDD);CKEisHIGH,isHIGHbetweenvalidcommands;AddressandcontrolinputsareSWITCHING;DatabusinputsareSWITCHING.

706055mA1,2,3,4,5,6IDD1OperatingCurrent-OneBankActive-Read-PrechargeIOUT=0mA;BL=4,CL=CL(IDD),AL=0;tCK=tCK(IDD),tRC=tRC(IDD),tRAS=tRASmin(IDD),tRCD=tRCD(IDD);CKEisHIGH,isHIGHbetweenvalidcommands;AddressandcontrolinputsareSWITCHING;DatabusinputsareSWITCHING.

807065mA1,2,3,4,5,6IDD2PPrechargePower-DownCurrentAllbanksidle;tCK=tCK(IDD);CKEisLOW;OthercontrolandaddressinputsareSTABLE;DataBusinputsareFLOATING.

(TCASE≤85°C)666mA1,2,3,4,5,6,7IDD2NPrechargeStandbyCurrentAllbanksidle;tCK=tCK(IDD);CKEisHIGH,isHIGH;OthercontrolandaddressinputsareSWITCHING;DatabusinputsareSWITCHING.

454035mA1,2,3,4,5,6IDD2QPrechargeQuietStandbyCurrentAllbanksidle;tCK=tCK(IDD);CKEisHIGH,isHIGH;OthercontrolandaddressinputsareSTABLE;DatabusinputsareFLOATING.

353530mA1,2,3,4,5,6IDD3PFActivePower-DownCurrentAllbanksopen;tCK=tCK(IDD);CKEisLOW;OthercontrolandaddressinputsareSTABLE;DatabusinputsareFLOATING.

(TCASE≤85°C)FastPDNExitMRS(12)=0151515mA1,2,3,4,5,6IDD3PSSlowPDNExitMRS(12)=1101010mA1,2,3,4,5,6,7IDD3NActiveStandbyCurrentAllbanksopen;tCK=tCK(IDD);tRAS=tRASmax(IDD),tRP=tRP(IDD);CKEisHIGH,isHIGHbetweenvalidcommands;OthercontrolandaddressinputsareSWITCHING;DatabusinputsareSWITCHING.

605045mA1,2,3,4,5,6W9725G6KBPublicationReleaseDate:Sep.

03,2012-41-RevisionA03IDD4ROperatingBurstReadCurrentAllbanksopen,Continuousburstreads,IOUT=0mA;BL=4,CL=CL(IDD),AL=0;tCK=tCK(IDD);tRAS=tRASmax(IDD),tRP=tRP(IDD);CKEisHIGH,isHIGHbetweenvalidcommands;AddressinputsareSWITCHING;DataBusinputsareSWITCHING.

12510595mA1,2,3,4,5,6IDD4WOperatingBurstWriteCurrentAllbanksopen,Continuousburstwrites;BL=4,CL=CL(IDD),AL=0;tCK=tCK(IDD);tRAS=tRASmax(IDD),tRP=tRP(IDD);CKEisHIGH,isHIGHbetweenvalidcommands;AddressinputsareSWITCHING;DataBusinputsareSWITCHING.

130110100mA1,2,3,4,5,6IDD5BBurstRefreshCurrenttCK=tCK(IDD);RefreshcommandeverytRFC(IDD)interval;CKEisHIGH,isHIGHbetweenvalidcommands;OthercontrolandaddressinputsareSWITCHING;DatabusinputsareSWITCHING.

757065mA1,2,3,4,5,6IDD6SelfRefreshCurrentCKE≤0.

2V,externalclockoff,CLKandat0V;OthercontrolandaddressinputsareFLOATING;DatabusinputsareFLOATING.

(TCASE≤85°C)666mA1,2,3,4,5,6,7IDD7OperatingBankInterleaveReadCurrentAllbankinterleavingreads,IOUT=0mA;BL=4,CL=CL(IDD),AL=tRCD(IDD)-1xtCK(IDD);tCK=tCK(IDD),tRC=tRC(IDD),tRRD=tRRD(IDD),tFAW=tFAW(IDD),tRCD=tRCD(IDD);CKEisHIGH,isHIGHbetweenvalidcommands;AddressbusinputsareSTABLEduringdeselects;DataBusinputsareSWITCHING.

160135115mA1,2,3,4,5,6Notes:1.

VDD=1.

8V0.

1V;VDDQ=1.

8V0.

1V.

2.

IDDspecificationsaretestedafterthedeviceisproperlyinitialized.

3.

InputslewrateisspecifiedbyACParametricTestCondition.

4.

IDDparametersarespecifiedwithODTdisabled.

5.

DataBusconsistsofDQ,LDM,UDM,LDQS,,UDQSand.

6.

DefinitionsforIDDLOW=Vin≤VIL(ac)(max)HIGH=Vin≥VIH(ac)(min)STABLE=inputsstableataHIGHorLOWlevelFLOATING=inputsatVREF=VDDQ/2SWITCHING=inputschangingbetweenHIGHandLOWeveryotherclockcycle(oncepertwoclocks)foraddressandcontrolsignals,andinputschangingbetweenHIGHandLOWeveryotherdatatransfer(onceperclock)forDQsignalsnotincludingmasksorstrobes.

7.

ThefollowingIDDvaluesmustbederated(IDDlimitsincrease),whenTCASE≥85°CIDD2Pmustbederatedby20%;IDD3P(slow)mustbederatedby30%andIDD6mustbederatedby80%.

(IDD6willincreasebythisamountifTCASE2clks)11.

20Burstwriteoperationfollowedbyprecharge:WL=(RL-1)=3W9725G6KBPublicationReleaseDate:Sep.

03,2012-80-RevisionA0311.

21Burstwriteoperationfollowedbyprecharge:WL=(RL-1)=411.

22BurstreadoperationwithAuto-precharge:RL=4(AL=1,CL=3,BL=8,tRTP≤2clks)W9725G6KBPublicationReleaseDate:Sep.

03,2012-81-RevisionA0311.

23BurstreadoperationwithAuto-precharge:RL=4(AL=1,CL=3,BL=4,tRTP>2clks)11.

24BurstreadwithAuto-prechargefollowedbyanactivationtothesamebank(tRCLimit):RL=5(AL=2,CL=3,internaltRCD=3,BL=4,tRTP≤2clks)W9725G6KBPublicationReleaseDate:Sep.

03,2012-82-RevisionA0311.

25BurstreadwithAuto-prechargefollowedbyanactivationtothesamebank(tRPLimit):RL=5(AL=2,CL=3,internaltRCD=3,BL=4,tRTP≤2clks)11.

26BurstwritewithAuto-precharge(tRCLimit):WL=2,WR=2,BL=4,tRP=3W9725G6KBPublicationReleaseDate:Sep.

03,2012-83-RevisionA0311.

27BurstwritewithAuto-precharge(WR+tRPLimit):WL=4,WR=2,BL=4,tRP=311.

28SelfRefreshTimingNotes:1.

Devicemustbeinthe"Allbanksidle"statepriortoenteringSelfRefreshmode.

2.

ODTmustbeturnedofftAOFDbeforeenteringSelfRefreshmode,andcanbeturnedonagainwhentXSRDtimingissatisfied.

3.

tXSRDisappliedforaReadoraReadwithAuto-prechargecommand.

tXSNRisappliedforanycommandexceptaReadoraReadwithAuto-prechargecommand.

W9725G6KBPublicationReleaseDate:Sep.

03,2012-84-RevisionA0311.

29ActivePowerDownModeEntryandExitTiming11.

30PrechargedPowerDownModeEntryandExitTimingW9725G6KBPublicationReleaseDate:Sep.

03,2012-85-RevisionA0311.

31ClockfrequencychangeinprechargePowerDownmodeW9725G6KBPublicationReleaseDate:Sep.

03,2012-86-RevisionA0312.

PACKAGESPECIFICATIONPackageOutlineWBGA-84(8x12.

5mm2)W9725G6KBPublicationReleaseDate:Sep.

03,2012-87-RevisionA0313.

REVISIONHISTORYVERSIONDATEPAGEDESCRIPTIONA01Apr.

25,2012AllInitialformaldatasheetA02Jul.

06,20124,5,13,37,38,40~42,45,46Added25Aand25KautomotivegradepartsA03Sep.

03,20129AddedVTTvoltageramptimerequiredconditioninsection8.

1power-upandinitializationsequence83Addednotesfor11.

28selfrefreshtimingdiagram86Added"ddd"and"eee"symbolsinWBGA84packageoutlinedrawingdiagramImportantNoticeWinbondproductsarenotdesigned,intended,authorizedorwarrantedforuseascomponentsinsystemsorequipmentintendedforsurgicalimplantation,atomicenergycontrolinstruments,airplaneorspaceshipinstruments,transportationinstruments,trafficsignalinstruments,combustioncontrolinstruments,orforotherapplicationsintendedtosupportorsustainlife.

Furthermore,WinbondproductsarenotintendedforapplicationswhereinfailureofWinbondproductscouldresultorleadtoasituationwhereinpersonalinjury,deathorseverepropertyorenvironmentaldamagecouldoccur.

WinbondcustomersusingorsellingtheseproductsforuseinsuchapplicationsdosoattheirownriskandagreetofullyindemnifyWinbondforanydamagesresultingfromsuchimproperuseorsales.

- devicekb936929相关文档

- biologicalkb936929

- 0.40kb936929

- Levelkb936929

- warrantykb936929

- Vcckb936929

- Patchingkb936929

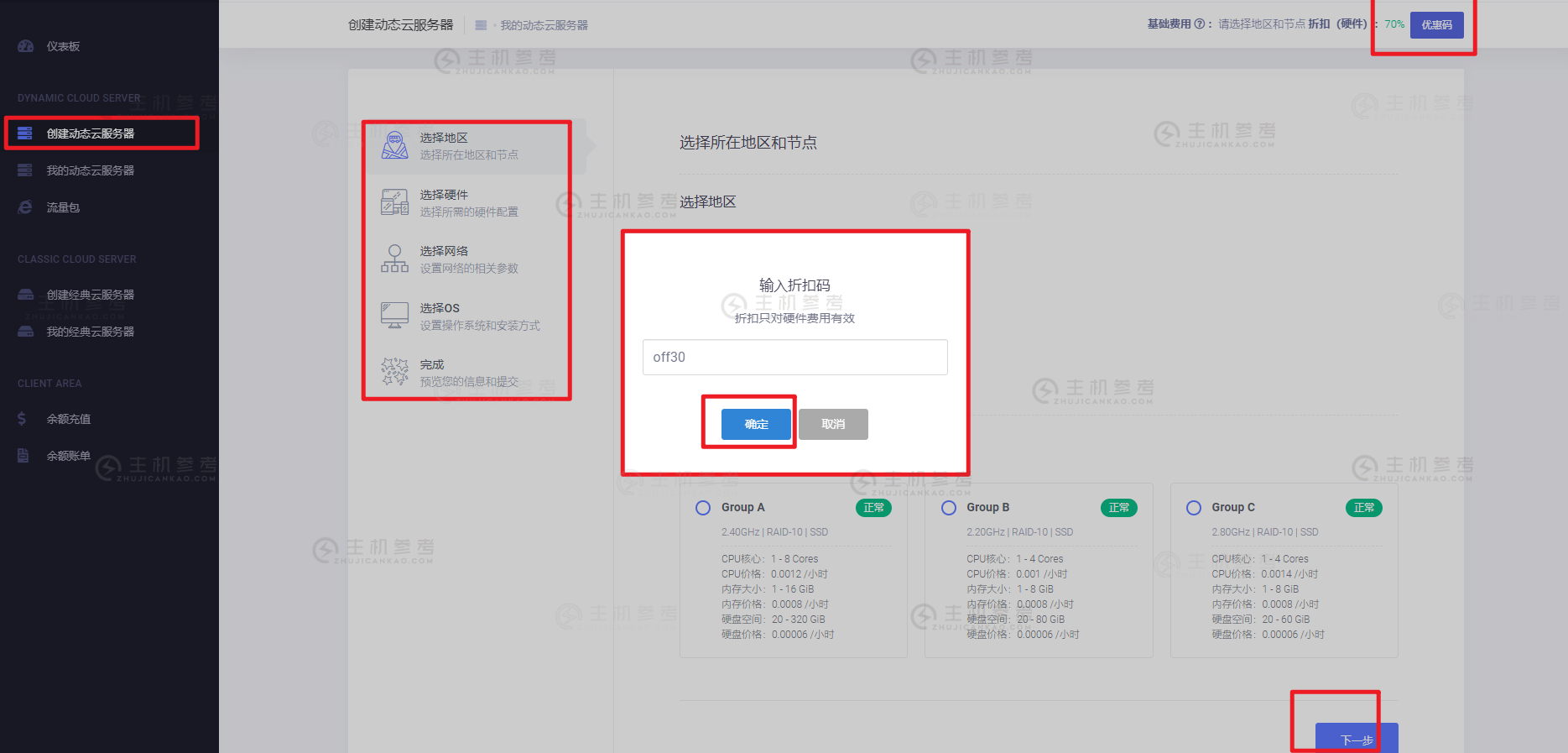

HostMem,最新优惠促销,全场75折优惠,大硬盘VPS特价优惠,美国洛杉矶QuadraNet机房,KVM虚拟架构,KVM虚拟架构,2核2G内存240GB SSD,100Mbps带宽,27美元/年

HostMem近日发布了最新的优惠消息,全场云服务器产品一律75折优惠,美国洛杉矶QuadraNet机房,基于KVM虚拟架构,2核心2G内存240G SSD固态硬盘100Mbps带宽4TB流量,27美元/年,线路方面电信CN2 GT,联通CU移动CM,有需要美国大硬盘VPS云服务器的朋友可以关注一下。HostMem怎么样?HostMem服务器好不好?HostMem值不值得购买?HostMem是一家...

WebHorizon($10.56/年)256MB/5G SSD/200GB/日本VPS

WebHorizon是一家去年成立的国外VPS主机商,印度注册,提供虚拟主机和VPS产品,其中VPS包括OpenVZ和KVM架构,有独立IP也有共享IP,数据中心包括美国、波兰、日本、新加坡等(共享IP主机可选机房更多)。目前商家对日本VPS提供一个8折优惠码,优惠后最低款OpenVZ套餐年付10.56美元起。OpenVZCPU:1core内存:256MB硬盘:5G NVMe流量:200GB/1G...

无法忍受旧版不兼容PHP7+主题 更换新主题

今天父亲节我们有没有陪伴家人一起吃个饭,还是打个电话问候一下。前一段时间同学将网站账户给我说可以有空更新点信息确保他在没有时间的时候还能保持网站有一定的更新内容。不过,他这个网站之前采用的主题也不知道来源哪里,总之各种不合适,文件中很多都是他多年来手工修改的主题拼接的,并非完全适应WordPress已有的函数,有些函数还不兼容最新的PHP版本,于是每次出现问题都要去排查。于是和他商量后,就抽时间把...

kb936929为你推荐

-

回收站在哪回收站 在c盘的路径推广方法最有效的推广方法是什么?bbsxpbbsxp 2008 无法创建数据库雅虎社区雅虎是中国的吗无线路由器限速设置无线路由器能设置限速吗?或者说那个牌子的能。sourcegear请问高手这是什么“dynamsoft sourceanywhere for vss”,做项目的时候用的,我是新手不知道这是干什么。怎么样免费装扮qq空间如何免费装扮qq空间vbscript教程请教一下高手们,这个VBS脚本难不难啊,我想学学这个,但是又不知道该从哪入手,希望高手指点指点??rewritebase为什么我写.htaccess这个 rewriterule 进入死循环了,高手帮忙修改网站推广外链在网站推广中,有着一种“购买外链”是什么意思