specificationo3o4o5

o3o4o5 com 时间:2021-03-02 阅读:()

DS550April19,2010www.

xilinx.

com1ProductSpecification2006-2010Xilinx,Inc.

Xilinx,Inc.

XILINX,theXilinxlogo,Virtex,Spartan,ISEandotherdesignatedbrandsincludedhereinaretrademarksofXilinxintheUnitedStatesandothercountries.

Allothertrademarksarethepropertyoftheirrespectiveowners.

IntroductionTheLogiCOREIPVirtex-5FPGAEmbeddedTri-ModeEthernetMACWrapperautomatesthegenerationofHDLwrapperfilesfortheEmbeddedTri-ModeEthernetMAC(EthernetMAC)inVirtex-5LXT,SXT,FXTandTXTFPGAsusingtheXilinxCOREGeneratorsoftware.

VHDLandVeriloginstantiationtemplatesareavailableintheLibrariesGuidefortheVirtex-5FPGAEthernetMACprimitive;however,duetothecomplexityandlargenumberofports,theCOREGeneratorsoftwaresimplifiesintegrationoftheEthernetMACbyprovid-ingHDLexamplesbasedonuser-selectableconfigura-tions.

FeaturesAllowsselectionofoneorbothEthernetMACs(EMAC0/EMAC1)fromtheEthernetMACprimitiveSetstheEMAC0/EMAC1attributesbasedonuseroptionsProvidesuser-configurableEthernetMACphysicalinterfacesSupportsMII,GMII,RGMIIv1.

3,RGMIIv2.

0,SGMII,and1000BASE-XPCS/PMAinterfacesInstantiatesclockbuffers,DCMs,Virtex-5FPGARocketIOGTPorGTXtransceivers,andlogicasrequiredfortheselectedphysicalinterfacesProvidesasimpleFIFO-loopbackexampledesign,connectedtotheMACclientinterfacesProvidesasimpledemonstrationtestbenchbasedontheselectedconfigurationGeneratesVHDLorVerilogVirtex-5FPGAEmbeddedTri-ModeEthernetMACWrapperv1.

7DS550April19,2010ProductSpecificationLogiCOREIPFactsSupportedFPGAFamily1Virtex-5Performance10Mbps,100Mbps,1GbpsExampleDesignResourcesLUTs380-9302FFs440-12202BlockRAMs(18k)4-102DCM0-12BUFG2-102WrapperHighlightsOptimizedClockingLogicHDLExampleDesignHardwareVerifiedDemonstrationTestBenchProvidedwithWrapperDocumentationProductSpecificationGettingStartedGuideUserGuide3DesignFileFormatsHDLExampleDesign,DemonstrationTestBench,ScriptsConstraintsFileUserConstraintsFile(.

ucf)ExampleDesignsExampleFIFOconnectedtoClientI/FDemonstrationTestEnvironmentDesignToolRequirementsSupportedHDLVHDLand/orVerilogSynthesisXST12.

1XilinxToolsISE12.

1SimulationTools4MentorGraphicsModelSim6.

5candabove5CadenceIncisiveEnterpriseSimulator(IES)v9.

2andabove5SynopsysVCSandVCSMX2009.

12andabove51.

Forthecompletelistofsupporteddevices,seethe12.

1releasenotesforthiscore.

2.

Theprecisenumberdependsonuserconfiguration;seeDeviceUtilization.

3.

Availablefromwww.

xilinx.

com/support/documentation/ip_documentation/ug194.

pdf.

4.

RequiresaVerilogLRM-IEEE1364-2005encryption-compliantsimulator.

ForVHDLsimulation,amixedHDLlicenseisrequired.

5.

Scriptsprovidedforlistedsimulatorsonly.

Virtex-5FPGAEmbeddedTri-ModeEthernetMACWrapperv1.

72www.

xilinx.

comApril19,2010ProductSpecificationEthernetArchitectureOverviewFigure1displaystheEthernetMACarchitecturefromtheMACtotheright,asdefinedintheIEEE802.

3specification,andalsoillustrateswherethesupportedphysicalinterfacesfitintothearchitecture.

MACTheEthernetMACisdefinedintheIEEE802.

3specificationclauses2,3,and4.

AMACisresponsiblefortheEthernetframingprotocolsanderrordetectionoftheseframes.

TheMACisindependentof,andcanconnectto,anytypeofphysicalsublayer.

GMII/MIITheMediaIndependentInterface(MII),definedinIEEE802.

3clause22,isaparallelinterfacethatcon-nectsa10-Mbpsand/or100-MbpscapableMACtothephysicalsublayers.

TheGigabitMediaIndepen-dentInterface(GMII),definedinIEEE802.

3clause35,isanextensionoftheMIIusedtoconnecta1-GbpscapableMACtothephysicalsublayers.

MIIcanbeconsideredasubsetofGMII,andasaresult,GMII/MIIcancarryEthernettrafficat10Mbps,100Mbps,and1Gbps.

RGMIITheReduced-GMII(RGMII)isanalternativetoGMII/MII.

RGMIIachievesa50-percentreductioninthepincount,achievedbytheuseofdouble-data-rate(DDR)flip-flops.

Forthisreason,RGMIIispre-ferredoverGMIIbyPCBdesigners.

RGMIIcancarryEthernettrafficat10Mbps,100Mbps,and1Gbps.

SGMIITheSerial-GMII(SGMII)interfaceisanalternativetoGMII/MII.

SGMIIconvertstheparallelinterfaceoftheGMII/MIIintoaserialformatusingaRocketIOGTPorGTXtransceiver,radicallyreducingtheI/Ocount.

Forthisreason,itisoftenthepreferredinterfaceofPCBdesigners.

SGMIIcancarryEthernettrafficat10Mbps,100Mbps,and1Gbps.

X-RefTarget-Figure1Figure1:TypicalEthernetArchitectureTCPIPFIFOI/FEthernetMACPCSPMAPMDGMII/MIIRGMIISGMII(RocketIO)1000BASE-X(RocketIO)PhysicalSublayersDS550April19,2010www.

xilinx.

com3ProductSpecificationVirtex-5FPGAEmbeddedTri-ModeEthernetMACWrapperv1.

7PCS,PMA,PMDThecombinationofthePhysicalCodingSublayer(PCS),thePhysicalMediumAttachment(PMA),andthePhysicalMediumDependent(PMD)sublayercomprisethephysicallayersoftheEthernetprotocol.

TwomainphysicalstandardsarespecifiedforEthernet:BASE-T,acopperstandardusingtwistedpaircablingsystemsBASE-X,usuallyafibreopticalphysicalstandardusingshortandlongwavelengthlaserBASE-Tdevices,supporting10Mbps,100Mbps,and1GbpsEthernetspeeds,arereadilyavailableasoff-the-shelfparts.

AsillustratedinFigures1and2,thesecanbeconnectedusingGMII/MII,RGMII,orSGMIItoprovideatri-speedEthernetport.

TheEthernetMAChasbuilt-in1000BASE-XPCS/PMAfunctionalityandcanbeconnectedtoaRock-etIOGTPorGTXtransceivertoprovidea1Gbpsfibreopticport,asillustratedinFigure3.

ApplicationsTypicalapplicationsfortheEthernetMACcoreincludeEthernetTri-speedBASE-TPortEthernet1000BASE-XPortEthernetTri-speedBASE-TPortFigure2illustratesatypicalapplicationforasingleEthernetMAC.

ThePHYsideofthecoreisimple-mentinganexternalGMII/MIIbyconnectingittoIOBs;theexternalGMII/MIIisconnectedtoanoff-the-shelfEthernetPHYdevice,whichperformstheBASE-Tstandardat1Gbps,100Mbps,and10Mbpsspeeds.

Alternatively,theexternalGMII/MIIcanbereplacedwithanRGMII(asshown)orasanSGMII(whichrequirestheuseofaRocketIOGTPorGTXtransceiver).

GMII,RGMII,andSGMIIfunc-tionalityaredemonstratedintheHDLexamplesprovidedwiththeexampledesign.

TheclientsideoftheEthernetMACisshownconnectedtothe10Mbps,100Mbps,1GbpsEthernetFIFO(deliveredwiththeexampledesign)tocompleteasingleEthernetport.

ThisportisdisplayedconnectedtoaSwitchorRoutingmatrix,whichcancontainseveralports.

X-RefTarget-Figure2Figure2:Typical1000BASE-TApplicationTwistedCopperPairGMII/MII(orRGMII)MACIOBsTri-speedBASE-TPHYVirtex-5DeviceEthernetMACSwitchorRouter10Mbps,100Mbps,1Gbps10Mbps,100Mbps,1GbpsEthernetFIFOVirtex-5FPGAEmbeddedTri-ModeEthernetMACWrapperv1.

74www.

xilinx.

comApril19,2010ProductSpecificationEthernet1000BASE-XPortFigure3illustratesatypicalapplicationforasingleEthernetMAC.

ThePHYsideoftheMACiscon-nectedtoaRocketIOGTPorGTXtransceiver,whichinturnisconnectedtoanexternaloff-the-shelfGBICorSFPopticaltransceiver.

The1000BASE-XlogiccanbeoptionallyprovidedbytheEthernetMAC,asdisplayed.

1000BASE-XfunctionalityisdemonstratedintheHDLexamplesprovidedwiththeexampledesign.

TheclientsideoftheEthernetMACisshownconnectedtothe10Mbps,100Mbps,1GbpsEthernetFIFO(deliveredwiththeexampledesign)tocompleteasingleGigabitEthernetport.

Thisportiscon-nectedtoaSwitchorRoutingmatrix,whichcancontainseveralportsX-RefTarget-Figure3Figure3:Typical1000BASE-XApplicationEthernetMACRocketIOTransceiverMAC1000BASE-XPCS/PMAOpticalFiberPMARXP/RXNGBICorSFPOpticalTransceiverTXP/TXNSwitchorRouter1Gbps10Mbps,100Mbps,1GbpsEthernetFIFODS550April19,2010www.

xilinx.

com5ProductSpecificationVirtex-5FPGAEmbeddedTri-ModeEthernetMACWrapperv1.

7ExampleDesignOverviewFigure4illustratesthemajorfunctionalblocksoftheEthernetMACexampledesign.

AllillustratedcomponentsareprovidedinHDL,withtheexceptionoftheEthernetMACcomponent.

X-RefTarget-Figure4Figure4:ExampleDesignEmbeddedEthernetMACWrapperFPGAFabricClockCircuitryPhysicalI/F(GMII/MII,RGMII,orRocketIOPhysicalI/F(GMII/MII,RGMII,orRocketIO)EMAC1HostInterfaceEMAC0EmbeddedEthernetMACPhysicalInterfacecomponent_name_blockcomponent_name_example_designAddressSwapModuleAddressSwapModule10M/100M/1GEthernetFIFO10M/100M/1GEthernetFIFOClientInterfacecomponent_name_locallinkTxClientFIFORxClientFIFOTxClientFIFORxClientFIFOLocalLinkInterfaceLocalLinkInterfaceVirtex-5FPGAEmbeddedTri-ModeEthernetMACWrapperv1.

76www.

xilinx.

comApril19,2010ProductSpecificationEthernetMACExampleDesignTheexampledesignisarrangedforquickadaptationandcanbedownloadedontoanFPGAtoprovidearealhardwaretestenvironment.

Inaddition,alltheclockmanagementlogicrequiredtooperatetheEthernetMACanditsexampledesignisprovided.

DCMs,BUFGs,andsoforthareinstantiatedasrequired.

Thedataisloopedbackattheclientinterface,enablingtheEthernetMACtobequicklyconnectedtoaprotocoltester—framesinjectedintotheEthernetMACPHYReceiveportarerelayedbackthroughtheEthernetMACandoutthroughtheEthernetMACsPHYTransmitport.

Usingthismethod,theyarereceivedbackattheprotocoltester.

ThedesignincludesanAddressSwappingModuleandaFIFO.

FramesreceivedbytheEthernetMACarepassedthroughtheReceivesideoftheFIFO.

DatafromtheReceivesideoftheFIFOispassedintotheAddressSwapModuleandthenontotheTransmitsideoftheFIFOusingaLocalLinkinterface.

TheTransmitFIFOqueuesframesfortransmissionandconnectsdirectlytotheclientsideTransmitinterfaceoftheEthernetMAC.

AddressSwapModuleTheAddressSwapModuleswitchestheDestinationAddressandSourceAddresswithinthereceivedMACframe.

Usingthismethod,framesreceivedfromalinkpartner,forexampleaprotocoltester,arerelayedbacktothecorrectDestinationAddress.

10Mbps,100Mbps,1GbpsEthernetFIFOThe10Mbps,100Mbps,1GbpsEthernetFIFOisawrapperfilearoundtheReceiveandTransmitFIFOcomponents.

Thesecomponentscanbeusedinmorecomplexclientapplications,asillustratedinFigures2and3.

TousetheFIFOs,thecomponent_name_locallinkcomponentcanbeinstantiatedintheuserdesign.

ReceiveClientFIFOTheReceive(Rx)ClientFIFO,a4k-byteFIFOimplementedinblockRAMs,canbeusedformorecom-plexclientapplicationsandcanbeconnecteddirectlytotheRxClientInterfaceoftheEthernetMAC.

TheRxClientprovidesaLocalLinkconnectionfortheuser.

TheFIFOoperatesatallEthernetspeedssupportedbytheEthernetMAC.

TheFIFOdropsallframesmarkedasbadfromtheEthernetMACsothatonlyerror-freeframesarepassedtotheEthernetclient.

TransmitClientFIFOTheTransmit(Tx)ClientFIFO,a4k-byteFIFOimplementedinblockRAMs,canusedformorecomplexclientapplicationsandcanbeconnecteddirectlytotheTxClientInterfaceoftheEthernetMAC.

TheTxClientFIFOprovidesaLocalLinkconnectionfortheuser.

TheFIFOoperatesatallEthernetspeedssupportedbytheEthernetMAC.

TheFIFOiscapableofhalf-duplexre-transmission.

Forthisreason,ifacollisionoccursonthemedium,theEthernetMACindicatesacollisionontheTxClientinterfaceandtheFIFOautomaticallyre-queuestheframeforre-transmission.

DS550April19,2010www.

xilinx.

com7ProductSpecificationVirtex-5FPGAEmbeddedTri-ModeEthernetMACWrapperv1.

7EthernetMACWrapperTheEthernetMACwrapperfileinstantiatesthefullEthernetMACprimitive.

ForoneorbothEthernetMACs(EMAC0/EMAC1),thefollowingapplies:Allunusedinputportsontheprimitivearetiedtotheappropriatelogiclevel;allunusedoutputportsareleftunconnected.

TheEthernetMACattributesaresetbasedonoptionsselectedintheCOREGeneratorsoftware.

Onlyusedportsareconnectedtotheportsofthewrapperfile.

ThissimplifiedwrappershouldbeusedastheinstantiationtemplatefortheEthernetMACincus-tomerdesigns.

PhysicalI/FAnappropriatePhysicalInterfaceisprovidedforeachselectedEMAC0/EMAC1.

Thisinterfacecon-nectsthephysicalinterfaceoftheEthernetMACblocktotheI/OoftheFPGA.

Asrequired,thefollow-ingcomponentsareprovided:ForGMII/MII,thiscomponentcontainsInput/Outputblock(IOB)buffersandIOBflip-flops.

ForRGMII,thiscomponentcontainscontainIOBbuffers,IOBDouble-DataRateflip-flopsandIODELAYelementstoaligntheincomingdatawiththereceiverclock.

AnIODELAYelementisalsousedtodelaythetransmittedclockinRGMIIV2.

0.

For1000BASE-XPCS/PMAorSGMII,thiscomponentinstantiatesandconnectsaRocketIOGTPorGTXtransceiver.

Virtex-5FPGAEmbeddedTri-ModeEthernetMACWrapperv1.

78www.

xilinx.

comApril19,2010ProductSpecificationDeviceUtilizationThefollowingsectionsprovideapproximatedevice-utilizationfiguresforcommonconfigurationsoftheEthernetMACanditsexampledesign:1GbpsOnlyOperationTri-SpeedOperation100Mbpsor10MbpsOperationOfinterestistheutilizationofclockresources,specificallytheglobalclockusage(BUFGs),whichshouldinfluencetheselectionoftheinterfacetype.

Notethattheseclockresourcefiguresdonotcon-sideranyclockthatcanbeusedfortheHostInterface.

1GbpsOnlyOperationTable1definesapproximateutilizationfiguresforcommonconfigurationsoftheEthernetMACanditsexampledesignfor1Gbpsoperation.

Table1:DeviceUtilizationfor1GbpsOperationParameterValuesDeviceResourcesPhysicalInterfaceEthernetMACUsageLUTsRegisters18KBlockRAMsBUFGsDCMsGMIISingleEMAC3804504211.

TheseimplementationsuseIDLEAYelements,whichrequirea200MHzreferenceclockfortheassociatedIDELAYCTRL.

Therefer-enceclock'sBUFGisnotaccountedfor.

0BothEMACs7608808310RGMII1.

3SingleEMAC3804604210BothEMACs7609008310RGMII2.

0SingleEMAC3804604210BothEMACs7609008310SGMIISingleEMAC390440410BothEMACs7808708101000BASE-X(8-bitclient)SingleEMAC390440410BothEMACs7808708101000BASE-X(16-bitclient)SingleEMAC370560431BothEMACs7301120831DS550April19,2010www.

xilinx.

com9ProductSpecificationVirtex-5FPGAEmbeddedTri-ModeEthernetMACWrapperv1.

7Tri-SpeedOperationTable2definesapproximateutilizationfiguresforcommonconfigurationsoftheEthernetMACanditsexampledesign10Mbps,100Mbps,or1Gbpsoperation.

Table2:DeviceUtilizationforTri-SpeedOperationParameterValuesDeviceResourcesPhysicalInterfaceEthernetMACUsageLUTsRegisters18KBlockRAMsBUFGsRCLKsGMII/MII(standardclocking)SingleEMAC4004804511.

TheseimplementationsuseIDLEAYelements,whichrequirea200MHzreferenceclockfortheassociatedIDELAYCTRL.

Therefer-enceclock'sBUFGisnotaccountedfor.

0BothEMACs79095081010GMII/MII(withclockenable)SingleEMAC4005004210BothEMACs7909808410GMII/MII(withbytePHY)SingleEMAC4105104210BothEMACs8109908410RGMII1.

3(standardclocking)SingleEMAC4004904410BothEMACs7909708810RGMII1.

3(withclockenable)SingleEMAC4005104210BothEMACs79010008410RGMII2.

0(standardclocking)SingleEMAC4004904410BothEMACs7909708810RGMII2.

0(withclockenable)SingleEMAC4005104210BothEMACs79010008410SGMIISingleEMAC470620521BothEMACs93012201032Virtex-5FPGAEmbeddedTri-ModeEthernetMACWrapperv1.

710www.

xilinx.

comApril19,2010ProductSpecification100Mbpsor10MbpsOperationTable3providesapproximateutilizationfiguresforcommonconfigurationsoftheEthernetMACanditsexampledesignfor10Mbpsor100Mbpsoperation.

Forallotherinterfaces,seeTri-SpeedOperation.

OrderingInformationTheEthernetMACwrapperisprovidedundertheEndUserLicenseAgreementandcanbegeneratedusingCOREGeneratorsoftwarev12.

1andhigher.

TheCOREGeneratorsoftwareisshippedwithXilinxISEDesignSuiteSeriesDevelopmentsoftware.

InISEv12.

1andlater,alicensekeyisnotrequiredtoaccesstheIP.

ToaccessthewrapperinISEv11.

4andolder,anocostfulllicensemustbeobtainedfromXilinx.

Seetheproductpage:www.

xilinx.

com/products/ipcenter/V5_Embedded_TEMAC_Wrapper.

htmContactyourlocalXilinxsalesrepresentativeforpricingandavailabilityofotherXilinxLogiCOREIPmodulesandsoftware.

InformationonadditionalLogiCOREIPmodulesisavailableontheXilinxIPCenter.

RevisionHistoryTable3:DeviceUtilizationfor10Mbps,100MbpsOperationParameterValuesDeviceResourcesPhysicalInterfaceEthernetMACUsageLUTsRegisters18KBlockRAMsBUFGsMII(standardclocking)SingleEMAC40046044BothEMACs78092088MII(withclockenable)SingleEMAC39048042BothEMACs78095084MII(withbytePHY)SingleEMAC40048042BothEMACs80096084DateVersionRevision10/23/061.

0InitialXilinxrelease.

2/15/072.

0Coreupdatedtoversion1.

2;Xilinxtools9.

1i.

8/8/052.

2Coreupdatedtoversion1.

3;Xilinxtools9.

2,IUSv5.

8.

3/24/083.

0Coreupdatedtoversion1.

4;Xilinxtools10.

1;Virtex-5FXTFPGAsupport.

9/19/084.

0Coreupdatedtoversion1.

5;Virtex-5TXTFPGAsupport.

4/24/095.

0Coreupdatedtoversion1.

6andXilinxtoolsupdatedtoversion11.

1.

4/9/106.

0Coreupdatedtoversion1.

7andXilinxtoolsupdatedtoversion12.

1.

DS550April19,2010www.

xilinx.

com11ProductSpecificationVirtex-5FPGAEmbeddedTri-ModeEthernetMACWrapperv1.

7NoticeofDisclaimerXilinxisprovidingthisproductdocumentation,hereinafter"Information,"toyou"ASIS"withnowarrantyofanykind,expressorimplied.

XilinxmakesnorepresentationthattheInformation,oranyparticularimplementationthereof,isfreefromanyclaimsofinfringement.

YouareresponsibleforobtaininganyrightsyoumayrequireforanyimplementationbasedontheInformation.

Allspecificationsaresubjecttochangewithoutnotice.

XILINXEXPRESSLYDISCLAIMSANYWARRANTYWHATSOEVERWITHRESPECTTOTHEADEQUACYOFTHEINFORMATIONORANYIMPLEMENTATIONBASEDTHEREON,INCLUDINGBUTNOTLIMITEDTOANYWARRANTIESORREPRESENTATIONSTHATTHISIMPLEMENTATIONISFREEFROMCLAIMSOFINFRINGEMENTANDANYIMPLIEDWARRANTIESOFMERCHANTABILITYORFITNESSFORAPARTICULARPURPOSE.

Exceptasstatedherein,noneoftheInformationmaybecopied,reproduced,distributed,republished,downloaded,displayed,posted,ortransmittedinanyformorbyanymeansincluding,butnotlimitedto,electronic,mechanical,photocopying,recording,orotherwise,withoutthepriorwrittenconsentofXilinx.

xilinx.

com1ProductSpecification2006-2010Xilinx,Inc.

Xilinx,Inc.

XILINX,theXilinxlogo,Virtex,Spartan,ISEandotherdesignatedbrandsincludedhereinaretrademarksofXilinxintheUnitedStatesandothercountries.

Allothertrademarksarethepropertyoftheirrespectiveowners.

IntroductionTheLogiCOREIPVirtex-5FPGAEmbeddedTri-ModeEthernetMACWrapperautomatesthegenerationofHDLwrapperfilesfortheEmbeddedTri-ModeEthernetMAC(EthernetMAC)inVirtex-5LXT,SXT,FXTandTXTFPGAsusingtheXilinxCOREGeneratorsoftware.

VHDLandVeriloginstantiationtemplatesareavailableintheLibrariesGuidefortheVirtex-5FPGAEthernetMACprimitive;however,duetothecomplexityandlargenumberofports,theCOREGeneratorsoftwaresimplifiesintegrationoftheEthernetMACbyprovid-ingHDLexamplesbasedonuser-selectableconfigura-tions.

FeaturesAllowsselectionofoneorbothEthernetMACs(EMAC0/EMAC1)fromtheEthernetMACprimitiveSetstheEMAC0/EMAC1attributesbasedonuseroptionsProvidesuser-configurableEthernetMACphysicalinterfacesSupportsMII,GMII,RGMIIv1.

3,RGMIIv2.

0,SGMII,and1000BASE-XPCS/PMAinterfacesInstantiatesclockbuffers,DCMs,Virtex-5FPGARocketIOGTPorGTXtransceivers,andlogicasrequiredfortheselectedphysicalinterfacesProvidesasimpleFIFO-loopbackexampledesign,connectedtotheMACclientinterfacesProvidesasimpledemonstrationtestbenchbasedontheselectedconfigurationGeneratesVHDLorVerilogVirtex-5FPGAEmbeddedTri-ModeEthernetMACWrapperv1.

7DS550April19,2010ProductSpecificationLogiCOREIPFactsSupportedFPGAFamily1Virtex-5Performance10Mbps,100Mbps,1GbpsExampleDesignResourcesLUTs380-9302FFs440-12202BlockRAMs(18k)4-102DCM0-12BUFG2-102WrapperHighlightsOptimizedClockingLogicHDLExampleDesignHardwareVerifiedDemonstrationTestBenchProvidedwithWrapperDocumentationProductSpecificationGettingStartedGuideUserGuide3DesignFileFormatsHDLExampleDesign,DemonstrationTestBench,ScriptsConstraintsFileUserConstraintsFile(.

ucf)ExampleDesignsExampleFIFOconnectedtoClientI/FDemonstrationTestEnvironmentDesignToolRequirementsSupportedHDLVHDLand/orVerilogSynthesisXST12.

1XilinxToolsISE12.

1SimulationTools4MentorGraphicsModelSim6.

5candabove5CadenceIncisiveEnterpriseSimulator(IES)v9.

2andabove5SynopsysVCSandVCSMX2009.

12andabove51.

Forthecompletelistofsupporteddevices,seethe12.

1releasenotesforthiscore.

2.

Theprecisenumberdependsonuserconfiguration;seeDeviceUtilization.

3.

Availablefromwww.

xilinx.

com/support/documentation/ip_documentation/ug194.

pdf.

4.

RequiresaVerilogLRM-IEEE1364-2005encryption-compliantsimulator.

ForVHDLsimulation,amixedHDLlicenseisrequired.

5.

Scriptsprovidedforlistedsimulatorsonly.

Virtex-5FPGAEmbeddedTri-ModeEthernetMACWrapperv1.

72www.

xilinx.

comApril19,2010ProductSpecificationEthernetArchitectureOverviewFigure1displaystheEthernetMACarchitecturefromtheMACtotheright,asdefinedintheIEEE802.

3specification,andalsoillustrateswherethesupportedphysicalinterfacesfitintothearchitecture.

MACTheEthernetMACisdefinedintheIEEE802.

3specificationclauses2,3,and4.

AMACisresponsiblefortheEthernetframingprotocolsanderrordetectionoftheseframes.

TheMACisindependentof,andcanconnectto,anytypeofphysicalsublayer.

GMII/MIITheMediaIndependentInterface(MII),definedinIEEE802.

3clause22,isaparallelinterfacethatcon-nectsa10-Mbpsand/or100-MbpscapableMACtothephysicalsublayers.

TheGigabitMediaIndepen-dentInterface(GMII),definedinIEEE802.

3clause35,isanextensionoftheMIIusedtoconnecta1-GbpscapableMACtothephysicalsublayers.

MIIcanbeconsideredasubsetofGMII,andasaresult,GMII/MIIcancarryEthernettrafficat10Mbps,100Mbps,and1Gbps.

RGMIITheReduced-GMII(RGMII)isanalternativetoGMII/MII.

RGMIIachievesa50-percentreductioninthepincount,achievedbytheuseofdouble-data-rate(DDR)flip-flops.

Forthisreason,RGMIIispre-ferredoverGMIIbyPCBdesigners.

RGMIIcancarryEthernettrafficat10Mbps,100Mbps,and1Gbps.

SGMIITheSerial-GMII(SGMII)interfaceisanalternativetoGMII/MII.

SGMIIconvertstheparallelinterfaceoftheGMII/MIIintoaserialformatusingaRocketIOGTPorGTXtransceiver,radicallyreducingtheI/Ocount.

Forthisreason,itisoftenthepreferredinterfaceofPCBdesigners.

SGMIIcancarryEthernettrafficat10Mbps,100Mbps,and1Gbps.

X-RefTarget-Figure1Figure1:TypicalEthernetArchitectureTCPIPFIFOI/FEthernetMACPCSPMAPMDGMII/MIIRGMIISGMII(RocketIO)1000BASE-X(RocketIO)PhysicalSublayersDS550April19,2010www.

xilinx.

com3ProductSpecificationVirtex-5FPGAEmbeddedTri-ModeEthernetMACWrapperv1.

7PCS,PMA,PMDThecombinationofthePhysicalCodingSublayer(PCS),thePhysicalMediumAttachment(PMA),andthePhysicalMediumDependent(PMD)sublayercomprisethephysicallayersoftheEthernetprotocol.

TwomainphysicalstandardsarespecifiedforEthernet:BASE-T,acopperstandardusingtwistedpaircablingsystemsBASE-X,usuallyafibreopticalphysicalstandardusingshortandlongwavelengthlaserBASE-Tdevices,supporting10Mbps,100Mbps,and1GbpsEthernetspeeds,arereadilyavailableasoff-the-shelfparts.

AsillustratedinFigures1and2,thesecanbeconnectedusingGMII/MII,RGMII,orSGMIItoprovideatri-speedEthernetport.

TheEthernetMAChasbuilt-in1000BASE-XPCS/PMAfunctionalityandcanbeconnectedtoaRock-etIOGTPorGTXtransceivertoprovidea1Gbpsfibreopticport,asillustratedinFigure3.

ApplicationsTypicalapplicationsfortheEthernetMACcoreincludeEthernetTri-speedBASE-TPortEthernet1000BASE-XPortEthernetTri-speedBASE-TPortFigure2illustratesatypicalapplicationforasingleEthernetMAC.

ThePHYsideofthecoreisimple-mentinganexternalGMII/MIIbyconnectingittoIOBs;theexternalGMII/MIIisconnectedtoanoff-the-shelfEthernetPHYdevice,whichperformstheBASE-Tstandardat1Gbps,100Mbps,and10Mbpsspeeds.

Alternatively,theexternalGMII/MIIcanbereplacedwithanRGMII(asshown)orasanSGMII(whichrequirestheuseofaRocketIOGTPorGTXtransceiver).

GMII,RGMII,andSGMIIfunc-tionalityaredemonstratedintheHDLexamplesprovidedwiththeexampledesign.

TheclientsideoftheEthernetMACisshownconnectedtothe10Mbps,100Mbps,1GbpsEthernetFIFO(deliveredwiththeexampledesign)tocompleteasingleEthernetport.

ThisportisdisplayedconnectedtoaSwitchorRoutingmatrix,whichcancontainseveralports.

X-RefTarget-Figure2Figure2:Typical1000BASE-TApplicationTwistedCopperPairGMII/MII(orRGMII)MACIOBsTri-speedBASE-TPHYVirtex-5DeviceEthernetMACSwitchorRouter10Mbps,100Mbps,1Gbps10Mbps,100Mbps,1GbpsEthernetFIFOVirtex-5FPGAEmbeddedTri-ModeEthernetMACWrapperv1.

74www.

xilinx.

comApril19,2010ProductSpecificationEthernet1000BASE-XPortFigure3illustratesatypicalapplicationforasingleEthernetMAC.

ThePHYsideoftheMACiscon-nectedtoaRocketIOGTPorGTXtransceiver,whichinturnisconnectedtoanexternaloff-the-shelfGBICorSFPopticaltransceiver.

The1000BASE-XlogiccanbeoptionallyprovidedbytheEthernetMAC,asdisplayed.

1000BASE-XfunctionalityisdemonstratedintheHDLexamplesprovidedwiththeexampledesign.

TheclientsideoftheEthernetMACisshownconnectedtothe10Mbps,100Mbps,1GbpsEthernetFIFO(deliveredwiththeexampledesign)tocompleteasingleGigabitEthernetport.

Thisportiscon-nectedtoaSwitchorRoutingmatrix,whichcancontainseveralportsX-RefTarget-Figure3Figure3:Typical1000BASE-XApplicationEthernetMACRocketIOTransceiverMAC1000BASE-XPCS/PMAOpticalFiberPMARXP/RXNGBICorSFPOpticalTransceiverTXP/TXNSwitchorRouter1Gbps10Mbps,100Mbps,1GbpsEthernetFIFODS550April19,2010www.

xilinx.

com5ProductSpecificationVirtex-5FPGAEmbeddedTri-ModeEthernetMACWrapperv1.

7ExampleDesignOverviewFigure4illustratesthemajorfunctionalblocksoftheEthernetMACexampledesign.

AllillustratedcomponentsareprovidedinHDL,withtheexceptionoftheEthernetMACcomponent.

X-RefTarget-Figure4Figure4:ExampleDesignEmbeddedEthernetMACWrapperFPGAFabricClockCircuitryPhysicalI/F(GMII/MII,RGMII,orRocketIOPhysicalI/F(GMII/MII,RGMII,orRocketIO)EMAC1HostInterfaceEMAC0EmbeddedEthernetMACPhysicalInterfacecomponent_name_blockcomponent_name_example_designAddressSwapModuleAddressSwapModule10M/100M/1GEthernetFIFO10M/100M/1GEthernetFIFOClientInterfacecomponent_name_locallinkTxClientFIFORxClientFIFOTxClientFIFORxClientFIFOLocalLinkInterfaceLocalLinkInterfaceVirtex-5FPGAEmbeddedTri-ModeEthernetMACWrapperv1.

76www.

xilinx.

comApril19,2010ProductSpecificationEthernetMACExampleDesignTheexampledesignisarrangedforquickadaptationandcanbedownloadedontoanFPGAtoprovidearealhardwaretestenvironment.

Inaddition,alltheclockmanagementlogicrequiredtooperatetheEthernetMACanditsexampledesignisprovided.

DCMs,BUFGs,andsoforthareinstantiatedasrequired.

Thedataisloopedbackattheclientinterface,enablingtheEthernetMACtobequicklyconnectedtoaprotocoltester—framesinjectedintotheEthernetMACPHYReceiveportarerelayedbackthroughtheEthernetMACandoutthroughtheEthernetMACsPHYTransmitport.

Usingthismethod,theyarereceivedbackattheprotocoltester.

ThedesignincludesanAddressSwappingModuleandaFIFO.

FramesreceivedbytheEthernetMACarepassedthroughtheReceivesideoftheFIFO.

DatafromtheReceivesideoftheFIFOispassedintotheAddressSwapModuleandthenontotheTransmitsideoftheFIFOusingaLocalLinkinterface.

TheTransmitFIFOqueuesframesfortransmissionandconnectsdirectlytotheclientsideTransmitinterfaceoftheEthernetMAC.

AddressSwapModuleTheAddressSwapModuleswitchestheDestinationAddressandSourceAddresswithinthereceivedMACframe.

Usingthismethod,framesreceivedfromalinkpartner,forexampleaprotocoltester,arerelayedbacktothecorrectDestinationAddress.

10Mbps,100Mbps,1GbpsEthernetFIFOThe10Mbps,100Mbps,1GbpsEthernetFIFOisawrapperfilearoundtheReceiveandTransmitFIFOcomponents.

Thesecomponentscanbeusedinmorecomplexclientapplications,asillustratedinFigures2and3.

TousetheFIFOs,thecomponent_name_locallinkcomponentcanbeinstantiatedintheuserdesign.

ReceiveClientFIFOTheReceive(Rx)ClientFIFO,a4k-byteFIFOimplementedinblockRAMs,canbeusedformorecom-plexclientapplicationsandcanbeconnecteddirectlytotheRxClientInterfaceoftheEthernetMAC.

TheRxClientprovidesaLocalLinkconnectionfortheuser.

TheFIFOoperatesatallEthernetspeedssupportedbytheEthernetMAC.

TheFIFOdropsallframesmarkedasbadfromtheEthernetMACsothatonlyerror-freeframesarepassedtotheEthernetclient.

TransmitClientFIFOTheTransmit(Tx)ClientFIFO,a4k-byteFIFOimplementedinblockRAMs,canusedformorecomplexclientapplicationsandcanbeconnecteddirectlytotheTxClientInterfaceoftheEthernetMAC.

TheTxClientFIFOprovidesaLocalLinkconnectionfortheuser.

TheFIFOoperatesatallEthernetspeedssupportedbytheEthernetMAC.

TheFIFOiscapableofhalf-duplexre-transmission.

Forthisreason,ifacollisionoccursonthemedium,theEthernetMACindicatesacollisionontheTxClientinterfaceandtheFIFOautomaticallyre-queuestheframeforre-transmission.

DS550April19,2010www.

xilinx.

com7ProductSpecificationVirtex-5FPGAEmbeddedTri-ModeEthernetMACWrapperv1.

7EthernetMACWrapperTheEthernetMACwrapperfileinstantiatesthefullEthernetMACprimitive.

ForoneorbothEthernetMACs(EMAC0/EMAC1),thefollowingapplies:Allunusedinputportsontheprimitivearetiedtotheappropriatelogiclevel;allunusedoutputportsareleftunconnected.

TheEthernetMACattributesaresetbasedonoptionsselectedintheCOREGeneratorsoftware.

Onlyusedportsareconnectedtotheportsofthewrapperfile.

ThissimplifiedwrappershouldbeusedastheinstantiationtemplatefortheEthernetMACincus-tomerdesigns.

PhysicalI/FAnappropriatePhysicalInterfaceisprovidedforeachselectedEMAC0/EMAC1.

Thisinterfacecon-nectsthephysicalinterfaceoftheEthernetMACblocktotheI/OoftheFPGA.

Asrequired,thefollow-ingcomponentsareprovided:ForGMII/MII,thiscomponentcontainsInput/Outputblock(IOB)buffersandIOBflip-flops.

ForRGMII,thiscomponentcontainscontainIOBbuffers,IOBDouble-DataRateflip-flopsandIODELAYelementstoaligntheincomingdatawiththereceiverclock.

AnIODELAYelementisalsousedtodelaythetransmittedclockinRGMIIV2.

0.

For1000BASE-XPCS/PMAorSGMII,thiscomponentinstantiatesandconnectsaRocketIOGTPorGTXtransceiver.

Virtex-5FPGAEmbeddedTri-ModeEthernetMACWrapperv1.

78www.

xilinx.

comApril19,2010ProductSpecificationDeviceUtilizationThefollowingsectionsprovideapproximatedevice-utilizationfiguresforcommonconfigurationsoftheEthernetMACanditsexampledesign:1GbpsOnlyOperationTri-SpeedOperation100Mbpsor10MbpsOperationOfinterestistheutilizationofclockresources,specificallytheglobalclockusage(BUFGs),whichshouldinfluencetheselectionoftheinterfacetype.

Notethattheseclockresourcefiguresdonotcon-sideranyclockthatcanbeusedfortheHostInterface.

1GbpsOnlyOperationTable1definesapproximateutilizationfiguresforcommonconfigurationsoftheEthernetMACanditsexampledesignfor1Gbpsoperation.

Table1:DeviceUtilizationfor1GbpsOperationParameterValuesDeviceResourcesPhysicalInterfaceEthernetMACUsageLUTsRegisters18KBlockRAMsBUFGsDCMsGMIISingleEMAC3804504211.

TheseimplementationsuseIDLEAYelements,whichrequirea200MHzreferenceclockfortheassociatedIDELAYCTRL.

Therefer-enceclock'sBUFGisnotaccountedfor.

0BothEMACs7608808310RGMII1.

3SingleEMAC3804604210BothEMACs7609008310RGMII2.

0SingleEMAC3804604210BothEMACs7609008310SGMIISingleEMAC390440410BothEMACs7808708101000BASE-X(8-bitclient)SingleEMAC390440410BothEMACs7808708101000BASE-X(16-bitclient)SingleEMAC370560431BothEMACs7301120831DS550April19,2010www.

xilinx.

com9ProductSpecificationVirtex-5FPGAEmbeddedTri-ModeEthernetMACWrapperv1.

7Tri-SpeedOperationTable2definesapproximateutilizationfiguresforcommonconfigurationsoftheEthernetMACanditsexampledesign10Mbps,100Mbps,or1Gbpsoperation.

Table2:DeviceUtilizationforTri-SpeedOperationParameterValuesDeviceResourcesPhysicalInterfaceEthernetMACUsageLUTsRegisters18KBlockRAMsBUFGsRCLKsGMII/MII(standardclocking)SingleEMAC4004804511.

TheseimplementationsuseIDLEAYelements,whichrequirea200MHzreferenceclockfortheassociatedIDELAYCTRL.

Therefer-enceclock'sBUFGisnotaccountedfor.

0BothEMACs79095081010GMII/MII(withclockenable)SingleEMAC4005004210BothEMACs7909808410GMII/MII(withbytePHY)SingleEMAC4105104210BothEMACs8109908410RGMII1.

3(standardclocking)SingleEMAC4004904410BothEMACs7909708810RGMII1.

3(withclockenable)SingleEMAC4005104210BothEMACs79010008410RGMII2.

0(standardclocking)SingleEMAC4004904410BothEMACs7909708810RGMII2.

0(withclockenable)SingleEMAC4005104210BothEMACs79010008410SGMIISingleEMAC470620521BothEMACs93012201032Virtex-5FPGAEmbeddedTri-ModeEthernetMACWrapperv1.

710www.

xilinx.

comApril19,2010ProductSpecification100Mbpsor10MbpsOperationTable3providesapproximateutilizationfiguresforcommonconfigurationsoftheEthernetMACanditsexampledesignfor10Mbpsor100Mbpsoperation.

Forallotherinterfaces,seeTri-SpeedOperation.

OrderingInformationTheEthernetMACwrapperisprovidedundertheEndUserLicenseAgreementandcanbegeneratedusingCOREGeneratorsoftwarev12.

1andhigher.

TheCOREGeneratorsoftwareisshippedwithXilinxISEDesignSuiteSeriesDevelopmentsoftware.

InISEv12.

1andlater,alicensekeyisnotrequiredtoaccesstheIP.

ToaccessthewrapperinISEv11.

4andolder,anocostfulllicensemustbeobtainedfromXilinx.

Seetheproductpage:www.

xilinx.

com/products/ipcenter/V5_Embedded_TEMAC_Wrapper.

htmContactyourlocalXilinxsalesrepresentativeforpricingandavailabilityofotherXilinxLogiCOREIPmodulesandsoftware.

InformationonadditionalLogiCOREIPmodulesisavailableontheXilinxIPCenter.

RevisionHistoryTable3:DeviceUtilizationfor10Mbps,100MbpsOperationParameterValuesDeviceResourcesPhysicalInterfaceEthernetMACUsageLUTsRegisters18KBlockRAMsBUFGsMII(standardclocking)SingleEMAC40046044BothEMACs78092088MII(withclockenable)SingleEMAC39048042BothEMACs78095084MII(withbytePHY)SingleEMAC40048042BothEMACs80096084DateVersionRevision10/23/061.

0InitialXilinxrelease.

2/15/072.

0Coreupdatedtoversion1.

2;Xilinxtools9.

1i.

8/8/052.

2Coreupdatedtoversion1.

3;Xilinxtools9.

2,IUSv5.

8.

3/24/083.

0Coreupdatedtoversion1.

4;Xilinxtools10.

1;Virtex-5FXTFPGAsupport.

9/19/084.

0Coreupdatedtoversion1.

5;Virtex-5TXTFPGAsupport.

4/24/095.

0Coreupdatedtoversion1.

6andXilinxtoolsupdatedtoversion11.

1.

4/9/106.

0Coreupdatedtoversion1.

7andXilinxtoolsupdatedtoversion12.

1.

DS550April19,2010www.

xilinx.

com11ProductSpecificationVirtex-5FPGAEmbeddedTri-ModeEthernetMACWrapperv1.

7NoticeofDisclaimerXilinxisprovidingthisproductdocumentation,hereinafter"Information,"toyou"ASIS"withnowarrantyofanykind,expressorimplied.

XilinxmakesnorepresentationthattheInformation,oranyparticularimplementationthereof,isfreefromanyclaimsofinfringement.

YouareresponsibleforobtaininganyrightsyoumayrequireforanyimplementationbasedontheInformation.

Allspecificationsaresubjecttochangewithoutnotice.

XILINXEXPRESSLYDISCLAIMSANYWARRANTYWHATSOEVERWITHRESPECTTOTHEADEQUACYOFTHEINFORMATIONORANYIMPLEMENTATIONBASEDTHEREON,INCLUDINGBUTNOTLIMITEDTOANYWARRANTIESORREPRESENTATIONSTHATTHISIMPLEMENTATIONISFREEFROMCLAIMSOFINFRINGEMENTANDANYIMPLIEDWARRANTIESOFMERCHANTABILITYORFITNESSFORAPARTICULARPURPOSE.

Exceptasstatedherein,noneoftheInformationmaybecopied,reproduced,distributed,republished,downloaded,displayed,posted,ortransmittedinanyformorbyanymeansincluding,butnotlimitedto,electronic,mechanical,photocopying,recording,orotherwise,withoutthepriorwrittenconsentofXilinx.

- specificationo3o4o5相关文档

- Slowo3o4o5

- Insertiono3o4o5

- populationo3o4o5

- packageo3o4o5

- Temperatureo3o4o5

- capacitanceo3o4o5

RFCHOST - 洛杉矶CN2 GIA VPS季付23.9美元起 100Mbps带宽

RFCHOST,这个服务商我们可能有一些朋友知道的。不要看官网是英文就以为是老外服务商,实际上这个服务商公司在上海。我们实际上看到的很多商家,有的是繁体,有的是英文,实际上很多都是我们国人朋友做的,有的甚至还做好几个品牌域名,实际上都是一个公司。对于RFCHOST商家还是第一次分享他们家的信息,公司成立大约2015年左右。目前RFCHOST洛杉矶机房VPS正进行优惠促销,采用CN2优化线路,电信双...

cloudcone:特价便宜VPS补货通知贴,SAS或SSD低价有磁盘阵列,SAS或SSD raid10 硬盘

cloudcone经常性有特价促销VPS放出来,每次的数量都是相当有限的,为了方便、及时帮助大家,主机测评这里就做这个cloudcone特价VPS补货专题吧,以后每次放货我会在这里更新一下日期,方便大家秒杀!官方网站:https://cloudcone.com/预交费模式,需要充值之后方可使用,系统自动扣费!信用卡、PayPal、支付宝,均可付款购买!为什么说cloudcone值得买?cloudc...

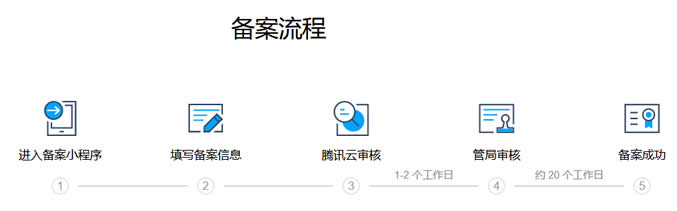

个人网站备案流程及注意事项(内容方向和适用主机商)

如今我们还有在做个人网站吗?随着自媒体和短视频的发展和兴起,包括我们很多WEB2.0产品的延续,当然也包括个人建站市场的低迷和用户关注的不同,有些个人已经不在做网站。但是,由于我们有些朋友出于网站的爱好或者说是有些项目还是基于PC端网站的,还是有网友抱有信心的,比如我们看到有一些老牌个人网站依旧在运行,且还有新网站的出现。今天在这篇文章中谈谈有网友问关于个人网站备案的问题。这个也是前几天有他在选择...

o3o4o5 com为你推荐

-

郭吉军二战中受害最大的国家?网络明星想知道3大网络歌手是谁?网站联盟怎样进入网站联盟天天酷跑刷金币天天酷跑怎么刷金币?虚拟机软件下载谁有虚拟机软件的网址要好用的虚拟机软件下载求一个免费虚拟机软件!!!请发送下载网站给我blogcnblogcn网页无法正常显示,直接跳转http://www.7t7t.com/7?如何清理ie缓存怎么清理IE的缓存网站排名靠前怎样才能做好一个网站?让网站排名靠前?新手求解office2007简体中文版如何激活office2007 professional简体中文专业版啊?