WP411_06_011112avtt4.com

avtt4.com 时间:2021-03-19 阅读:()

WP411(v1.

0)January30,2012www.

xilinx.

com1Copyright2012Xilinx,Inc.

Xilinx,theXilinxlogo,Artix,ISE,Kintex,Spartan,Virtex,Zynq,andotherdesignatedbrandsincludedhereinaretrademarksofXilinxintheUnitedStatesandothercountries.

ThepurposeofaPowerDistributionNetwork(PDN)istoprovidepowertoelectricaldevicesinasystem.

Eachdeviceinasystemnotonlyhasitsownpowerrequirementsforitsinternaloperation,butalsoarequirementfortheinputvoltagefluctuationofthatpowerrail.

ForXilinxKintex-7andVirtex-7FPGAs,theanalogpowerrailshaveaninputvoltagefluctuationrequirementofnotmorethan10mVpeak-to-peakfromthe10kHztothe80MHzfrequencyrange.

Theself-generatedvoltagefluctuationonthepowerrailsisafunctionoffrequencyandcanbedescribedbyOhm'sLaw:Voltage(frequency)=Current(frequency)*Self-Impedance(frequency).

Thus,iftheuserdeterminestheself-impedance(frequency)andknowsthecurrent(frequency)ofthePDN,thenthevoltage(frequency)canbedetermined.

Theself-impedance(frequency)caneasilybedeterminedbysimulatingthefrequencydomainself-impedanceprofileofthePDNandis,thus,thesubjectofthiswhitepaper.

WhitePaper:Kintex-7andVirtex-7FPGAsWP411(v1.

0)January30,2012SimulatingFPGAPowerIntegrityUsingS-ParameterModelsBy:HanyFahmyandColinWarwickofAgilentTechnologies,Inc.

andJackCarrel,RayAnderson,HarryFu,andRomiMayderofXilinx,Inc.

2www.

xilinx.

comWP411(v1.

0)January30,2012OverviewOverviewBeforesimulatingthefrequencydomainself-impedanceprofilesofaPDN,itisimportanttoestablishexpectationsforthesimulationresults.

Todothis,anunderstandingofthefundamentalconceptsmustbeattained:Series-ResonanceCircuitandImpedanceMinimumsParallel-ResonanceCircuitandImpedanceMaximumsFrequencyComponentsofElectricalSignalsS-ParameterModelvs.

LumpedRLCModelforDecouplingCapacitorsSeries-ResonanceCircuitandImpedanceMinimumsAseries-resonantcircuitisdefinedbyacapacitor(C)andinductor(L)thatareconnectedinseries.

WhentheXC(capacitivereactance)andXL(inductivereactance)areequalinmagnitudeandoppositeinphase,thecurrentisatmaximum.

Thisconditiongivesrisetoanimpedanceminimum.

Thefrequencyatwhichthisequalityoccursiscalledtheseries-resonantfrequencyandisdescribedbyEquation1:Equation1Acommonseries-resonantcircuitisformedbythecapacitance(C)andtheparasiticinductance(L)ofagivencapacitormountedonaprintedcircuitboard.

Figure1showstheschematiccircuitrepresentationwhileFigure2showsthefrequencydomainimpedanceprofile.

X-RefTarget-Figure1Figure1:Series-ResonantComponentsofaPCB-MountedCapacitorX-RefTarget-Figure2Figure2:Frequency-DomainImpedanceProfileofPCB-MountedCapacitorf12πLC-=Series-ResonantCircuitP3Num=3P4Num=4CC2C=C_PCB_CapacitanceRR3R=R_PCB_CapacitanceLL2L=L_PCB_Cap_InductanceWP411_01_0124120.

00.

00.

20.

40.

60.

81.

01.

21.

41.

60.

10.

20.

30.

40.

5Freq,GHzImpedanceMinimumSeriesResonantCircuitSeries_Resonance0.

6WP411_02_1110110.

70.

80.

91.

0OverviewWP411(v1.

0)January30,2012www.

xilinx.

com3Parallel-ResonanceCircuitandImpedanceMaximumsAparallelanti-resonantcircuitisdefinedbyacapacitor(C)andinductor(L)thatareconnectedinparallel.

WhentheXC(capacitivereactance)andXL(inductivereactance)areequalinmagnitudeandoppositeinphase,thereactivebranchcurrentsarealsoequalinmagnitudeandoppositeinphase.

Thisgivesrisetoaminimumtotalcurrentandthus,amaximumtotalimpedanceiscreated.

Thefrequencyatwhichthisconditionoccursiscalledtheparallelanti-resonantfrequencyandisdescribedbyEquation2:Equation2Acommonparallelanti-resonantcircuitisoneformedbythediecapacitanceandpackageinductance.

Figure3showsaschematiccircuitrepresentationwhileFigure4showsthefrequencydomainimpedanceprofile.

X-RefTarget-Figure3Figure3:ParallelAnti-ResonantComponentsofDieandPackagePropertiesX-RefTarget-Figure4Figure4:Frequency-DomainImpedanceProfileofDieandPackagePropertiesf12πLC-=ParallelAnti-ResonantCircuitP1Num=1P2Num=2WP411_03_112411RR1R=R_Die_CapacitanceRR2R=R_Package_InductanceLL1L=L_Package_InductanceCC1C=C_Die_Capacitance0.

00.

00.

10.

20.

30.

40.

50.

60.

70.

80.

10.

20.

30.

40.

5Freq,GHzImpedanceMaximumParallelAnti-resonantCircuitParallel_Anti_Resonance0.

6WP411_04_1110110.

70.

80.

91.

04www.

xilinx.

comWP411(v1.

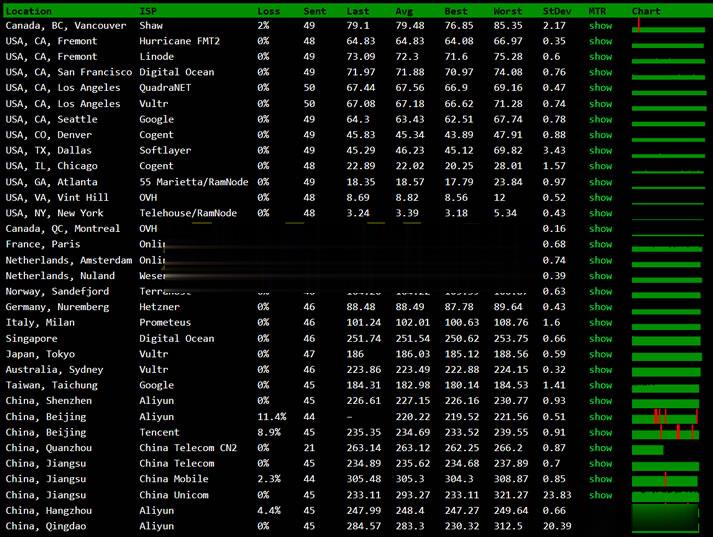

0)January30,2012OverviewFrequencyComponentsofElectricalSignalsThefrequencydomaincurrentprofileofVCCO(f)isshowninFigure5andFigure6assimulatedattheBGApowerballsoftheXilinxVirtex-7XC7VX485TFPGAintheFFG1761pinpackage.

Intheexample,thesimulationisrunningamemoryinterfaceat1.

866Gb/swithaPRBS15datapattern.

ThepowerspectraldensityofVCCO(t)iswide-banded,extendingfrom10MHzuptothe10GHz.

Asthedatatrafficpatternandactivitychange,thesimulationsdemonstratethatthedominantfrequencycomponentsofthepowerspectraldensityalsochange.

Therefore,thesimulationsshowthatPDNnoiseisawide-bandphenomenon;PDNsimulationsmust,therefore,berunoverawide-bandfrequencyrange.

X-RefTarget-Figure5Figure5:MemoryInterfaceSimulationActivityPatterns0.

00.

10.

20.

30.

40.

50.

60.

7Freq,HzFrequencySpectrumSSTL15CurrentSSTL15HPIOVCCOCurrentmag(FS_Kirtex_7_SSTL15_Current),mAWP411_05_011112IE9IE8IE7IE10051015202530Freq,HzFrequencySpectrumDDR3DieInputmag(FS_Kintex_7_SSTL15),mV-0.

50.

00.

51.

01.

52.

0DDR3_Die_Input_Eye_Diagram,VoltsIE9IE8IE7IE10-10-5051015202530Time,nsecKintex_7_SSTL15_Current,mA7080904050600012030100DDR3DieInput1,866Mb/sTime,nsec0.

70.

80.

90.

40.

50.

60.

00.

10.

20.

31.

01.

1OverviewWP411(v1.

0)January30,2012www.

xilinx.

com5Becausethepowerspectraldensityisofawideband,thefrequencydomainself-impedanceprofilemustbesimulatedoverawiderange.

Below1kHz,thevoltageregulatormodule(VRM)dominatesthefrequencydomainself-impedanceprofile.

Above10GHz,theon-diecapacitancedominatestheimpedanceprofile.

Thus,Xilinxrecommendsrunningthesimulationsfrom1kHzto10GHz.

S-ParameterModelvs.

LumpedRLCModelforDecouplingCapacitorsAsacomparisonbetweenusinglumpedRLCcircuitsandS-parameterstorunPDNsimulations,thedecouplingcapacitorsportionofthePDNcircuitisexaminedfirst.

Inthissimulation,anattemptismadetocurve-fitanS-parametermodelforcommonX5RcapacitorsinthefollowingEIAcasesizes:0201,0402,0603,0805,1206,and1610.

Aftermatchingthecapacitivereactanceandtheseries-resonantfrequencygiveninEquation1,thepercentageerroroftheinductivereactanceat100MHzismeasured.

Thesesimulationsaredoneatroomtemperature(25°C)withnoappliedDCbias.

Figure7throughFigure9showthecircuitschematicrepresentations.

Figure10andFigure11showthesimulationresults.

X-RefTarget-Figure6Figure6:SimulationTestSetupTTLPCPCGCGCPUPDPDPUVINI/OODigOPRBS15K7325TFF900SSTL15HPIODDR31.

86Gb/sDQPin40ΩImpedance3InchTraceDDR3PackageParasiticsWP411_06_011112VtPRBSVPRBS1PRBSIBIS_OIBIS1IBIS_IOIBIS4SLINTL1Subst="SSub1"W=5.

0milL=3000.

0milLL1L=1.

38nHR=0.

25656CC1C=0.

33pFDDR3DieInputEye_ProbeEye_Probe1V_DCSRC1VDC=1.

5VV_DCSRC2VDC=1.

5VPowerOutput++++––6www.

xilinx.

comWP411(v1.

0)January30,2012OverviewX-RefTarget-Figure7Figure7:DecouplingCapacitorsSimulation,SchematicRepresentation1X-RefTarget-Figure8Figure8:DecouplingCapacitorsSimulation,SchematicRepresentation2X-RefTarget-Figure9Figure9:DecouplingCapacitorsSimulation,SchematicRepresentation3DataSheetCeramic02011uF4VX5RWP411_07_013012TermTerm1Num=1Z=50Ω+–TermTerm2Num=2Z=50ΩS2PSNP1LL2L=320pHR=10mΩCC2C=0.

69uF+–TermTerm3Num=3Z=50Ω+–TermTerm4Num=4Z=50Ω+–DataSheetCeramic04024.

7uF4VX5RTermTerm16Num=16Z=50Ω+–TermTerm15Num=15Z=50ΩS2PSNP4LL3L=500pHR=8mΩCC3C=3.

7uF+–TermTerm14Num=14Z=50Ω+–TermTerm13Num=13Z=50Ω+–DataSheetCeramic060322uF4VX5RWP411_08_013012TermTerm12Num=12Z=50Ω+–TermTerm11Num=11Z=50ΩS2PSNP3LL4L=800pHR=4mΩCC4C=14uF+–TermTerm10Num=10Z=50Ω+–TermTerm9Num=9Z=50Ω+–DataSheetCeramic080522uF4VX5RTermTerm17Num=17Z=50Ω+–TermTerm18Num=18Z=50ΩS2PSNP5LL6L=800pHR=3.

5mΩCC6C=14uF+–TermTerm19Num=19Z=50Ω+–TermTerm20Num=20Z=50Ω+–DataSheetCeramic1206100uF4VX5RWP411_09_013012TermTerm21Num=21Z=50Ω+–TermTerm22Num=22Z=50ΩS2PSNP6LL5L=1,360pHR=2.

75mΩCC5C=50uF+–TermTerm23Num=23Z=50Ω+–TermTerm24Num=24Z=50Ω+–DataSheetCeramic1210100uF4VX5RTermTerm32Num=25Z=50Ω+–TermTerm31Num=26Z=50ΩS2PSNP8LL7L=1,200pHR=1.

9mΩCC7C=60uF+–TermTerm30Num=27Z=50Ω+–TermTerm29Num=28Z=50Ω+–OverviewWP411(v1.

0)January30,2012www.

xilinx.

com7X-RefTarget-Figure10Figure10:SimulationResults(EIACaseSizes0201/0603/1206)X-RefTarget-Figure11Figure11:SimulationResults(EIACaseSizes0402/0805/1210)1E-21E51E61E71E81E96E91E-111E1Freq,HzImpedanceMagnitude0201mag(Ceramic_0201_1uF_RLC)mag(Ceramic_0201_1uF_S)1E51E61E71E81E99580655035200-10-25-40-55-70-85-100Freq,HzImpedancePhase0201phase(Ceramic_0201_1uF_RLC),degphase(Ceramic_0201_1uF_S),deg1E-21E-31E51E61E71E81E96E91E-111E1Freq,HzImpedanceMagnitude0603mag(Ceramic_0603_1uF_RLC)mag(Ceramic_0603_1uF_S)1E51E61E71E81E99580655035200-10-25-40-55-70-85-100Freq,HzImpedancePhase0603phase(Ceramic_0603_1uF_RLC),degphase(Ceramic_0603_1uF_S),deg1E-21E-31E51E61E71E81E96E91E-111E1Freq,HzImpedanceMagnitude1206mag(Ceramic_1206_1uF_RLC)mag(Ceramic_1206_1uF_S)1E51E61E71E81E99580655035200-10-25-40-55-70-85-100Freq,HzImpedancePhase1206phase(Ceramic_1206_1uF_RLC),degphase(Ceramic_1206_1uF_S),degWP411_10_0116121E-31E-21E51E61E71E81E96E91E-111E1Freq,HzImpedanceMagnitude0402mag(Ceramic_0402_4_7uF_RLC)mag(Ceramic_0402_4_7uF_RLC)1E51E61E71E81E99580655035200-10-25-40-55-70-85-100Freq,HzImpedancePhase0402phase(Ceramic_0402_4_7uF_RLC),degphase(Ceramic_0402_4_7uF_S),deg1E-21E-31E51E61E71E81E96E91E-111E1Freq,HzImpedanceMagnitude0805mag(Ceramic_0805_22uF_RLC)mag(Ceramic_0805_22uF_S)1E51E61E71E81E99580655035200-10-25-40-55-70-85-100Freq,HzImpedancePhase0805phase(Ceramic_0805_22uF_RLC),degphase(Ceramic_0805_22uF_S),deg1E-21E-31E51E61E71E81E96E91E-111E1Freq,HzImpedanceMagnitude1210mag(Ceramic_1210_100uF_RLC)mag(Ceramic_1210_100uF_S)1E51E61E71E81E99580655035200-10-25-40-55-70-85-100Freq,HzImpedancePhase1210phase(Ceramic_1210_100uF_RLC),degphase(Ceramic_1210_100uF_S),degWP411_11_0116128www.

xilinx.

comWP411(v1.

0)January30,2012OverviewAsummaryofthedataisshownbelowinTable1:ItisknownthatthetypicalcapacitormanufacturerspecifiesthecapacitanceofacapacitorwithzeroDCbiasand0.

5VrmsACvoltage,whilethes-parametermodelsaretypicallymeasuredwitha0dbmACsignal.

InS-ParameterModelsforDecouplingCapacitorssection,thevariousmethodsforgeneratingtheS-parametermodelofacapacitorareexamined.

S-ParameterModelsforDecouplingCapacitorsAtfirstglance,themeasurementofthecapacitor'sPDNimpedanceprofile(theimpedancewithrespecttofrequency)seemstobeasimpletask,butseveralsubtledetailsarerequiredtoensurethemeasureddataisaccurate.

ThefrequencydomainmeasurementisusuallyaccomplishedbyutilizingaVectorNetworkAnalyzer(VNA).

TheobviousmethodistoprobethePDNmakinganS11measurement,andthenconvertthemeasureds-parameterstoimpedancebymeansoftheEquation3relationship:Equation3Animpedancemeasurementusingthismethod,however,hasinherentinaccuraciesduetothefactthattheinstrumenttypicallyhasa50ΩinputimpedanceandthePDNhasaverylowimpedance(typicallyinthemilliohmrange).

TheaccuracyofthemeasuredVNAdatainherentlyhaserrorsbecausethetypicaluncertaintyofS11(whenrho,thereflectioncoefficient,isnear1)canbeinthe1%–2%range.

Thisequatestoanimpedanceuncertaintyinthe0.

3Ω-to-0.

4Ωrange.

IfPDNimpedancesinthemilliohmrangearebeingmeasured,itquicklybecomesobviousthatthedesiredimpedancemeasurementislostinthemeasurementuncertainty.

AsecondfactortoconsideristhattheinductiveparasiticsoftheprobingarrangementcaneasilyexceedthevalueoftheDUTinductance.

Thereisnoeasywaytobackouttheprobeparasiticsfromthemeasureddata.

Fortunately,anS21measurementisagoodalternativetoanS11measurementtodeterminethePDNimpedance.

Inthismethod,itisfoundthatZdut=25(S21).

Withthismeasurementtechnique,thesolderofthedecouplingcapacitorisincludedinthemeasurement.

ByutilizingtheS21measurement,theimpedanceuncertaintyisreducedintothe10s-of-milliohmsrange.

Inaddition,theprobeparasiticsareinserieswith50ΩasopposedtobeinginserieswiththeDUTimpedance,whichreducestheireffectstonearnegligiblelevels.

Foramorecompletediscussionofthistopic,seeAccuracyImprovementsofPDNImpedanceMeasurementsintheLowtoMiddleFrequencyTable1:SummaryofResultData,DecouplingCapacitorsSimulationSizeCapacitance(F)ImpedanceMagnitude@100MHzSeries-ResonantFrequencyEIACodeS-ParameterDataSheet%ErrorS-ParameterRLCModel%Error12106010066.

70.

2090.

751259.

3600KHz120650100100.

00.

2550.

845231.

4700KHz805142257.

10.

180.

501178.

31.

5MHz603142257.

10.

1780.

501181.

51.

5MHz4023.

74.

727.

00.

150.

313108.

73.

5MHz2010.

69144.

90.

1290.

19853.

510MHzZdut501S11+1S11–-=OverviewWP411(v1.

0)January30,2012www.

xilinx.

com9RangepresentedatDesignCon2010byIstvanNovakofSUNMicrosystemsandYasuhiroMoriandMikeRessoofAgilentTechnologies(http://www.

home.

agilent.

com/upload/cmc_upload/All/DC10_ID2696_Novak-Mori-Resso.

pdf).

RLCModelsforDecouplingCapacitorDecouplingcapacitorsareoftencharacterizedbyvendorsbymeansofthreeparameters:R(resistance),L(inductance),andC(capacitance).

TheCparameteristhedecap'sintrinsiccapacitance;theLisitsintrinsicinductance;andtheRistheESRofthedecouplingcapacitor.

WhenthissimpleRLCmodelforadecouplingcapacitorisutilizedinasimulationalongwithagoodPDNmodel,themountinginductanceandspreadinginductanceassociatedwiththepackageorPCBcombineswiththedecap'sintrinsicinductancetoeffectivelymodeltheloopinductance.

Thisloopinductanceplusthepackageinductanceresonateswiththediecapacitancetoformaparallelanti-resonantcircuitwithauniqueimpedanceprofile.

SeriesRLCmodelsofdecouplingcapacitorsareeasytounderstand,andtheysimulatequicklyasbothfrequencydomainandtransientsimulationswithaminimumofissues.

Asnotedpreviously,theRLCvaluesforthemodelcancomefromavendor'sdatasheet;alternatively,theycanbederivedfrommeasureds-parameterdatabyfittingthevaluesofasimpleseriesRLCcircuittotheresponseofthes-parameters.

Insomecases,particularlyatlowfrequencies,thesimpleseriesRLCcircuitworksadequately.

However,whenitisrequiredtodeterminetheimpedanceprofileofaPDNaccuratelyoverawidebandwidthofDCtoseveralgigahertz,thingsusuallydonotworkoutsosimply.

TwomainissuesmakesimpleseriesRLCmodelsinadequateforaccuratePDNsimulations.

Duetothestackedlayersofthedecouplingcapacitorconstruction,thereisdistributedinductanceandresistanceintheZaxisoftheplatestack.

ThiscausestheLparameteroftheseriesRLCrepresentationtobefrequencydependent.

Inmostsimulators,thereisnofrequency-dependentLelement.

First,areasonablyaccurateseriesRLCmodelcanbeconstructedateitherlowfrequenciesorhighfrequencies,butcannotmodelbothsimultaneously.

Second,whileacomplexmulti-elementmodelcanbeconstructedtomoreaccuratelymodelthefrequency-dependentLeffect,suchmodelsareverydifficulttodesignandmanage.

Therefore,ratherthanuseasimpleseriesRLCcircuitthatisknowntobeinaccurateoverawidebandwidth,orattempttosynthesizeamorecomplexmulti-elementmodel,thesimulationworkdoneatXilinxsuggeststhatitismucheasierandmoreaccuratetoutilizeameasuredwidebands-parameterdecouplingcapacitormodelwhensimulatingPDNs.

Note:Ceramicdecouplingcapacitormodelsarestronglyvoltagedependent.

Therefore,itisimportanttoobtainthes-parametermodelfromthecapacitormanufacturerthathasbeenmeasuredattheoperatingvoltageofinterest—forbothDCandACvoltages.

10www.

xilinx.

comWP411(v1.

0)January30,2012RunningthePDNSimulationswiththeAgilentADS2011.

10RunningthePDNSimulationswiththeAgilentADS2011.

10Tosimulatethefrequencydomainself-impedanceprofileofaPowerDistributionNetwork,XilinxrecommendsusingtheAgilentADS2011softwarebundle.

Thissoftwarebundleprovidesthehigh-speed-digital(HSD)designerwithawiderangeoftools.

Everyaspectofthepowerintegrityproblemrequiresaspecifictechniqueforsolvingit.

Forexample,PDNanalysisrequiresthefollowing:1.

Truefrequency-domainsimulationofthePDNparallelanti-resonancesandseriesresonanceswithsolidS-parameterhandlingandassuranceof"PassivityandCausality"2.

Patentedconvolution(Kramers-Kronig)tobringfrequency-domainmodels(measurement-basedmodelsandEM-basedmodels)intothetimedomain(eyediagrams,BERcontours,andjitterdecomposition)3.

Usinganextractiontechnique,suchasMethod-of-Moment,whichhasexcellentaccuracyfromDCtoGHzrangePDNSimulationExampleInthissimulationexample,thesimulationperformedisthePDNoftheMGTAVCCandMGTAVTTanalogpowerrailsfortheXilinx7seriesXC7VX485TFPGAintheFFG1761pinpackage.

Twocasesaresimulatedhere.

Case1usesthePCBcapacitorslistedinTable2,whicharesimilartotherecommendedPCBcapsfortheXilinxVirtex-6devices.

Case2usesthePCBcapacitorsdescribedinTable3.

Figure12istheschematicforbothcases(1)and(2)listedabovefortheMGTAVCCandMGTAVTTpowerrails.

Forcase2(withnoPCBcapacitors),thereisstillonebulkcapacitormountedonthePCBspecifiedbythemanufacturerofthevoltageregulatormodule.

Table2:Case1CapacitorsQTYperGroupCapacitance(F)MGTAVCCMGTAVTTMGTVCCAUX4420.

0224400.

4722112214.

7Table3:Case2CapacitorsQTYperGroupCapacitance(F)MGTAVCCMGTAVTTMGTVCCAUX0000.

0220000.

4700010004.

7RunningthePDNSimulationswiththeAgilentADS2011.

10WP411(v1.

0)January30,2012www.

xilinx.

com11X-RefTarget-Figure12Figure12:PowerRailsSimulationSchematicRepresentationTermTerm13Num=13Z=50OhmTermTerm14Num=14Z=50OhmCC30C=22.

16nFS2PSNP105File="GRM155R61C223KA01_022uF_0402S2P"S2PSNP49File="T520V337M2R5ATE025.

s2p"S2PSNP111File="GRM152R60J474ME15_047_0402.

S2P"S2PSNP108File="GRM152R60J474ME15_047_0402.

S2P"S2PSNP107File="GRM152R60J474ME15_047_0402.

S2P"S2PSNP106File="GRM152R60J474ME15_047_0402.

S2P"S2PSNP109File="GRM188R61C105KA93_1uF_0603.

S2P"S2PSNP53File="GRM033C80G104KE19series(for_Fuji2_AVTT_AVCC).

s2p"S2PSNP52File="GRM033C80G104KE19series(for_Fuji2_AVTT_AVCC).

s2p"S2PSNP51File="GRM033C80G104KE19series(for_Fuji2_AVTT_AVCC).

s2p"S2PSNP50File="GRM033C80G104KE19series(for_Fuji2_AVTT_AVCC).

s2p"LL28L=25nHR=1mOhmV_DCSRC7Vdc=1.

2V+–S6PSNP48File="fga2034_485t_ff1761_031411_Avcc_G10.

s6p"S2PSNP104File="GRM155R61C223KA01_022uF_0402.

S2P"S2PSNP105File="GRM155R61C223KA01_022uF_0402.

S2P"S2PSNP105File="GRM155R61C223KA01_022uF_0402.

S2P"RR8R=10mOhmWP411_12_012212++––PackageCapacitorsVRMDieCapacitorsS2PSNP112File="GRM188R60J475KE19_47uF_0603.

S2P"S2PSNP113File="GRM188R60J475KE19_47uF_0603.

S2P"S2PSNP110File="GRM188R61C105KA93_1uF_0603.

S2P"S20PSNP47File="VC7203_MGTAVCC_092611_175001_S.

s20p"12www.

xilinx.

comWP411(v1.

0)January30,2012RunningthePDNSimulationswiththeAgilentADS2011.

10Figure13showthesimulationsresults.

Figure14showsthecompletesimulationtimeusingatypicallaptopcomputerrunningtheWindows-764-bitoperatingsystemisonly11.

68seconds!

Becausethesimulationresultsforbothcasesresultinalmostidenticalfrequencydomainself-impedanceprofilesfortheMGTAVCCandMGTAVTTpowerrails,andbecausetheMGTVCCAUXpowerrailhasaninternallowdropoutregulatorintegratedonthedie,similarperformancebetweenthetwocasesshouldbeexpected.

Asasimplereference,theimpedanceprofilesweresimulatedonacompetitivedevicewith0PCBcapacitorsbeyondthe1bulkPCBcapacitortypicallyrequiredbythevoltageregulatormanufacturer.

ProfilesrepresentingtheVCCH_GXBL0,VCCT_GXBL0,andVCCR_GXBL0powerrailswererun.

X-RefTarget-Figure13Figure13:PowerRailsSimulationResults1E31E41E51E61E71E81E91E10freq,HzMGTAVCC-MagnitudeTypicalCompetitormag(Competitor_PLL_Supply_With_PCB_Caps)mag(MGTAVCC_Die_Without_PCB_Caps)mag(MGTAVCC_Die_With_PCB_Caps)130012001100100090080070060050040030020010001E31E41E51E61E71E81E91E10freq,HzMGTAVCC-MagnitudeTypicalCompetitormag(Competitor_Tx_Rx_Supply_With_PCB_Caps)mag(MGTAVTT_Die_Without_PCB_Caps)mag(MGTAVTT_Die_With_PCB_Caps)13001200110010009008007006005004003002001000WP411_13_012212X-RefTarget-Figure14Figure14:CompleteSimulationTime,Windows-764-bitOSWP411_14_012212RunningthePDNSimulationswiththeAgilentADS2011.

10WP411(v1.

0)January30,2012www.

xilinx.

com13AscaneasilybeseeninthePDNprofilesofatypicalcompetitivedevice,theanalograilswouldhaveapeakimpedanceofwellover2ΩifthePCBcapswereremoved!

TransmitterHardwareMeasurementsFigure15throughFigure18containaseriesofeyediagramsat10.

3125Gb/susingtheQPLLand6.

25Gb/susingtheCPLLwithPRBS15datapatternmeasuredontheAgilentInfiniiumDCA-JWide-BandwidthOscilloscope.

ThisAgilent86100Cwiththe86108Aprecisionwaveformanalyzerhasbeenselectedtomakethesehardwaremeasurementsbecauseofthefollowingkeyattributes:1.

Highbandwidth,lownoise,andultra-lowresidualjitter2.

Simpleoneconnection"triggerless"operation3.

PLLcharacterizationincludingloopBW/jittertransfer4.

IntegratedhardwareclockrecoverwithadjustableloopBW/Peaking—exceedsindustrystandardsFigure15showstheeyediagramandassociatedjitterdecompositionwhenusingtheCPLLrunningat6.

25Gb/sforcase1.

Figure16showstheeyediagramandassociatedjitterdecompositionwhenusingtheCPLLrunningat6.

25Gb/sforcase2(noPCBcaps).

X-RefTarget-Figure15Figure15:Case1EyeDiagram,6.

25Gb/sWP411_15_01161214www.

xilinx.

comWP411(v1.

0)January30,2012RunningthePDNSimulationswiththeAgilentADS2011.

10Figure17showstheeyediagramandassociatedjitterdecompositionwhenusingtheQPLLrunningat10.

3125Gb/sforcase1.

Figure18showstheeyediagramandassociatedjitterdecompositionwhenusingtheQPLLrunningat10.

3125Gb/sforcase2(noPCBcaps).

X-RefTarget-Figure16Figure16:Case2EyeDiagram,6.

25Gb/sWP411_16_011612X-RefTarget-Figure17Figure17:Case1EyeDiagram,10.

3125Gb/sWP411_17_011612RunningthePDNSimulationswiththeAgilentADS2011.

10WP411(v1.

0)January30,2012www.

xilinx.

com15AsseeninthescopescreenshotsinFigure15throughFigure18,thetotaljitterisbothcases1and2iswithinthemeasurementtoleranceofthesetup.

Thus,hardwaremeasurementshaveconfirmedthesimulationresultsshowingthat0PCBcapsarerequiredforproperoperationofthetransmitter.

ReceiverMeasurementsTable4isasummaryofthereceiverhardwaremeasurementsbasedonaloopbacktestusingeyescan.

ThedatarecordedinTable4isthevoltageamplitudenoisewithalltransceiversinthepackagerunningasynchronously.

Asshownbythedata,thevoltageamplitudenoiseisthesameorlessafterallthePCBcapshavebeenremovedwhenusingeithertheCPLLortheQPLL.

Figure19isasummaryofthereceiver'sjittertoleranceanalysiswithalltransceiversinthepackagerunningasynchronouslyforbothcases1and2.

Asshownbythedata,thejittertoleranceisthesameorlessafterallthePCBcapshavebeenremoved.

Thejittertoleranceanalysiswasdoneat10-12BERthresholdandadatarateof10.

3125Gb/s.

X-RefTarget-Figure18Figure18:Case2EyeDiagram,10.

3125Gb/sWP411_18_011612Table4:ComparisonofVoltageAmplitudeNoisewith/withoutDecouplingCapsPLLCPLLQPLLBitRate6.

25Gb/s10.

3125Gb/sMGTAVCCAllCapsNoCapsAllCapsNoCapsMGTAVTTAllCapsNoCapsAllCapsNoCapsMGTVCCAUXAllCapsNoCapsAllCapsNoCaps%FullScale3.

6%3.

3%5.

0%4.

5%16www.

xilinx.

comWP411(v1.

0)January30,2012SummarySummaryPDNsimulations,confirmedbyhardwaremeasurements,haveshownthatnoPCBcapsbeyondthatrecommendedbythevoltageregulatormanufacturerarerequiredfortheMGTAVTT,MGTAVCC,andMGTVCCAUXpowerrailsforproperoperationofthetransceiversinXilinx'sKintex-7andVirtex-7devices.

WhilethePCBcapacitorsarenotneededforproperoperationofthetransceivers,however,properfilteringcanberequiredonthePCBtoachievetheinputvoltageripplenoisespecificationof10mVpeak-to-peak(10kHzto80MHz)whenmeasuredattheBGAballofthepackage.

Currently,XilinxhasseveralAgilentADSPowerIntegrityDesignKitsavailablefor7seriesFPGAsthatsupportalldevicepowersupplies(digitalandanalog).

ContactyourlocalXilinxfieldapplicationengineertoobtaintheseAgilentADSDesignKits.

Toobtaina30-dayfreelicenseofAgilentADS2011,pleasevisitthefollowinglink:https://software.

business.

agilent.

com/TrialLicense/TrialLicenseRequest.

aspxProdNum=W2200F-1U1-TRLX-RefTarget-Figure19Figure19:ComparisonofJitterTolerancewith/withoutDecouplingCaps100.

0010.

001.

000.

100AllCapsBER12NoCapsBER120.

010.

101.

00Frequency,MHzSI,UI10.

00100.

00WP411_xx_012212RevisionHistoryWP411(v1.

0)January30,2012www.

xilinx.

com17RevisionHistoryThefollowingtableshowstherevisionhistoryforthisdocument:NoticeofDisclaimerTheinformationdisclosedtoyouhereunder(the"Materials")isprovidedsolelyfortheselectionanduseofXilinxproducts.

Tothemaximumextentpermittedbyapplicablelaw:(1)Materialsaremadeavailable"ASIS"andwithallfaults,XilinxherebyDISCLAIMSALLWARRANTIESANDCONDITIONS,EXPRESS,IMPLIED,ORSTATUTORY,INCLUDINGBUTNOTLIMITEDTOWARRANTIESOFMERCHANTABILITY,NON-INFRINGEMENT,ORFITNESSFORANYPARTICULARPURPOSE;and(2)Xilinxshallnotbeliable(whetherincontractortort,includingnegligence,orunderanyothertheoryofliability)foranylossordamageofanykindornaturerelatedto,arisingunder,orinconnectionwith,theMaterials(includingyouruseoftheMaterials),includingforanydirect,indirect,special,incidental,orconsequentiallossordamage(includinglossofdata,profits,goodwill,oranytypeoflossordamagesufferedasaresultofanyactionbroughtbyathirdparty)evenifsuchdamageorlosswasreasonablyforeseeableorXilinxhadbeenadvisedofthepossibilityofthesame.

XilinxassumesnoobligationtocorrectanyerrorscontainedintheMaterialsortonotifyyouofupdatestotheMaterialsortoproductspecifications.

Youmaynotreproduce,modify,distribute,orpubliclydisplaytheMaterialswithoutpriorwrittenconsent.

CertainproductsaresubjecttothetermsandconditionsoftheLimitedWarrantieswhichcanbeviewedathttp://www.

xilinx.

com/warranty.

htm;IPcoresmaybesubjecttowarrantyandsupporttermscontainedinalicenseissuedtoyoubyXilinx.

Xilinxproductsarenotdesignedorintendedtobefail-safeorforuseinanyapplicationrequiringfail-safeperformance;youassumesoleriskandliabilityforuseofXilinxproductsinCriticalApplications:http://www.

xilinx.

com/warranty.

htm#critapps.

DateVersionDescriptionofRevisions01/30/121.

0InitialXilinxrelease.

0)January30,2012www.

xilinx.

com1Copyright2012Xilinx,Inc.

Xilinx,theXilinxlogo,Artix,ISE,Kintex,Spartan,Virtex,Zynq,andotherdesignatedbrandsincludedhereinaretrademarksofXilinxintheUnitedStatesandothercountries.

ThepurposeofaPowerDistributionNetwork(PDN)istoprovidepowertoelectricaldevicesinasystem.

Eachdeviceinasystemnotonlyhasitsownpowerrequirementsforitsinternaloperation,butalsoarequirementfortheinputvoltagefluctuationofthatpowerrail.

ForXilinxKintex-7andVirtex-7FPGAs,theanalogpowerrailshaveaninputvoltagefluctuationrequirementofnotmorethan10mVpeak-to-peakfromthe10kHztothe80MHzfrequencyrange.

Theself-generatedvoltagefluctuationonthepowerrailsisafunctionoffrequencyandcanbedescribedbyOhm'sLaw:Voltage(frequency)=Current(frequency)*Self-Impedance(frequency).

Thus,iftheuserdeterminestheself-impedance(frequency)andknowsthecurrent(frequency)ofthePDN,thenthevoltage(frequency)canbedetermined.

Theself-impedance(frequency)caneasilybedeterminedbysimulatingthefrequencydomainself-impedanceprofileofthePDNandis,thus,thesubjectofthiswhitepaper.

WhitePaper:Kintex-7andVirtex-7FPGAsWP411(v1.

0)January30,2012SimulatingFPGAPowerIntegrityUsingS-ParameterModelsBy:HanyFahmyandColinWarwickofAgilentTechnologies,Inc.

andJackCarrel,RayAnderson,HarryFu,andRomiMayderofXilinx,Inc.

2www.

xilinx.

comWP411(v1.

0)January30,2012OverviewOverviewBeforesimulatingthefrequencydomainself-impedanceprofilesofaPDN,itisimportanttoestablishexpectationsforthesimulationresults.

Todothis,anunderstandingofthefundamentalconceptsmustbeattained:Series-ResonanceCircuitandImpedanceMinimumsParallel-ResonanceCircuitandImpedanceMaximumsFrequencyComponentsofElectricalSignalsS-ParameterModelvs.

LumpedRLCModelforDecouplingCapacitorsSeries-ResonanceCircuitandImpedanceMinimumsAseries-resonantcircuitisdefinedbyacapacitor(C)andinductor(L)thatareconnectedinseries.

WhentheXC(capacitivereactance)andXL(inductivereactance)areequalinmagnitudeandoppositeinphase,thecurrentisatmaximum.

Thisconditiongivesrisetoanimpedanceminimum.

Thefrequencyatwhichthisequalityoccursiscalledtheseries-resonantfrequencyandisdescribedbyEquation1:Equation1Acommonseries-resonantcircuitisformedbythecapacitance(C)andtheparasiticinductance(L)ofagivencapacitormountedonaprintedcircuitboard.

Figure1showstheschematiccircuitrepresentationwhileFigure2showsthefrequencydomainimpedanceprofile.

X-RefTarget-Figure1Figure1:Series-ResonantComponentsofaPCB-MountedCapacitorX-RefTarget-Figure2Figure2:Frequency-DomainImpedanceProfileofPCB-MountedCapacitorf12πLC-=Series-ResonantCircuitP3Num=3P4Num=4CC2C=C_PCB_CapacitanceRR3R=R_PCB_CapacitanceLL2L=L_PCB_Cap_InductanceWP411_01_0124120.

00.

00.

20.

40.

60.

81.

01.

21.

41.

60.

10.

20.

30.

40.

5Freq,GHzImpedanceMinimumSeriesResonantCircuitSeries_Resonance0.

6WP411_02_1110110.

70.

80.

91.

0OverviewWP411(v1.

0)January30,2012www.

xilinx.

com3Parallel-ResonanceCircuitandImpedanceMaximumsAparallelanti-resonantcircuitisdefinedbyacapacitor(C)andinductor(L)thatareconnectedinparallel.

WhentheXC(capacitivereactance)andXL(inductivereactance)areequalinmagnitudeandoppositeinphase,thereactivebranchcurrentsarealsoequalinmagnitudeandoppositeinphase.

Thisgivesrisetoaminimumtotalcurrentandthus,amaximumtotalimpedanceiscreated.

Thefrequencyatwhichthisconditionoccursiscalledtheparallelanti-resonantfrequencyandisdescribedbyEquation2:Equation2Acommonparallelanti-resonantcircuitisoneformedbythediecapacitanceandpackageinductance.

Figure3showsaschematiccircuitrepresentationwhileFigure4showsthefrequencydomainimpedanceprofile.

X-RefTarget-Figure3Figure3:ParallelAnti-ResonantComponentsofDieandPackagePropertiesX-RefTarget-Figure4Figure4:Frequency-DomainImpedanceProfileofDieandPackagePropertiesf12πLC-=ParallelAnti-ResonantCircuitP1Num=1P2Num=2WP411_03_112411RR1R=R_Die_CapacitanceRR2R=R_Package_InductanceLL1L=L_Package_InductanceCC1C=C_Die_Capacitance0.

00.

00.

10.

20.

30.

40.

50.

60.

70.

80.

10.

20.

30.

40.

5Freq,GHzImpedanceMaximumParallelAnti-resonantCircuitParallel_Anti_Resonance0.

6WP411_04_1110110.

70.

80.

91.

04www.

xilinx.

comWP411(v1.

0)January30,2012OverviewFrequencyComponentsofElectricalSignalsThefrequencydomaincurrentprofileofVCCO(f)isshowninFigure5andFigure6assimulatedattheBGApowerballsoftheXilinxVirtex-7XC7VX485TFPGAintheFFG1761pinpackage.

Intheexample,thesimulationisrunningamemoryinterfaceat1.

866Gb/swithaPRBS15datapattern.

ThepowerspectraldensityofVCCO(t)iswide-banded,extendingfrom10MHzuptothe10GHz.

Asthedatatrafficpatternandactivitychange,thesimulationsdemonstratethatthedominantfrequencycomponentsofthepowerspectraldensityalsochange.

Therefore,thesimulationsshowthatPDNnoiseisawide-bandphenomenon;PDNsimulationsmust,therefore,berunoverawide-bandfrequencyrange.

X-RefTarget-Figure5Figure5:MemoryInterfaceSimulationActivityPatterns0.

00.

10.

20.

30.

40.

50.

60.

7Freq,HzFrequencySpectrumSSTL15CurrentSSTL15HPIOVCCOCurrentmag(FS_Kirtex_7_SSTL15_Current),mAWP411_05_011112IE9IE8IE7IE10051015202530Freq,HzFrequencySpectrumDDR3DieInputmag(FS_Kintex_7_SSTL15),mV-0.

50.

00.

51.

01.

52.

0DDR3_Die_Input_Eye_Diagram,VoltsIE9IE8IE7IE10-10-5051015202530Time,nsecKintex_7_SSTL15_Current,mA7080904050600012030100DDR3DieInput1,866Mb/sTime,nsec0.

70.

80.

90.

40.

50.

60.

00.

10.

20.

31.

01.

1OverviewWP411(v1.

0)January30,2012www.

xilinx.

com5Becausethepowerspectraldensityisofawideband,thefrequencydomainself-impedanceprofilemustbesimulatedoverawiderange.

Below1kHz,thevoltageregulatormodule(VRM)dominatesthefrequencydomainself-impedanceprofile.

Above10GHz,theon-diecapacitancedominatestheimpedanceprofile.

Thus,Xilinxrecommendsrunningthesimulationsfrom1kHzto10GHz.

S-ParameterModelvs.

LumpedRLCModelforDecouplingCapacitorsAsacomparisonbetweenusinglumpedRLCcircuitsandS-parameterstorunPDNsimulations,thedecouplingcapacitorsportionofthePDNcircuitisexaminedfirst.

Inthissimulation,anattemptismadetocurve-fitanS-parametermodelforcommonX5RcapacitorsinthefollowingEIAcasesizes:0201,0402,0603,0805,1206,and1610.

Aftermatchingthecapacitivereactanceandtheseries-resonantfrequencygiveninEquation1,thepercentageerroroftheinductivereactanceat100MHzismeasured.

Thesesimulationsaredoneatroomtemperature(25°C)withnoappliedDCbias.

Figure7throughFigure9showthecircuitschematicrepresentations.

Figure10andFigure11showthesimulationresults.

X-RefTarget-Figure6Figure6:SimulationTestSetupTTLPCPCGCGCPUPDPDPUVINI/OODigOPRBS15K7325TFF900SSTL15HPIODDR31.

86Gb/sDQPin40ΩImpedance3InchTraceDDR3PackageParasiticsWP411_06_011112VtPRBSVPRBS1PRBSIBIS_OIBIS1IBIS_IOIBIS4SLINTL1Subst="SSub1"W=5.

0milL=3000.

0milLL1L=1.

38nHR=0.

25656CC1C=0.

33pFDDR3DieInputEye_ProbeEye_Probe1V_DCSRC1VDC=1.

5VV_DCSRC2VDC=1.

5VPowerOutput++++––6www.

xilinx.

comWP411(v1.

0)January30,2012OverviewX-RefTarget-Figure7Figure7:DecouplingCapacitorsSimulation,SchematicRepresentation1X-RefTarget-Figure8Figure8:DecouplingCapacitorsSimulation,SchematicRepresentation2X-RefTarget-Figure9Figure9:DecouplingCapacitorsSimulation,SchematicRepresentation3DataSheetCeramic02011uF4VX5RWP411_07_013012TermTerm1Num=1Z=50Ω+–TermTerm2Num=2Z=50ΩS2PSNP1LL2L=320pHR=10mΩCC2C=0.

69uF+–TermTerm3Num=3Z=50Ω+–TermTerm4Num=4Z=50Ω+–DataSheetCeramic04024.

7uF4VX5RTermTerm16Num=16Z=50Ω+–TermTerm15Num=15Z=50ΩS2PSNP4LL3L=500pHR=8mΩCC3C=3.

7uF+–TermTerm14Num=14Z=50Ω+–TermTerm13Num=13Z=50Ω+–DataSheetCeramic060322uF4VX5RWP411_08_013012TermTerm12Num=12Z=50Ω+–TermTerm11Num=11Z=50ΩS2PSNP3LL4L=800pHR=4mΩCC4C=14uF+–TermTerm10Num=10Z=50Ω+–TermTerm9Num=9Z=50Ω+–DataSheetCeramic080522uF4VX5RTermTerm17Num=17Z=50Ω+–TermTerm18Num=18Z=50ΩS2PSNP5LL6L=800pHR=3.

5mΩCC6C=14uF+–TermTerm19Num=19Z=50Ω+–TermTerm20Num=20Z=50Ω+–DataSheetCeramic1206100uF4VX5RWP411_09_013012TermTerm21Num=21Z=50Ω+–TermTerm22Num=22Z=50ΩS2PSNP6LL5L=1,360pHR=2.

75mΩCC5C=50uF+–TermTerm23Num=23Z=50Ω+–TermTerm24Num=24Z=50Ω+–DataSheetCeramic1210100uF4VX5RTermTerm32Num=25Z=50Ω+–TermTerm31Num=26Z=50ΩS2PSNP8LL7L=1,200pHR=1.

9mΩCC7C=60uF+–TermTerm30Num=27Z=50Ω+–TermTerm29Num=28Z=50Ω+–OverviewWP411(v1.

0)January30,2012www.

xilinx.

com7X-RefTarget-Figure10Figure10:SimulationResults(EIACaseSizes0201/0603/1206)X-RefTarget-Figure11Figure11:SimulationResults(EIACaseSizes0402/0805/1210)1E-21E51E61E71E81E96E91E-111E1Freq,HzImpedanceMagnitude0201mag(Ceramic_0201_1uF_RLC)mag(Ceramic_0201_1uF_S)1E51E61E71E81E99580655035200-10-25-40-55-70-85-100Freq,HzImpedancePhase0201phase(Ceramic_0201_1uF_RLC),degphase(Ceramic_0201_1uF_S),deg1E-21E-31E51E61E71E81E96E91E-111E1Freq,HzImpedanceMagnitude0603mag(Ceramic_0603_1uF_RLC)mag(Ceramic_0603_1uF_S)1E51E61E71E81E99580655035200-10-25-40-55-70-85-100Freq,HzImpedancePhase0603phase(Ceramic_0603_1uF_RLC),degphase(Ceramic_0603_1uF_S),deg1E-21E-31E51E61E71E81E96E91E-111E1Freq,HzImpedanceMagnitude1206mag(Ceramic_1206_1uF_RLC)mag(Ceramic_1206_1uF_S)1E51E61E71E81E99580655035200-10-25-40-55-70-85-100Freq,HzImpedancePhase1206phase(Ceramic_1206_1uF_RLC),degphase(Ceramic_1206_1uF_S),degWP411_10_0116121E-31E-21E51E61E71E81E96E91E-111E1Freq,HzImpedanceMagnitude0402mag(Ceramic_0402_4_7uF_RLC)mag(Ceramic_0402_4_7uF_RLC)1E51E61E71E81E99580655035200-10-25-40-55-70-85-100Freq,HzImpedancePhase0402phase(Ceramic_0402_4_7uF_RLC),degphase(Ceramic_0402_4_7uF_S),deg1E-21E-31E51E61E71E81E96E91E-111E1Freq,HzImpedanceMagnitude0805mag(Ceramic_0805_22uF_RLC)mag(Ceramic_0805_22uF_S)1E51E61E71E81E99580655035200-10-25-40-55-70-85-100Freq,HzImpedancePhase0805phase(Ceramic_0805_22uF_RLC),degphase(Ceramic_0805_22uF_S),deg1E-21E-31E51E61E71E81E96E91E-111E1Freq,HzImpedanceMagnitude1210mag(Ceramic_1210_100uF_RLC)mag(Ceramic_1210_100uF_S)1E51E61E71E81E99580655035200-10-25-40-55-70-85-100Freq,HzImpedancePhase1210phase(Ceramic_1210_100uF_RLC),degphase(Ceramic_1210_100uF_S),degWP411_11_0116128www.

xilinx.

comWP411(v1.

0)January30,2012OverviewAsummaryofthedataisshownbelowinTable1:ItisknownthatthetypicalcapacitormanufacturerspecifiesthecapacitanceofacapacitorwithzeroDCbiasand0.

5VrmsACvoltage,whilethes-parametermodelsaretypicallymeasuredwitha0dbmACsignal.

InS-ParameterModelsforDecouplingCapacitorssection,thevariousmethodsforgeneratingtheS-parametermodelofacapacitorareexamined.

S-ParameterModelsforDecouplingCapacitorsAtfirstglance,themeasurementofthecapacitor'sPDNimpedanceprofile(theimpedancewithrespecttofrequency)seemstobeasimpletask,butseveralsubtledetailsarerequiredtoensurethemeasureddataisaccurate.

ThefrequencydomainmeasurementisusuallyaccomplishedbyutilizingaVectorNetworkAnalyzer(VNA).

TheobviousmethodistoprobethePDNmakinganS11measurement,andthenconvertthemeasureds-parameterstoimpedancebymeansoftheEquation3relationship:Equation3Animpedancemeasurementusingthismethod,however,hasinherentinaccuraciesduetothefactthattheinstrumenttypicallyhasa50ΩinputimpedanceandthePDNhasaverylowimpedance(typicallyinthemilliohmrange).

TheaccuracyofthemeasuredVNAdatainherentlyhaserrorsbecausethetypicaluncertaintyofS11(whenrho,thereflectioncoefficient,isnear1)canbeinthe1%–2%range.

Thisequatestoanimpedanceuncertaintyinthe0.

3Ω-to-0.

4Ωrange.

IfPDNimpedancesinthemilliohmrangearebeingmeasured,itquicklybecomesobviousthatthedesiredimpedancemeasurementislostinthemeasurementuncertainty.

AsecondfactortoconsideristhattheinductiveparasiticsoftheprobingarrangementcaneasilyexceedthevalueoftheDUTinductance.

Thereisnoeasywaytobackouttheprobeparasiticsfromthemeasureddata.

Fortunately,anS21measurementisagoodalternativetoanS11measurementtodeterminethePDNimpedance.

Inthismethod,itisfoundthatZdut=25(S21).

Withthismeasurementtechnique,thesolderofthedecouplingcapacitorisincludedinthemeasurement.

ByutilizingtheS21measurement,theimpedanceuncertaintyisreducedintothe10s-of-milliohmsrange.

Inaddition,theprobeparasiticsareinserieswith50ΩasopposedtobeinginserieswiththeDUTimpedance,whichreducestheireffectstonearnegligiblelevels.

Foramorecompletediscussionofthistopic,seeAccuracyImprovementsofPDNImpedanceMeasurementsintheLowtoMiddleFrequencyTable1:SummaryofResultData,DecouplingCapacitorsSimulationSizeCapacitance(F)ImpedanceMagnitude@100MHzSeries-ResonantFrequencyEIACodeS-ParameterDataSheet%ErrorS-ParameterRLCModel%Error12106010066.

70.

2090.

751259.

3600KHz120650100100.

00.

2550.

845231.

4700KHz805142257.

10.

180.

501178.

31.

5MHz603142257.

10.

1780.

501181.

51.

5MHz4023.

74.

727.

00.

150.

313108.

73.

5MHz2010.

69144.

90.

1290.

19853.

510MHzZdut501S11+1S11–-=OverviewWP411(v1.

0)January30,2012www.

xilinx.

com9RangepresentedatDesignCon2010byIstvanNovakofSUNMicrosystemsandYasuhiroMoriandMikeRessoofAgilentTechnologies(http://www.

home.

agilent.

com/upload/cmc_upload/All/DC10_ID2696_Novak-Mori-Resso.

pdf).

RLCModelsforDecouplingCapacitorDecouplingcapacitorsareoftencharacterizedbyvendorsbymeansofthreeparameters:R(resistance),L(inductance),andC(capacitance).

TheCparameteristhedecap'sintrinsiccapacitance;theLisitsintrinsicinductance;andtheRistheESRofthedecouplingcapacitor.

WhenthissimpleRLCmodelforadecouplingcapacitorisutilizedinasimulationalongwithagoodPDNmodel,themountinginductanceandspreadinginductanceassociatedwiththepackageorPCBcombineswiththedecap'sintrinsicinductancetoeffectivelymodeltheloopinductance.

Thisloopinductanceplusthepackageinductanceresonateswiththediecapacitancetoformaparallelanti-resonantcircuitwithauniqueimpedanceprofile.

SeriesRLCmodelsofdecouplingcapacitorsareeasytounderstand,andtheysimulatequicklyasbothfrequencydomainandtransientsimulationswithaminimumofissues.

Asnotedpreviously,theRLCvaluesforthemodelcancomefromavendor'sdatasheet;alternatively,theycanbederivedfrommeasureds-parameterdatabyfittingthevaluesofasimpleseriesRLCcircuittotheresponseofthes-parameters.

Insomecases,particularlyatlowfrequencies,thesimpleseriesRLCcircuitworksadequately.

However,whenitisrequiredtodeterminetheimpedanceprofileofaPDNaccuratelyoverawidebandwidthofDCtoseveralgigahertz,thingsusuallydonotworkoutsosimply.

TwomainissuesmakesimpleseriesRLCmodelsinadequateforaccuratePDNsimulations.

Duetothestackedlayersofthedecouplingcapacitorconstruction,thereisdistributedinductanceandresistanceintheZaxisoftheplatestack.

ThiscausestheLparameteroftheseriesRLCrepresentationtobefrequencydependent.

Inmostsimulators,thereisnofrequency-dependentLelement.

First,areasonablyaccurateseriesRLCmodelcanbeconstructedateitherlowfrequenciesorhighfrequencies,butcannotmodelbothsimultaneously.

Second,whileacomplexmulti-elementmodelcanbeconstructedtomoreaccuratelymodelthefrequency-dependentLeffect,suchmodelsareverydifficulttodesignandmanage.

Therefore,ratherthanuseasimpleseriesRLCcircuitthatisknowntobeinaccurateoverawidebandwidth,orattempttosynthesizeamorecomplexmulti-elementmodel,thesimulationworkdoneatXilinxsuggeststhatitismucheasierandmoreaccuratetoutilizeameasuredwidebands-parameterdecouplingcapacitormodelwhensimulatingPDNs.

Note:Ceramicdecouplingcapacitormodelsarestronglyvoltagedependent.

Therefore,itisimportanttoobtainthes-parametermodelfromthecapacitormanufacturerthathasbeenmeasuredattheoperatingvoltageofinterest—forbothDCandACvoltages.

10www.

xilinx.

comWP411(v1.

0)January30,2012RunningthePDNSimulationswiththeAgilentADS2011.

10RunningthePDNSimulationswiththeAgilentADS2011.

10Tosimulatethefrequencydomainself-impedanceprofileofaPowerDistributionNetwork,XilinxrecommendsusingtheAgilentADS2011softwarebundle.

Thissoftwarebundleprovidesthehigh-speed-digital(HSD)designerwithawiderangeoftools.

Everyaspectofthepowerintegrityproblemrequiresaspecifictechniqueforsolvingit.

Forexample,PDNanalysisrequiresthefollowing:1.

Truefrequency-domainsimulationofthePDNparallelanti-resonancesandseriesresonanceswithsolidS-parameterhandlingandassuranceof"PassivityandCausality"2.

Patentedconvolution(Kramers-Kronig)tobringfrequency-domainmodels(measurement-basedmodelsandEM-basedmodels)intothetimedomain(eyediagrams,BERcontours,andjitterdecomposition)3.

Usinganextractiontechnique,suchasMethod-of-Moment,whichhasexcellentaccuracyfromDCtoGHzrangePDNSimulationExampleInthissimulationexample,thesimulationperformedisthePDNoftheMGTAVCCandMGTAVTTanalogpowerrailsfortheXilinx7seriesXC7VX485TFPGAintheFFG1761pinpackage.

Twocasesaresimulatedhere.

Case1usesthePCBcapacitorslistedinTable2,whicharesimilartotherecommendedPCBcapsfortheXilinxVirtex-6devices.

Case2usesthePCBcapacitorsdescribedinTable3.

Figure12istheschematicforbothcases(1)and(2)listedabovefortheMGTAVCCandMGTAVTTpowerrails.

Forcase2(withnoPCBcapacitors),thereisstillonebulkcapacitormountedonthePCBspecifiedbythemanufacturerofthevoltageregulatormodule.

Table2:Case1CapacitorsQTYperGroupCapacitance(F)MGTAVCCMGTAVTTMGTVCCAUX4420.

0224400.

4722112214.

7Table3:Case2CapacitorsQTYperGroupCapacitance(F)MGTAVCCMGTAVTTMGTVCCAUX0000.

0220000.

4700010004.

7RunningthePDNSimulationswiththeAgilentADS2011.

10WP411(v1.

0)January30,2012www.

xilinx.

com11X-RefTarget-Figure12Figure12:PowerRailsSimulationSchematicRepresentationTermTerm13Num=13Z=50OhmTermTerm14Num=14Z=50OhmCC30C=22.

16nFS2PSNP105File="GRM155R61C223KA01_022uF_0402S2P"S2PSNP49File="T520V337M2R5ATE025.

s2p"S2PSNP111File="GRM152R60J474ME15_047_0402.

S2P"S2PSNP108File="GRM152R60J474ME15_047_0402.

S2P"S2PSNP107File="GRM152R60J474ME15_047_0402.

S2P"S2PSNP106File="GRM152R60J474ME15_047_0402.

S2P"S2PSNP109File="GRM188R61C105KA93_1uF_0603.

S2P"S2PSNP53File="GRM033C80G104KE19series(for_Fuji2_AVTT_AVCC).

s2p"S2PSNP52File="GRM033C80G104KE19series(for_Fuji2_AVTT_AVCC).

s2p"S2PSNP51File="GRM033C80G104KE19series(for_Fuji2_AVTT_AVCC).

s2p"S2PSNP50File="GRM033C80G104KE19series(for_Fuji2_AVTT_AVCC).

s2p"LL28L=25nHR=1mOhmV_DCSRC7Vdc=1.

2V+–S6PSNP48File="fga2034_485t_ff1761_031411_Avcc_G10.

s6p"S2PSNP104File="GRM155R61C223KA01_022uF_0402.

S2P"S2PSNP105File="GRM155R61C223KA01_022uF_0402.

S2P"S2PSNP105File="GRM155R61C223KA01_022uF_0402.

S2P"RR8R=10mOhmWP411_12_012212++––PackageCapacitorsVRMDieCapacitorsS2PSNP112File="GRM188R60J475KE19_47uF_0603.

S2P"S2PSNP113File="GRM188R60J475KE19_47uF_0603.

S2P"S2PSNP110File="GRM188R61C105KA93_1uF_0603.

S2P"S20PSNP47File="VC7203_MGTAVCC_092611_175001_S.

s20p"12www.

xilinx.

comWP411(v1.

0)January30,2012RunningthePDNSimulationswiththeAgilentADS2011.

10Figure13showthesimulationsresults.

Figure14showsthecompletesimulationtimeusingatypicallaptopcomputerrunningtheWindows-764-bitoperatingsystemisonly11.

68seconds!

Becausethesimulationresultsforbothcasesresultinalmostidenticalfrequencydomainself-impedanceprofilesfortheMGTAVCCandMGTAVTTpowerrails,andbecausetheMGTVCCAUXpowerrailhasaninternallowdropoutregulatorintegratedonthedie,similarperformancebetweenthetwocasesshouldbeexpected.

Asasimplereference,theimpedanceprofilesweresimulatedonacompetitivedevicewith0PCBcapacitorsbeyondthe1bulkPCBcapacitortypicallyrequiredbythevoltageregulatormanufacturer.

ProfilesrepresentingtheVCCH_GXBL0,VCCT_GXBL0,andVCCR_GXBL0powerrailswererun.

X-RefTarget-Figure13Figure13:PowerRailsSimulationResults1E31E41E51E61E71E81E91E10freq,HzMGTAVCC-MagnitudeTypicalCompetitormag(Competitor_PLL_Supply_With_PCB_Caps)mag(MGTAVCC_Die_Without_PCB_Caps)mag(MGTAVCC_Die_With_PCB_Caps)130012001100100090080070060050040030020010001E31E41E51E61E71E81E91E10freq,HzMGTAVCC-MagnitudeTypicalCompetitormag(Competitor_Tx_Rx_Supply_With_PCB_Caps)mag(MGTAVTT_Die_Without_PCB_Caps)mag(MGTAVTT_Die_With_PCB_Caps)13001200110010009008007006005004003002001000WP411_13_012212X-RefTarget-Figure14Figure14:CompleteSimulationTime,Windows-764-bitOSWP411_14_012212RunningthePDNSimulationswiththeAgilentADS2011.

10WP411(v1.

0)January30,2012www.

xilinx.

com13AscaneasilybeseeninthePDNprofilesofatypicalcompetitivedevice,theanalograilswouldhaveapeakimpedanceofwellover2ΩifthePCBcapswereremoved!

TransmitterHardwareMeasurementsFigure15throughFigure18containaseriesofeyediagramsat10.

3125Gb/susingtheQPLLand6.

25Gb/susingtheCPLLwithPRBS15datapatternmeasuredontheAgilentInfiniiumDCA-JWide-BandwidthOscilloscope.

ThisAgilent86100Cwiththe86108Aprecisionwaveformanalyzerhasbeenselectedtomakethesehardwaremeasurementsbecauseofthefollowingkeyattributes:1.

Highbandwidth,lownoise,andultra-lowresidualjitter2.

Simpleoneconnection"triggerless"operation3.

PLLcharacterizationincludingloopBW/jittertransfer4.

IntegratedhardwareclockrecoverwithadjustableloopBW/Peaking—exceedsindustrystandardsFigure15showstheeyediagramandassociatedjitterdecompositionwhenusingtheCPLLrunningat6.

25Gb/sforcase1.

Figure16showstheeyediagramandassociatedjitterdecompositionwhenusingtheCPLLrunningat6.

25Gb/sforcase2(noPCBcaps).

X-RefTarget-Figure15Figure15:Case1EyeDiagram,6.

25Gb/sWP411_15_01161214www.

xilinx.

comWP411(v1.

0)January30,2012RunningthePDNSimulationswiththeAgilentADS2011.

10Figure17showstheeyediagramandassociatedjitterdecompositionwhenusingtheQPLLrunningat10.

3125Gb/sforcase1.

Figure18showstheeyediagramandassociatedjitterdecompositionwhenusingtheQPLLrunningat10.

3125Gb/sforcase2(noPCBcaps).

X-RefTarget-Figure16Figure16:Case2EyeDiagram,6.

25Gb/sWP411_16_011612X-RefTarget-Figure17Figure17:Case1EyeDiagram,10.

3125Gb/sWP411_17_011612RunningthePDNSimulationswiththeAgilentADS2011.

10WP411(v1.

0)January30,2012www.

xilinx.

com15AsseeninthescopescreenshotsinFigure15throughFigure18,thetotaljitterisbothcases1and2iswithinthemeasurementtoleranceofthesetup.

Thus,hardwaremeasurementshaveconfirmedthesimulationresultsshowingthat0PCBcapsarerequiredforproperoperationofthetransmitter.

ReceiverMeasurementsTable4isasummaryofthereceiverhardwaremeasurementsbasedonaloopbacktestusingeyescan.

ThedatarecordedinTable4isthevoltageamplitudenoisewithalltransceiversinthepackagerunningasynchronously.

Asshownbythedata,thevoltageamplitudenoiseisthesameorlessafterallthePCBcapshavebeenremovedwhenusingeithertheCPLLortheQPLL.

Figure19isasummaryofthereceiver'sjittertoleranceanalysiswithalltransceiversinthepackagerunningasynchronouslyforbothcases1and2.

Asshownbythedata,thejittertoleranceisthesameorlessafterallthePCBcapshavebeenremoved.

Thejittertoleranceanalysiswasdoneat10-12BERthresholdandadatarateof10.

3125Gb/s.

X-RefTarget-Figure18Figure18:Case2EyeDiagram,10.

3125Gb/sWP411_18_011612Table4:ComparisonofVoltageAmplitudeNoisewith/withoutDecouplingCapsPLLCPLLQPLLBitRate6.

25Gb/s10.

3125Gb/sMGTAVCCAllCapsNoCapsAllCapsNoCapsMGTAVTTAllCapsNoCapsAllCapsNoCapsMGTVCCAUXAllCapsNoCapsAllCapsNoCaps%FullScale3.

6%3.

3%5.

0%4.

5%16www.

xilinx.

comWP411(v1.

0)January30,2012SummarySummaryPDNsimulations,confirmedbyhardwaremeasurements,haveshownthatnoPCBcapsbeyondthatrecommendedbythevoltageregulatormanufacturerarerequiredfortheMGTAVTT,MGTAVCC,andMGTVCCAUXpowerrailsforproperoperationofthetransceiversinXilinx'sKintex-7andVirtex-7devices.

WhilethePCBcapacitorsarenotneededforproperoperationofthetransceivers,however,properfilteringcanberequiredonthePCBtoachievetheinputvoltageripplenoisespecificationof10mVpeak-to-peak(10kHzto80MHz)whenmeasuredattheBGAballofthepackage.

Currently,XilinxhasseveralAgilentADSPowerIntegrityDesignKitsavailablefor7seriesFPGAsthatsupportalldevicepowersupplies(digitalandanalog).

ContactyourlocalXilinxfieldapplicationengineertoobtaintheseAgilentADSDesignKits.

Toobtaina30-dayfreelicenseofAgilentADS2011,pleasevisitthefollowinglink:https://software.

business.

agilent.

com/TrialLicense/TrialLicenseRequest.

aspxProdNum=W2200F-1U1-TRLX-RefTarget-Figure19Figure19:ComparisonofJitterTolerancewith/withoutDecouplingCaps100.

0010.

001.

000.

100AllCapsBER12NoCapsBER120.

010.

101.

00Frequency,MHzSI,UI10.

00100.

00WP411_xx_012212RevisionHistoryWP411(v1.

0)January30,2012www.

xilinx.

com17RevisionHistoryThefollowingtableshowstherevisionhistoryforthisdocument:NoticeofDisclaimerTheinformationdisclosedtoyouhereunder(the"Materials")isprovidedsolelyfortheselectionanduseofXilinxproducts.

Tothemaximumextentpermittedbyapplicablelaw:(1)Materialsaremadeavailable"ASIS"andwithallfaults,XilinxherebyDISCLAIMSALLWARRANTIESANDCONDITIONS,EXPRESS,IMPLIED,ORSTATUTORY,INCLUDINGBUTNOTLIMITEDTOWARRANTIESOFMERCHANTABILITY,NON-INFRINGEMENT,ORFITNESSFORANYPARTICULARPURPOSE;and(2)Xilinxshallnotbeliable(whetherincontractortort,includingnegligence,orunderanyothertheoryofliability)foranylossordamageofanykindornaturerelatedto,arisingunder,orinconnectionwith,theMaterials(includingyouruseoftheMaterials),includingforanydirect,indirect,special,incidental,orconsequentiallossordamage(includinglossofdata,profits,goodwill,oranytypeoflossordamagesufferedasaresultofanyactionbroughtbyathirdparty)evenifsuchdamageorlosswasreasonablyforeseeableorXilinxhadbeenadvisedofthepossibilityofthesame.

XilinxassumesnoobligationtocorrectanyerrorscontainedintheMaterialsortonotifyyouofupdatestotheMaterialsortoproductspecifications.

Youmaynotreproduce,modify,distribute,orpubliclydisplaytheMaterialswithoutpriorwrittenconsent.

CertainproductsaresubjecttothetermsandconditionsoftheLimitedWarrantieswhichcanbeviewedathttp://www.

xilinx.

com/warranty.

htm;IPcoresmaybesubjecttowarrantyandsupporttermscontainedinalicenseissuedtoyoubyXilinx.

Xilinxproductsarenotdesignedorintendedtobefail-safeorforuseinanyapplicationrequiringfail-safeperformance;youassumesoleriskandliabilityforuseofXilinxproductsinCriticalApplications:http://www.

xilinx.

com/warranty.

htm#critapps.

DateVersionDescriptionofRevisions01/30/121.

0InitialXilinxrelease.

- WP411_06_011112avtt4.com相关文档

- 2.5avtt4.com

- 缸体avtt4.com

- measuredavtt4.com

- correspondsavtt4.com

- Refreshavtt4.com

- MHzavtt4.com

BuyVM商家4个机房的官方测试IP地址和测速文件

BuyVM 商家算是有一些年头,从早年提供低价便宜VPS主机深受广大网友抢购且也遭到吐槽的是因为审核账户太过于严格。毕竟我们国内的个人注册账户喜欢账户资料乱写,毕竟我们看英文信息有些还是比较难以识别的,于是就注册信息的时候随便打一些字符,这些是不能通过的。前几天,我们可以看到BUYVM商家有新增加迈阿密机房,而且商家有提供大硬盘且不限制流量的VPS主机,深受有一些网友的喜欢。目前,BUYVM商家有...

legionbox:美国、德国和瑞士独立服务器,E5/16GB/1Gbps月流量10TB起/$69/月起

legionbox怎么样?legionbox是一家来自于澳大利亚的主机销售商,成立时间在2014年,属于比较老牌商家。主要提供VPS和独立服务器产品,数据中心包括美国洛杉矶、瑞士、德国和俄罗斯。其中VPS采用KVM和Xen架构虚拟技术,硬盘分机械硬盘和固态硬盘,系统支持Windows。当前商家有几款大硬盘的独立服务器,可选美国、德国和瑞士机房,有兴趣的可以看一下,付款方式有PAYPAL、BTC等。...

Bluehost美国虚拟主机2.95美元/月,十八周年庆年付赠送顶级域名和SSL证书

Bluehost怎么样,Bluehost好不好,Bluehost成立十八周年全场虚拟主机优惠促销活动开始,购买12个月赠送主流域名和SSL证书,Bluehost是老牌虚拟主机商家了,有需要虚拟主机的朋友赶紧入手吧,活动时间:美国MST时间7月6日中午12:00到8月13日晚上11:59。Bluehost成立于2003年,主营WordPress托管、虚拟主机、VPS主机、专用服务器业务。Blueho...

avtt4.com为你推荐

-

netlife熊猫烧香是怎么制作的比肩工场比肩是什么意思,行比肩大运的主要意象百花百游迎得春来非自足,百花千卉共芬芳什么意思51sese.comwww.51xuanh.com这是什么网站是骗人的吗?m.2828dy.com电影虫www.dyctv.com这个电影站能下载电影吗?百度指数词百度指数为0的词 为啥排名没有16668.com香港最快开奖现场直播今晚开dadi.tv电视机如何从iptv转换成tv?鹤城勿扰齐齐哈尔电视台晴彩鹤城是哪个频道本冈一郎本冈一郎有副作用吗?主要有什么呢?