SCLwww.ddd138.com

www.ddd138.com 时间:2021-05-24 阅读:()

Rev.

1.

012/10Copyright2010bySiliconLaboratoriesSi5319Si5319FeaturesGeneratesanyfrequencyfrom2kHzto945MHzandselectfrequenciesto1.

4GHzfromaninputfrequencyof2kHzto710MHzUltra-lowjitterclockoutputwithjittergenerationaslowas0.

3psrms(50kHz–80MHz)Integratedloopfilterwithselectableloopbandwidth(60Hzto8.

4kHz)MeetsOC-192GR-253-COREjitterspecificationsClockorcrystalinputwithmanualclockselectionSelectableclockoutputsignalformat(LVPECL,LVDS,CML,CMOS)SupportforITUG.

709andcustomOTNFECratios(e.

g.

255/238,255/237,255/236)SupportsvariousfrequencytranslationsforSynchronousEthernetLOL,LOSalarmoutputsI2CorSPIprogrammableOn-chipvoltageregulatorfor1.

8V±5%,2.

5V±10%or3.

3V±10%operationSmallsize:6x6mm36-leadQFNPb-free,ROHScompliantApplications10G/40G/100GOTNlinecardsSONET/SDHOC-48/STM-16andOC-192/STM-64linecardsGbE/10GbE,1/2/4/8/10GFClinecardsITUG.

709andcustomFEClinecardsSynchronousEthernetOpticalmodulesWirelessbasestationsDataconverterclockingDSLAM/MSANsTestandmeasurementBroadcastvideoDiscretePLLreplacementDescriptionTheSi5319isajitter-attenuatingprecisionM/Nclockmultiplierforapplicationsrequiringsub1psjitterperformance.

TheSi5319acceptsoneclockinputrangingfrom2kHzto710MHzandgeneratesoneclockoutputrangingfrom2kHzto945MHzandselectfrequenciesto1.

4GHz.

TheSi5319canalsouseitscrystaloscillatorasaclocksourceforfree-runningclockgeneration.

Thedeviceprovidesvirtuallyanyfrequencytranslationcombinationacrossthisoperatingrange.

TheSi5319inputclockfrequencyandclockmultiplicationratioareprogrammablethroughanI2CorSPIinterface.

TheSi5319isbasedonSiliconLaboratories'third-generationDSPLLtechnology,whichprovidesany-frequencysynthesisandjitterattenuationinahighlyintegratedPLLsolutionthateliminatestheneedforexternalVCXOandloopfiltercomponents.

TheDSPLLloopbandwidthisdigitallyprogrammable,providingjitterperformanceoptimizationattheapplicationlevel.

Operatingfromasingle1.

8,2.

5,or3.

3Vsupply,theSi5319isidealforprovidingclockmultiplicationandjitterattenuationinhighperformancetimingapplications.

ANY-FREQUENCYPRECISIONCLOCKMULTIPLIER/JITTERATTENUATORSi53192Rev.

1.

0Si5319Rev.

1.

03TABLEOFCONTENTSSectionPage1.

ElectricalSpecifications42.

TypicalPhaseNoisePlots142.

1.

Example:SONETOC-192143.

FunctionalDescription163.

1.

ExternalReference163.

2.

FurtherDocumentation164.

RegisterMap175.

PinDescriptions:Si5319406.

OrderingGuide437.

PackageOutline:36-PinQFN448.

RecommendedPCBLayout459.

Si5319DeviceTopMark47DocumentChangeList48ContactInformation50Si53194Rev.

1.

01.

ElectricalSpecificationsFigure1.

DifferentialVoltageCharacteristicsFigure2.

Rise/FallTimeCharacteristicsTable1.

RecommendedOperatingConditionsParameterSymbolTestConditionMinTypMaxUnitAmbientTemperatureTA-402585°CSupplyVoltageduringNormalOperationVDD3.

3VNominal2.

973.

33.

63V2.

5VNominal2.

252.

52.

75V1.

8VNominal1.

711.

81.

89VNote:Allminimumandmaximumspecificationsareguaranteedandapplyacrosstherecommendedoperatingconditions.

Typicalvaluesapplyatnominalsupplyvoltagesandanoperatingtemperatureof25Cunlessotherwisestated.

Si5319Rev.

1.

05Table2.

DCCharacteristics(VDD=1.

8±5%,2.

5±10%,or3.

3V±10%,TA=–40to85°C)ParameterSymbolTestConditionMinTypMaxUnitSupplyCurrent1IDDLVPECLFormat622.

08MHzOut—217243mACMOSFormat19.

44MHzOut—194220mADisableMode—165—mACKINInputPin2InputCommonModeVoltage(InputThresh-oldVoltage)VICM1.

8V±5%0.

9—1.

4V2.

5V±10%1—1.

7V3.

3V±10%1.

1—1.

95VInputResistanceCKNRINSingle-ended204060kΩSingle-EndedInputVoltageSwing(SeeAbsoluteSpecs)VISEfCKIN212.

5MHzSeeFigure1.

0.

25——VPPDifferentialInputVoltageSwing(SeeAbsoluteSpecs)VIDfCKIN212.

5MHzSeeFigure1.

0.

25——VPPOutputClock(CKOUT)3CommonModeCKOVCMLVPECL100loadline-to-lineVDD–1.

42—VDD–1.

25VDifferentialOutputSwingCKOVDLVPECL100loadline-to-line1.

1—1.

9VPPSingleEndedOutputSwingCKOVSELVPECL100loadline-to-line0.

5—0.

93VPPDifferentialOutputVoltageCKOVDCML100loadline-to-line350425500mVPPNotes:1.

Currentdrawisindependentofsupplyvoltage.

2.

Nounder-orovershootisallowed.

3.

LVPECLoutputsrequirenominalVDD≥2.

5V.

4.

Thisistheamountofleakagethatthe3-levelinputscantoleratefromanexternaldriver.

SeeSi53xxFamilyReferenceManualformoredetails.

5.

LVPECL,CML,LVDSandlow-swingLVDSmeasuredwithFo=622.

08MHz.

Si53196Rev.

1.

0CommonModeOutputVoltageCKOVCMCML100loadline-to-line—VDD–0.

36—VDifferentialOutputVoltageCKOVDLVDS100loadline-to-line500700900mVPPLowSwingLVDS100loadline-to-line350425500mVPPCommonModeOutputVoltageCKOVCMLVDS100loadline-to-line1.

1251.

21.

275VDifferentialOutputResistanceCKORDCML,LVPECL,LVDS—200—OutputVoltageLowCKOVOLLHCMOS——0.

4VOutputVoltageHighCKOVOHLHVDD=1.

71VCMOS0.

8xVDD——VOutputDriveCurrent(CMOSdrivingintoCKOVOLforoutputloworCKOVOHforoutputhigh.

CKOUT+andCKOUT–shortedexternally)CKOIOICMOS[1:0]=11VDD=1.

8V—7.

5—mAICMOS[1:0]=10VDD=1.

8V—5.

5—mAICMOS[1:0]=01VDD=1.

8V—3.

5—mAICMOS[1:0]=00VDD=1.

8V—1.

75—mAICMOS[1:0]=11VDD=3.

3V—32—mAICMOS[1:0]=10VDD=3.

3V—24—mAICMOS[1:0]=01VDD=3.

3V—16—mAICMOS[1:0]=00VDD=3.

3V—8—mATable2.

DCCharacteristics(Continued)(VDD=1.

8±5%,2.

5±10%,or3.

3V±10%,TA=–40to85°C)ParameterSymbolTestConditionMinTypMaxUnitNotes:1.

Currentdrawisindependentofsupplyvoltage.

2.

Nounder-orovershootisallowed.

3.

LVPECLoutputsrequirenominalVDD≥2.

5V.

4.

Thisistheamountofleakagethatthe3-levelinputscantoleratefromanexternaldriver.

SeeSi53xxFamilyReferenceManualformoredetails.

5.

LVPECL,CML,LVDSandlow-swingLVDSmeasuredwithFo=622.

08MHz.

Si5319Rev.

1.

072-LevelLVCMOSInputPinsInputVoltageLowVILVDD=1.

71V——0.

5VVDD=2.

25V——0.

7VVDD=2.

97V——0.

8VInputVoltageHighVIHVDD=1.

89V1.

4——VVDD=2.

25V1.

8——VVDD=3.

63V2.

5——V3-LevelInputPins4InputVoltageLowVILL——0.

15xVDDVInputVoltageMidVIMM0.

45xVDD—0.

55xVDDVInputVoltageHighVIHH0.

85xVDD——VInputLowCurrentIILLSeeNote4–20——μAInputMidCurrentIIMMSeeNote4–2—+2μAInputHighCurrentIIHHSeeNote4——20μALVCMOSOutputPinsOutputVoltageLowVOLIO=2mAVDD=1.

71V——0.

4VOutputVoltageLowIO=2mAVDD=2.

97V——0.

4VTable2.

DCCharacteristics(Continued)(VDD=1.

8±5%,2.

5±10%,or3.

3V±10%,TA=–40to85°C)ParameterSymbolTestConditionMinTypMaxUnitNotes:1.

Currentdrawisindependentofsupplyvoltage.

2.

Nounder-orovershootisallowed.

3.

LVPECLoutputsrequirenominalVDD≥2.

5V.

4.

Thisistheamountofleakagethatthe3-levelinputscantoleratefromanexternaldriver.

SeeSi53xxFamilyReferenceManualformoredetails.

5.

LVPECL,CML,LVDSandlow-swingLVDSmeasuredwithFo=622.

08MHz.

Si53198Rev.

1.

0OutputVoltageHighVOHIO=–2mAVDD=1.

71VVDD–0.

4——VOutputVoltageHighIO=–2mAVDD=2.

97VVDD–0.

4——VDisabledLeakageCurrentIOZRSTb=0–100—100μATable3.

MicroprocessorControl(VDD=1.

8±5%,2.

5±10%,or3.

3V±10%,TA=–40to85°C)ParameterSymbolTestConditionMinTypMaxUnitI2CBusLines(SDA,SCL)InputVoltageLowVILI2C——0.

25xVDDVInputVoltageHighVIHI2C0.

7xVDD—VDDVInputCurrentIII2CVIN=0.

1xVDDto0.

9xVDD–10—10μAHysteresisofSchmitttriggerinputsVHYSI2CVDD=1.

8V0.

1xVDD——VVDD=2.

5or3.

3V0.

05xVDD——VOutputVoltageLowVOLI2CVDD=1.

8VIO=3mA——0.

2xVDDVVDD=2.

5or3.

3VIO=3mA——0.

4VSPISpecificationsDutyCycle,SCLKtDCSCLK=10MHz40—60%CycleTime,SCLKtc100——nsRiseTime,SCLKtr20–80%——25nsFallTime,SCLKtf20–80%——25nsTable2.

DCCharacteristics(Continued)(VDD=1.

8±5%,2.

5±10%,or3.

3V±10%,TA=–40to85°C)ParameterSymbolTestConditionMinTypMaxUnitNotes:1.

Currentdrawisindependentofsupplyvoltage.

2.

Nounder-orovershootisallowed.

3.

LVPECLoutputsrequirenominalVDD≥2.

5V.

4.

Thisistheamountofleakagethatthe3-levelinputscantoleratefromanexternaldriver.

SeeSi53xxFamilyReferenceManualformoredetails.

5.

LVPECL,CML,LVDSandlow-swingLVDSmeasuredwithFo=622.

08MHz.

Si5319Rev.

1.

09LowTime,SCLKtlsc20–20%30——nsHighTime,SCLKthsc80–80%30——nsDelayTime,SCLKFalltoSDOActivetd1——25nsDelayTime,SCLKFalltoSDOTransitiontd2——25nsDelayTime,SSRisetoSDOTri-statetd3——25nsSetupTime,SStoSCLKFalltsu125——nsHoldTime,SStoSCLKRiseth120——nsSetupTime,SDItoSCLKRisetsu225——nsHoldTime,SDItoSCLKRiseth220——nsDelayTimebetweenSlaveSelectstcs25——nsTable4.

ACSpecifications(VDD=1.

8±5%,2.

5±10%,or3.

3V±10%,TA=–40to85°C)ParameterSymbolTestConditionMinTypMaxUnitSingle-EndedReferenceClockInputPinXA(XBwithcaptoGND)InputResistanceXARINRATE[1:0]=LMorMH,accoupled—12—kInputVoltageSwingXAVPPRATE[1:0]=LMorMH,accoupled0.

5—1.

2VPPDifferentialReferenceClockInputPins(XA/XB)InputVoltageSwingXA/XBVPPRATE[1:0]=LMorMH0.

5—1.

2VPP,each.

CKINInputPinsInputFrequencyCKNF0.

002—710MHzTable3.

MicroprocessorControl(Continued)(VDD=1.

8±5%,2.

5±10%,or3.

3V±10%,TA=–40to85°C)ParameterSymbolTestConditionMinTypMaxUnitSi531910Rev.

1.

0InputDutyCycle(MinimumPulseWidth)CKNDCWhicheverissmaller(i.

e.

,the40%/60%limitationappliesonlytohigh-frequencyclocks)40—60%2——nsInputCapacitanceCKNCIN——3pFInputRise/FallTimeCKNTRF20–80%SeeFigure2——11nsCKOUTOutputPins(Seeorderingsectionforspeedgradevsfrequencylimits)OutputFrequency(Outputnotconfig-uredforCMOSorDisabled)CKOFN160.

002—945MHzN1=5970—1134MHzN1=41.

213—1.

4GHzMaximumOutputFrequencyinCMOSFormatCKOF——212.

5MHzOutputRise/Fall(20–80%)@622.

08MHzoutputCKOTRFOutputnotconfiguredforCMOSorDisabledSeeFigure2—230350psOutputRise/Fall(20–80%)@212.

5MHzoutputCKOTRFCMOSOutputVDD=1.

71CLOAD=5pF——8nsOutputRise/Fall(20–80%)@212.

5MHzoutputCKOTRFCMOSOutputVDD=2.

97CLOAD=5pF——2nsOutputDutyCycleUncertainty@622.

08MHzCKODC100LoadLine-to-LineMeasuredat50%Point(NotforCMOS)——+/-40psLVCMOSInputPinsMinimumResetPulseWidthtRSTMN1——μsResettoMicroproces-sorAccessReadytREADY——10msInputCapacitanceCin——3pFTable4.

ACSpecifications(Continued)(VDD=1.

8±5%,2.

5±10%,or3.

3V±10%,TA=–40to85°C)ParameterSymbolTestConditionMinTypMaxUnitSi5319Rev.

1.

011LVCMOSOutputPinsRise/FallTimestRFCLOAD=20pfSeeFigure2—25—nsLOSnTriggerWindowLOSTRIGFromlastCKINntoInternaldetectionofLOSnN3≠1——4.

5xN3TCKINTimetoClearLOLafterLOSClearedtCLRLOLLOStoLOLFold=FnewStableXa/XBreference—10—msDeviceSkewInputtoOutputPhaseChangeDuetoTem-peratureVariationtTEMPMaxphasechangesfrom–40to+85°C—300500psPLLPerformance(fin=fout=622.

08MHz;BW=120Hz;LVPECL)LockTimetLOCKMPStartofICALtoofLOL—351200msOutputClockPhaseChangetP_STEPAfterclockswitchf3128kHz—200—psClosedLoopJitterPeakingJPK—0.

050.

1dBJitterToleranceJTOLJitterFrequencyLoopBandwidth5000/BW——nspk-pkPhaseNoisefout=622.

08MHzCKOPN1kHzOffset—–106–87dBc/Hz10kHzOffset—–121–100dBc/Hz100kHzOffset—–132–104dBc/Hz1MHzOffset—–132–119dBc/HzSubharmonicNoiseSPSUBHPhaseNoise@100kHzOffset—–88–76dBcSpuriousNoiseSPSPURMaxspur@nxF3(n1,nxF34.

Maximumclockoutputfrequency=1.

4175GHz.

01:N1_HSxNC1_LS>6.

Maximumclockoutputfrequency=808MHz.

10:N1_HSxNC1_LS>14.

Maximumclockoutputfrequency=346MHz.

11:N1_HSxNC1_LS>20.

Maximumclockoutputfrequency=243MHz.

Si531938Rev.

1.

0Resetvalue=00001111Resetvalue=11111111Register138.

BitD7D6D5D4D3D2D1D0NameReservedLOS_EN[1:1]TypeRR/WBitNameFunction7:3ReservedReserved.

0LOS_EN[1:0]EnableCKINLOSMonitoringontheSpecifiedInput(1of2).

Note:LOS_ENissplitbetweentworegisters.

00:DisableLOSmonitoring.

01:Reserved.

10:EnableLOSAmonitoring.

11:EnableLOSmonitoring.

LOSAisaslowerandlesssensitiveversionofLOS.

SeetheFamilyReferenceManualfordetails.

Register139.

BitD7D6D5D4D3D2D1D0NameReservedLOS_EN[0:0]ReservedTypeRR/WRBitNameFunction7:5ReservedReserved.

4LOS_EN[1:0]EnableCKINLOSMonitoringontheSpecifiedInput(1of2).

Note:LOS_ENissplitbetweentworegisters.

00:DisableLOSmonitoring.

01:Reserved.

10:EnableLOSAmonitoring.

11:EnableLOSmonitoring.

LOSAisaslowerandlesssensitiveversionofLOS.

Seethefamilyreferencemanualfordetails.

3:0ReservedReserved.

Si5319Rev.

1.

039Resetvalue=00010011Table9listsalloftheregisterlocationsthatshouldbefollowedbyanICALaftertheircontentsarechanged.

Register185.

BitD7D6D5D4D3D2D1D0NameNVM_REVID[7:0]TypeRBitNameFunction7:0NVM_REVID[7:0]NVM_REVID.

Table8.

CKOUT_ALWAYS_ONandSQ_ICALTruthTableCKOUT_ALWAYS_ONSQ_ICALResults00CKOUTOFFuntilafterthefirstICAL.

01CKOUTOFFuntilafterthefirstsuccessfulICAL(i.

e.

,whenLOLislow).

10CKOUTalwaysON,includingduringanICAL.

11CKOUTalwaysON,includingduringanICAL.

Usethesesettingstopreserveoutput-to-outputskew.

Table9.

RegisterLocationsRequiringICALAddrRegister0BYPASS_REG0CKOUT_ALWAYS_ON2BWSEL_REG5ICMOS10DSBL_REG11PD_CK19VALTIME19LOCKT25N1_HS31NC1_LS40N2_HS40N2_LS43N31Si531940Rev.

1.

05.

PinDescriptions:Si5319Pin#PinNameI/OSignalLevelDescription1RSTILVCMOSExternalReset.

Activelowinputthatperformsexternalhardwareresetofdevice.

Resetsallinternallogictoaknownstateandforcesthedeviceregis-terstotheirdefaultvalue.

Clockoutputsaredisabledduringreset.

Thepartmustbeprogrammedafteraresetorpower-ontogetaclockout-put.

SeeFamilyReferenceManualfordetails.

Thispinhasaweakpull-up.

2,4,9,12–14,30,33–35NC——NoConnection.

Leavefloating.

Makenoexternalconnectionstothispinfornormaloperation.

3INT_CBOLVCMOSInterrupt/CKINInvalidIndicator.

ThispinfunctionsasadeviceinterruptoutputoranalarmoutputforCKIN.

Ifusedasaninterruptoutput,INT_PINmustbesetto1.

ThepinfunctionsasamaskableinterruptoutputwithactivepolaritycontrolledbytheINT_POLregisterbit.

Ifusedasanalarmoutput,thepinfunctionsasaLOSalarmindicatorforCKIN.

SetCK_BAD_PIN=1andINT_PIN=0.

0=CKINpresent.

1=LOSonCKIN.

TheactivepolarityiscontrolledbyCK_BAD_POL.

Ifnofunctionisselected,thepintristates.

5,10,32VDDVDDSupplySupply.

Thedeviceoperatesfroma1.

8,2.

5,or3.

3Vsupply.

Bypasscapaci-torsshouldbeassociatedwiththefollowingVDDpins:50.

1μF100.

1μF320.

1μFA1.

0μFshouldalsobeplacedasclosetothedeviceasispractical.

Note:Internalregisternamesareindicatedbyunderlineditalics(e.

g.

,INT_PIN.

SeeSi5319RegisterMap).

Si5319Rev.

1.

04176XBXAIAnalogExternalCrystalorReferenceClock.

Externalcrystalshouldbeconnectedtothesepinstouseinternaloscillatorbasedreference.

RefertotheFamilyReferenceManualforinterfacingtoanexternalreference.

Theexternalreferencemustbefromahigh-qualityclocksource(TCXO,OCXO).

FrequencyofcrystalorexternalclockissetbytheRATEpins.

8,3119,20GNDGNDSupplyGround.

Mustbeconnectedtosystemground.

Minimizethegroundpathimpedanceforoptimalperformanceofthisdevice.

GroundingthesepinsdoesnoteliminatetherequirementtogroundtheGNDPADonthebottomofthepackage.

1115RATE0RATE1I3-LevelExternalCrystalorReferenceClockRate.

ThreelevelinputsthatselectthetypeandrateofexternalcrystalorreferenceclocktobeappliedtotheXA/XBport.

RefertotheFamilyReferenceManualforsettings.

Thesepinshavebothaweakpull-upandaweakpull-down;theydefaulttoM.

The"HH"settingisnotsup-ported.

Note:Lsettingcorrespondstoground.

MsettingcorrespondstoVDD/2.

HsettingcorrespondstoVDD.

Somedesignsmayrequireanexternalresistorvoltagedividerwhendrivenbyanactivedevicethatwilltri-state.

1617CKIN+CKIN–IMultiClockInput.

Differentialinputclock.

Thisinputcanalsobedrivenwithasingle-endedsignal.

Inputfrequencyrangeis2kHzto710MHz.

18LOLOLVCMOSPLLLossofLockIndicator.

ThispinfunctionsastheactivehighPLLlossoflockindicatoriftheLOL_PINregisterbitissetto1.

0=PLLlocked.

1=PLLunlocked.

IfLOL_PIN=0,thispinwilltristate.

ActivepolarityiscontrolledbytheLOL_POLbit.

ThePLLlockstatuswillalwaysbereflectedintheLOL_INTreadonlyregisterbit.

21CSILVCMOSXtal/InputClockSelect.

ThispinselectstheactiveDSPLLinputclock,whichcanbeaclockinputoracrystalinput.

SeetheFREE_ENregisterforfreerunsettings.

0=Selectclockinput(CKIN).

1=Selectcrystalorexternalreferenceclock.

Thispinshouldnotbeleftopen.

22SCLILVCMOSSerialClock/SerialClock.

ThispinfunctionsastheserialclockinputforbothSPIandI2Cmodes.

Thispinhasaweakpull-down.

23SDA_SDOI/OLVCMOSSerialData.

InI2Ccontrolmode(CMODE=0),thispinfunctionsasthebidirec-tionalserialdataport.

InSPIcontrolmode(CMODE=1),thispinfunctionsastheserialdataoutput.

Pin#PinNameI/OSignalLevelDescriptionNote:Internalregisternamesareindicatedbyunderlineditalics(e.

g.

,INT_PIN.

SeeSi5319RegisterMap).

Si531942Rev.

1.

02524A1A0ILVCMOSSerialPortAddress.

InI2Ccontrolmode(CMODE=0),thesepinsfunctionashardwarecontrolledaddressbits.

TheI2Caddressis1101[A2][A1][A0].

InSPIcontrolmode(CMODE=1),thesepinsareignored.

Thesepinshaveaweakpull-down.

26A2_SSILVCMOSSerialPortAddress/SlaveSelect.

InI2Ccontrolmode(CMODE=0),thispinfunctionsasahardwarecontrolledaddressbit[A2].

InSPIcontrolmode(CMODE=1),thispinfunctionsastheslaveselectinput.

Thispinhasaweakpull-down.

27SDIILVCMOSSerialDataIn.

InI2Ccontrolmode(CMODE=0),thispinisignored.

InSPIcontrolmode(CMODE=1),thispinfunctionsastheserialdatainput.

Thispinhasaweakpull-down.

2928CKOUT–CKOUT+OMultiOutputClock.

Differentialoutputclockwithafrequencyrangeof10MHzto1.

4175GHz.

OutputsignalformatisselectedbySFOUT1_REGregis-terbits.

OutputisdifferentialforLVPECL,LVDS,andCMLcompatiblemodes.

ForCMOSformat,bothoutputpinsdriveidenticalsingle-endedclockoutputs.

36CMODEILVCMOSControlMode.

SelectsI2CorSPIcontrolmodefortheSi5319.

0=I2CControlMode1=SPIControlModeGNDPADGNDGNDSupplyGroundPad.

Thegroundpadmustprovidealowthermalandelectricalimpedancetoagroundplane.

Pin#PinNameI/OSignalLevelDescriptionNote:Internalregisternamesareindicatedbyunderlineditalics(e.

g.

,INT_PIN.

SeeSi5319RegisterMap).

Si5319Rev.

1.

0436.

OrderingGuideOrderingPartNumberOutputClockFrequencyRangePackageROHS6,Pb-FreeTemperatureRangeSi5319A-C-GM2kHz–945MHz970–1134MHz1.

213–1.

417GHz36-Lead6x6mmQFNYes–40to85°CSi5319B-C-GM2kHz–808MHz36-Lead6x6mmQFNYes–40to85°CSi5319C-C-GM2kHz–346MHz36-Lead6x6mmQFNYes–40to85°CNote:AddanRattheendofthedevicepartnumbertodenotetapeandreelorderingoptions.

Si531944Rev.

1.

07.

PackageOutline:36-PinQFNFigure6illustratesthepackagedetailsfortheSi5319.

Table10liststhevaluesforthedimensionsshownintheillustration.

Figure6.

36-PinQuadFlatNo-lead(QFN)Table10.

PackageDimensionsSymbolMillimetersSymbolMillimetersMinNomMaxMinNomMaxA0.

800.

850.

90L0.

500.

600.

70A10.

000.

020.

05——12b0.

180.

250.

30aaa——0.

10D6.

00BSCbbb——0.

10D23.

954.

104.

25ccc——0.

08e0.

50BSCddd——0.

10E6.

00BSCeee——0.

05E23.

954.

104.

25Notes:1.

Alldimensionsshownareinmillimeters(mm)unlessotherwisenoted.

2.

DimensioningandTolerancingperANSIY14.

5M-1994.

3.

ThisdrawingconformstoJEDECoutlineMO-220,variationVJJD.

4.

RecommendedcardreflowprofileispertheJEDEC/IPCJ-STD-020specificationforSmallBodyComponents.

Si5319Rev.

1.

0458.

RecommendedPCBLayoutFigure7.

PCBLandPatternDiagramFigure8.

GroundPadRecommendedLayoutSi531946Rev.

1.

0Table11.

PCBLandPatternDimensionsDimensionMINMAXe0.

50BSC.

E5.

42REF.

D5.

42REF.

E24.

004.

20D24.

004.

20GE4.

53—GD4.

53—X—0.

28Y0.

89REF.

ZE—6.

31ZD—6.

31Notes(General):1.

Alldimensionsshownareinmillimeters(mm)unlessotherwisenoted.

2.

DimensioningandTolerancingispertheANSIY14.

5M-1994specification.

3.

ThisLandPatternDesignisbasedonIPC-SM-782guidelines.

4.

AlldimensionsshownareatMaximumMaterialCondition(MMC).

LeastMaterialCondition(LMC)iscalculatedbasedonaFabricationAllowanceof0.

05mm.

Notes(SolderMaskDesign):1.

Allmetalpadsaretobenon-soldermaskdefined(NSMD).

Clearancebetweenthesoldermaskandthemetalpadistobe60μmminimum,allthewayaroundthepad.

Notes(StencilDesign):1.

Astainlesssteel,laser-cutandelectro-polishedstencilwithtrapezoidalwallsshouldbeusedtoassuregoodsolderpasterelease.

2.

Thestencilthicknessshouldbe0.

125mm(5mils).

3.

Theratioofstencilaperturetolandpadsizeshouldbe1:1fortheperimeterpads.

4.

A4x4arrayof0.

80mmsquareopeningson1.

05mmpitchshouldbeusedforthecentergroundpad.

Notes(CardAssembly):1.

ANo-Clean,Type-3solderpasteisrecommended.

2.

TherecommendedcardreflowprofileispertheJEDEC/IPCJ-STD-020specificationforSmallBodyComponents.

Si5319Rev.

1.

0479.

Si5319DeviceTopMarkMarkMethod:LaserFontSize:0.

80mmRight-JustifiedLine1Marking:Si5319CustomerPartNumberQ=SpeedCode:A,B,CSeeOrderingGuideforoptionsLine2Marking:C-GMC=ProductRevisionG=TemperatureRange–40to85°C(RoHS6)M=QFNPackageLine3Marking:YYWWRFYY=YearWW=WorkWeekR=DieRevisionF=InternalcodeAssignedbytheAssemblyHouse.

Correspondstotheyearandworkweekofthemolddate.

Line4Marking:Pin1IdentifierCircle=0.

75mmDiameterLower-LeftJustifiedXXXXInternalCodeSi531948Rev.

1.

0DOCUMENTCHANGELISTRevision0.

1toRevision0.

2Changed1.

8Voperatingrangeto±5%.

UpdatedTable1onpage4.

UpdatedTable2onpage5.

AddedtableunderFigure3onpage14.

Updated"3.

FunctionalDescription"onpage16.

Clarified"5.

PinDescriptions:Si5319"onpage40.

Revision0.

2toRevision0.

3Updated"5.

PinDescriptions:Si5319"onpage40.

CorrectedPins11and15descriptionintable.

Revision0.

3toRevision0.

4UpdatedTable1onpage4.

Added"9.

Si5319DeviceTopMark"onpage47.

Revision0.

4toRevision0.

41UpdatedTable1onpage4.

UpdatedThermalResistanceJunctiontoAmbienttypicalspecification.

UpdatedFigure4,"Si5319TypicalApplicationCircuit(I2CControlMode),"onpage15.

UpdatedFigure5,"Si5319TypicalApplicationCircuit(SPIControlMode),"onpage15.

UpdatedNCpindescriptionin"5.

PinDescriptions:Si5319"onpage40.

Updated"7.

PackageOutline:36-PinQFN"onpage44.

AddedFigure8,"GroundPadRecommendedLayout,"onpage45.

Addedregistermapdocumentation.

UpdatedRise/FallTimevalues.

Revision0.

41toRevision0.

42Changedregisteraddresslabelstodecimal.

Revision0.

42toRevision0.

43Updatedthefollowing:ESDspecificationsphasenoisevaluesabsoluteVddmaximumvoltagetypicalphasenoiseplotAddedspecificationforphasechangesduetotemperaturevariationAddedinformationfortheN32registerAddedJCspecificationRevision0.

43toRevision1.

0Replacedthespecificationtables(tables1and2fromrev.

0.

43)withthespecificationtablesfromtheSi53xReferenceManual,rev0.

42.

Si5319Rev.

1.

049NOTES:DisclaimerSiliconLaboratoriesintendstoprovidecustomerswiththelatest,accurate,andin-depthdocumentationofallperipheralsandmodulesavailableforsystemandsoftwareimplementersusingorintendingtousetheSiliconLaboratoriesproducts.

Characterizationdata,availablemodulesandperipherals,memorysizesandmemoryaddressesrefertoeachspecificdevice,and"Typical"parametersprovidedcananddovaryindifferentapplications.

Applicationexamplesdescribedhereinareforillustrativepurposesonly.

SiliconLaboratoriesreservestherighttomakechangeswithoutfurthernoticeandlimitationtoproductinformation,specifications,anddescriptionsherein,anddoesnotgivewarrantiesastotheaccuracyorcompletenessoftheincludedinformation.

SiliconLaboratoriesshallhavenoliabilityfortheconsequencesofuseoftheinformationsuppliedherein.

Thisdocumentdoesnotimplyorexpresscopyrightlicensesgrantedhereundertodesignorfabricateanyintegratedcircuits.

TheproductsmustnotbeusedwithinanyLifeSupportSystemwithoutthespecificwrittenconsentofSiliconLaboratories.

A"LifeSupportSystem"isanyproductorsystemintendedtosupportorsustainlifeand/orhealth,which,ifitfails,canbereasonablyexpectedtoresultinsignificantpersonalinjuryordeath.

SiliconLaboratoriesproductsaregenerallynotintendedformilitaryapplications.

SiliconLaboratoriesproductsshallundernocircumstancesbeusedinweaponsofmassdestructionincluding(butnotlimitedto)nuclear,biologicalorchemicalweapons,ormissilescapableofdeliveringsuchweapons.

TrademarkInformationSiliconLaboratoriesInc.

,SiliconLaboratories,SiliconLabs,SiLabsandtheSiliconLabslogo,CMEMS,EFM,EFM32,EFR,EnergyMicro,EnergyMicrologoandcombinationsthereof,"theworld'smostenergyfriendlymicrocontrollers",Ember,EZLink,EZMac,EZRadio,EZRadioPRO,DSPLL,ISOmodem,Precision32,ProSLIC,SiPHY,USBXpressandothersaretrademarksorregisteredtrademarksofSiliconLaboratoriesInc.

ARM,CORTEX,Cortex-M3andTHUMBaretrademarksorregisteredtrademarksofARMHoldings.

KeilisaregisteredtrademarkofARMLimited.

Allotherproductsorbrandnamesmentionedhereinaretrademarksoftheirrespectiveholders.

http://www.

silabs.

comSiliconLaboratoriesInc.

400WestCesarChavezAustin,TX78701USAClockBuilderProOne-clickaccesstoTimingtools,documentation,software,sourcecodelibraries&more.

AvailableforWindowsandiOS(CBGoonly).

www.

silabs.

com/CBProTimingPortfoliowww.

silabs.

com/timingSW/HWwww.

silabs.

com/CBProQualitywww.

silabs.

com/qualitySupportandCommunitycommunity.

silabs.

com

1.

012/10Copyright2010bySiliconLaboratoriesSi5319Si5319FeaturesGeneratesanyfrequencyfrom2kHzto945MHzandselectfrequenciesto1.

4GHzfromaninputfrequencyof2kHzto710MHzUltra-lowjitterclockoutputwithjittergenerationaslowas0.

3psrms(50kHz–80MHz)Integratedloopfilterwithselectableloopbandwidth(60Hzto8.

4kHz)MeetsOC-192GR-253-COREjitterspecificationsClockorcrystalinputwithmanualclockselectionSelectableclockoutputsignalformat(LVPECL,LVDS,CML,CMOS)SupportforITUG.

709andcustomOTNFECratios(e.

g.

255/238,255/237,255/236)SupportsvariousfrequencytranslationsforSynchronousEthernetLOL,LOSalarmoutputsI2CorSPIprogrammableOn-chipvoltageregulatorfor1.

8V±5%,2.

5V±10%or3.

3V±10%operationSmallsize:6x6mm36-leadQFNPb-free,ROHScompliantApplications10G/40G/100GOTNlinecardsSONET/SDHOC-48/STM-16andOC-192/STM-64linecardsGbE/10GbE,1/2/4/8/10GFClinecardsITUG.

709andcustomFEClinecardsSynchronousEthernetOpticalmodulesWirelessbasestationsDataconverterclockingDSLAM/MSANsTestandmeasurementBroadcastvideoDiscretePLLreplacementDescriptionTheSi5319isajitter-attenuatingprecisionM/Nclockmultiplierforapplicationsrequiringsub1psjitterperformance.

TheSi5319acceptsoneclockinputrangingfrom2kHzto710MHzandgeneratesoneclockoutputrangingfrom2kHzto945MHzandselectfrequenciesto1.

4GHz.

TheSi5319canalsouseitscrystaloscillatorasaclocksourceforfree-runningclockgeneration.

Thedeviceprovidesvirtuallyanyfrequencytranslationcombinationacrossthisoperatingrange.

TheSi5319inputclockfrequencyandclockmultiplicationratioareprogrammablethroughanI2CorSPIinterface.

TheSi5319isbasedonSiliconLaboratories'third-generationDSPLLtechnology,whichprovidesany-frequencysynthesisandjitterattenuationinahighlyintegratedPLLsolutionthateliminatestheneedforexternalVCXOandloopfiltercomponents.

TheDSPLLloopbandwidthisdigitallyprogrammable,providingjitterperformanceoptimizationattheapplicationlevel.

Operatingfromasingle1.

8,2.

5,or3.

3Vsupply,theSi5319isidealforprovidingclockmultiplicationandjitterattenuationinhighperformancetimingapplications.

ANY-FREQUENCYPRECISIONCLOCKMULTIPLIER/JITTERATTENUATORSi53192Rev.

1.

0Si5319Rev.

1.

03TABLEOFCONTENTSSectionPage1.

ElectricalSpecifications42.

TypicalPhaseNoisePlots142.

1.

Example:SONETOC-192143.

FunctionalDescription163.

1.

ExternalReference163.

2.

FurtherDocumentation164.

RegisterMap175.

PinDescriptions:Si5319406.

OrderingGuide437.

PackageOutline:36-PinQFN448.

RecommendedPCBLayout459.

Si5319DeviceTopMark47DocumentChangeList48ContactInformation50Si53194Rev.

1.

01.

ElectricalSpecificationsFigure1.

DifferentialVoltageCharacteristicsFigure2.

Rise/FallTimeCharacteristicsTable1.

RecommendedOperatingConditionsParameterSymbolTestConditionMinTypMaxUnitAmbientTemperatureTA-402585°CSupplyVoltageduringNormalOperationVDD3.

3VNominal2.

973.

33.

63V2.

5VNominal2.

252.

52.

75V1.

8VNominal1.

711.

81.

89VNote:Allminimumandmaximumspecificationsareguaranteedandapplyacrosstherecommendedoperatingconditions.

Typicalvaluesapplyatnominalsupplyvoltagesandanoperatingtemperatureof25Cunlessotherwisestated.

Si5319Rev.

1.

05Table2.

DCCharacteristics(VDD=1.

8±5%,2.

5±10%,or3.

3V±10%,TA=–40to85°C)ParameterSymbolTestConditionMinTypMaxUnitSupplyCurrent1IDDLVPECLFormat622.

08MHzOut—217243mACMOSFormat19.

44MHzOut—194220mADisableMode—165—mACKINInputPin2InputCommonModeVoltage(InputThresh-oldVoltage)VICM1.

8V±5%0.

9—1.

4V2.

5V±10%1—1.

7V3.

3V±10%1.

1—1.

95VInputResistanceCKNRINSingle-ended204060kΩSingle-EndedInputVoltageSwing(SeeAbsoluteSpecs)VISEfCKIN212.

5MHzSeeFigure1.

0.

25——VPPDifferentialInputVoltageSwing(SeeAbsoluteSpecs)VIDfCKIN212.

5MHzSeeFigure1.

0.

25——VPPOutputClock(CKOUT)3CommonModeCKOVCMLVPECL100loadline-to-lineVDD–1.

42—VDD–1.

25VDifferentialOutputSwingCKOVDLVPECL100loadline-to-line1.

1—1.

9VPPSingleEndedOutputSwingCKOVSELVPECL100loadline-to-line0.

5—0.

93VPPDifferentialOutputVoltageCKOVDCML100loadline-to-line350425500mVPPNotes:1.

Currentdrawisindependentofsupplyvoltage.

2.

Nounder-orovershootisallowed.

3.

LVPECLoutputsrequirenominalVDD≥2.

5V.

4.

Thisistheamountofleakagethatthe3-levelinputscantoleratefromanexternaldriver.

SeeSi53xxFamilyReferenceManualformoredetails.

5.

LVPECL,CML,LVDSandlow-swingLVDSmeasuredwithFo=622.

08MHz.

Si53196Rev.

1.

0CommonModeOutputVoltageCKOVCMCML100loadline-to-line—VDD–0.

36—VDifferentialOutputVoltageCKOVDLVDS100loadline-to-line500700900mVPPLowSwingLVDS100loadline-to-line350425500mVPPCommonModeOutputVoltageCKOVCMLVDS100loadline-to-line1.

1251.

21.

275VDifferentialOutputResistanceCKORDCML,LVPECL,LVDS—200—OutputVoltageLowCKOVOLLHCMOS——0.

4VOutputVoltageHighCKOVOHLHVDD=1.

71VCMOS0.

8xVDD——VOutputDriveCurrent(CMOSdrivingintoCKOVOLforoutputloworCKOVOHforoutputhigh.

CKOUT+andCKOUT–shortedexternally)CKOIOICMOS[1:0]=11VDD=1.

8V—7.

5—mAICMOS[1:0]=10VDD=1.

8V—5.

5—mAICMOS[1:0]=01VDD=1.

8V—3.

5—mAICMOS[1:0]=00VDD=1.

8V—1.

75—mAICMOS[1:0]=11VDD=3.

3V—32—mAICMOS[1:0]=10VDD=3.

3V—24—mAICMOS[1:0]=01VDD=3.

3V—16—mAICMOS[1:0]=00VDD=3.

3V—8—mATable2.

DCCharacteristics(Continued)(VDD=1.

8±5%,2.

5±10%,or3.

3V±10%,TA=–40to85°C)ParameterSymbolTestConditionMinTypMaxUnitNotes:1.

Currentdrawisindependentofsupplyvoltage.

2.

Nounder-orovershootisallowed.

3.

LVPECLoutputsrequirenominalVDD≥2.

5V.

4.

Thisistheamountofleakagethatthe3-levelinputscantoleratefromanexternaldriver.

SeeSi53xxFamilyReferenceManualformoredetails.

5.

LVPECL,CML,LVDSandlow-swingLVDSmeasuredwithFo=622.

08MHz.

Si5319Rev.

1.

072-LevelLVCMOSInputPinsInputVoltageLowVILVDD=1.

71V——0.

5VVDD=2.

25V——0.

7VVDD=2.

97V——0.

8VInputVoltageHighVIHVDD=1.

89V1.

4——VVDD=2.

25V1.

8——VVDD=3.

63V2.

5——V3-LevelInputPins4InputVoltageLowVILL——0.

15xVDDVInputVoltageMidVIMM0.

45xVDD—0.

55xVDDVInputVoltageHighVIHH0.

85xVDD——VInputLowCurrentIILLSeeNote4–20——μAInputMidCurrentIIMMSeeNote4–2—+2μAInputHighCurrentIIHHSeeNote4——20μALVCMOSOutputPinsOutputVoltageLowVOLIO=2mAVDD=1.

71V——0.

4VOutputVoltageLowIO=2mAVDD=2.

97V——0.

4VTable2.

DCCharacteristics(Continued)(VDD=1.

8±5%,2.

5±10%,or3.

3V±10%,TA=–40to85°C)ParameterSymbolTestConditionMinTypMaxUnitNotes:1.

Currentdrawisindependentofsupplyvoltage.

2.

Nounder-orovershootisallowed.

3.

LVPECLoutputsrequirenominalVDD≥2.

5V.

4.

Thisistheamountofleakagethatthe3-levelinputscantoleratefromanexternaldriver.

SeeSi53xxFamilyReferenceManualformoredetails.

5.

LVPECL,CML,LVDSandlow-swingLVDSmeasuredwithFo=622.

08MHz.

Si53198Rev.

1.

0OutputVoltageHighVOHIO=–2mAVDD=1.

71VVDD–0.

4——VOutputVoltageHighIO=–2mAVDD=2.

97VVDD–0.

4——VDisabledLeakageCurrentIOZRSTb=0–100—100μATable3.

MicroprocessorControl(VDD=1.

8±5%,2.

5±10%,or3.

3V±10%,TA=–40to85°C)ParameterSymbolTestConditionMinTypMaxUnitI2CBusLines(SDA,SCL)InputVoltageLowVILI2C——0.

25xVDDVInputVoltageHighVIHI2C0.

7xVDD—VDDVInputCurrentIII2CVIN=0.

1xVDDto0.

9xVDD–10—10μAHysteresisofSchmitttriggerinputsVHYSI2CVDD=1.

8V0.

1xVDD——VVDD=2.

5or3.

3V0.

05xVDD——VOutputVoltageLowVOLI2CVDD=1.

8VIO=3mA——0.

2xVDDVVDD=2.

5or3.

3VIO=3mA——0.

4VSPISpecificationsDutyCycle,SCLKtDCSCLK=10MHz40—60%CycleTime,SCLKtc100——nsRiseTime,SCLKtr20–80%——25nsFallTime,SCLKtf20–80%——25nsTable2.

DCCharacteristics(Continued)(VDD=1.

8±5%,2.

5±10%,or3.

3V±10%,TA=–40to85°C)ParameterSymbolTestConditionMinTypMaxUnitNotes:1.

Currentdrawisindependentofsupplyvoltage.

2.

Nounder-orovershootisallowed.

3.

LVPECLoutputsrequirenominalVDD≥2.

5V.

4.

Thisistheamountofleakagethatthe3-levelinputscantoleratefromanexternaldriver.

SeeSi53xxFamilyReferenceManualformoredetails.

5.

LVPECL,CML,LVDSandlow-swingLVDSmeasuredwithFo=622.

08MHz.

Si5319Rev.

1.

09LowTime,SCLKtlsc20–20%30——nsHighTime,SCLKthsc80–80%30——nsDelayTime,SCLKFalltoSDOActivetd1——25nsDelayTime,SCLKFalltoSDOTransitiontd2——25nsDelayTime,SSRisetoSDOTri-statetd3——25nsSetupTime,SStoSCLKFalltsu125——nsHoldTime,SStoSCLKRiseth120——nsSetupTime,SDItoSCLKRisetsu225——nsHoldTime,SDItoSCLKRiseth220——nsDelayTimebetweenSlaveSelectstcs25——nsTable4.

ACSpecifications(VDD=1.

8±5%,2.

5±10%,or3.

3V±10%,TA=–40to85°C)ParameterSymbolTestConditionMinTypMaxUnitSingle-EndedReferenceClockInputPinXA(XBwithcaptoGND)InputResistanceXARINRATE[1:0]=LMorMH,accoupled—12—kInputVoltageSwingXAVPPRATE[1:0]=LMorMH,accoupled0.

5—1.

2VPPDifferentialReferenceClockInputPins(XA/XB)InputVoltageSwingXA/XBVPPRATE[1:0]=LMorMH0.

5—1.

2VPP,each.

CKINInputPinsInputFrequencyCKNF0.

002—710MHzTable3.

MicroprocessorControl(Continued)(VDD=1.

8±5%,2.

5±10%,or3.

3V±10%,TA=–40to85°C)ParameterSymbolTestConditionMinTypMaxUnitSi531910Rev.

1.

0InputDutyCycle(MinimumPulseWidth)CKNDCWhicheverissmaller(i.

e.

,the40%/60%limitationappliesonlytohigh-frequencyclocks)40—60%2——nsInputCapacitanceCKNCIN——3pFInputRise/FallTimeCKNTRF20–80%SeeFigure2——11nsCKOUTOutputPins(Seeorderingsectionforspeedgradevsfrequencylimits)OutputFrequency(Outputnotconfig-uredforCMOSorDisabled)CKOFN160.

002—945MHzN1=5970—1134MHzN1=41.

213—1.

4GHzMaximumOutputFrequencyinCMOSFormatCKOF——212.

5MHzOutputRise/Fall(20–80%)@622.

08MHzoutputCKOTRFOutputnotconfiguredforCMOSorDisabledSeeFigure2—230350psOutputRise/Fall(20–80%)@212.

5MHzoutputCKOTRFCMOSOutputVDD=1.

71CLOAD=5pF——8nsOutputRise/Fall(20–80%)@212.

5MHzoutputCKOTRFCMOSOutputVDD=2.

97CLOAD=5pF——2nsOutputDutyCycleUncertainty@622.

08MHzCKODC100LoadLine-to-LineMeasuredat50%Point(NotforCMOS)——+/-40psLVCMOSInputPinsMinimumResetPulseWidthtRSTMN1——μsResettoMicroproces-sorAccessReadytREADY——10msInputCapacitanceCin——3pFTable4.

ACSpecifications(Continued)(VDD=1.

8±5%,2.

5±10%,or3.

3V±10%,TA=–40to85°C)ParameterSymbolTestConditionMinTypMaxUnitSi5319Rev.

1.

011LVCMOSOutputPinsRise/FallTimestRFCLOAD=20pfSeeFigure2—25—nsLOSnTriggerWindowLOSTRIGFromlastCKINntoInternaldetectionofLOSnN3≠1——4.

5xN3TCKINTimetoClearLOLafterLOSClearedtCLRLOLLOStoLOLFold=FnewStableXa/XBreference—10—msDeviceSkewInputtoOutputPhaseChangeDuetoTem-peratureVariationtTEMPMaxphasechangesfrom–40to+85°C—300500psPLLPerformance(fin=fout=622.

08MHz;BW=120Hz;LVPECL)LockTimetLOCKMPStartofICALtoofLOL—351200msOutputClockPhaseChangetP_STEPAfterclockswitchf3128kHz—200—psClosedLoopJitterPeakingJPK—0.

050.

1dBJitterToleranceJTOLJitterFrequencyLoopBandwidth5000/BW——nspk-pkPhaseNoisefout=622.

08MHzCKOPN1kHzOffset—–106–87dBc/Hz10kHzOffset—–121–100dBc/Hz100kHzOffset—–132–104dBc/Hz1MHzOffset—–132–119dBc/HzSubharmonicNoiseSPSUBHPhaseNoise@100kHzOffset—–88–76dBcSpuriousNoiseSPSPURMaxspur@nxF3(n1,nxF34.

Maximumclockoutputfrequency=1.

4175GHz.

01:N1_HSxNC1_LS>6.

Maximumclockoutputfrequency=808MHz.

10:N1_HSxNC1_LS>14.

Maximumclockoutputfrequency=346MHz.

11:N1_HSxNC1_LS>20.

Maximumclockoutputfrequency=243MHz.

Si531938Rev.

1.

0Resetvalue=00001111Resetvalue=11111111Register138.

BitD7D6D5D4D3D2D1D0NameReservedLOS_EN[1:1]TypeRR/WBitNameFunction7:3ReservedReserved.

0LOS_EN[1:0]EnableCKINLOSMonitoringontheSpecifiedInput(1of2).

Note:LOS_ENissplitbetweentworegisters.

00:DisableLOSmonitoring.

01:Reserved.

10:EnableLOSAmonitoring.

11:EnableLOSmonitoring.

LOSAisaslowerandlesssensitiveversionofLOS.

SeetheFamilyReferenceManualfordetails.

Register139.

BitD7D6D5D4D3D2D1D0NameReservedLOS_EN[0:0]ReservedTypeRR/WRBitNameFunction7:5ReservedReserved.

4LOS_EN[1:0]EnableCKINLOSMonitoringontheSpecifiedInput(1of2).

Note:LOS_ENissplitbetweentworegisters.

00:DisableLOSmonitoring.

01:Reserved.

10:EnableLOSAmonitoring.

11:EnableLOSmonitoring.

LOSAisaslowerandlesssensitiveversionofLOS.

Seethefamilyreferencemanualfordetails.

3:0ReservedReserved.

Si5319Rev.

1.

039Resetvalue=00010011Table9listsalloftheregisterlocationsthatshouldbefollowedbyanICALaftertheircontentsarechanged.

Register185.

BitD7D6D5D4D3D2D1D0NameNVM_REVID[7:0]TypeRBitNameFunction7:0NVM_REVID[7:0]NVM_REVID.

Table8.

CKOUT_ALWAYS_ONandSQ_ICALTruthTableCKOUT_ALWAYS_ONSQ_ICALResults00CKOUTOFFuntilafterthefirstICAL.

01CKOUTOFFuntilafterthefirstsuccessfulICAL(i.

e.

,whenLOLislow).

10CKOUTalwaysON,includingduringanICAL.

11CKOUTalwaysON,includingduringanICAL.

Usethesesettingstopreserveoutput-to-outputskew.

Table9.

RegisterLocationsRequiringICALAddrRegister0BYPASS_REG0CKOUT_ALWAYS_ON2BWSEL_REG5ICMOS10DSBL_REG11PD_CK19VALTIME19LOCKT25N1_HS31NC1_LS40N2_HS40N2_LS43N31Si531940Rev.

1.

05.

PinDescriptions:Si5319Pin#PinNameI/OSignalLevelDescription1RSTILVCMOSExternalReset.

Activelowinputthatperformsexternalhardwareresetofdevice.

Resetsallinternallogictoaknownstateandforcesthedeviceregis-terstotheirdefaultvalue.

Clockoutputsaredisabledduringreset.

Thepartmustbeprogrammedafteraresetorpower-ontogetaclockout-put.

SeeFamilyReferenceManualfordetails.

Thispinhasaweakpull-up.

2,4,9,12–14,30,33–35NC——NoConnection.

Leavefloating.

Makenoexternalconnectionstothispinfornormaloperation.

3INT_CBOLVCMOSInterrupt/CKINInvalidIndicator.

ThispinfunctionsasadeviceinterruptoutputoranalarmoutputforCKIN.

Ifusedasaninterruptoutput,INT_PINmustbesetto1.

ThepinfunctionsasamaskableinterruptoutputwithactivepolaritycontrolledbytheINT_POLregisterbit.

Ifusedasanalarmoutput,thepinfunctionsasaLOSalarmindicatorforCKIN.

SetCK_BAD_PIN=1andINT_PIN=0.

0=CKINpresent.

1=LOSonCKIN.

TheactivepolarityiscontrolledbyCK_BAD_POL.

Ifnofunctionisselected,thepintristates.

5,10,32VDDVDDSupplySupply.

Thedeviceoperatesfroma1.

8,2.

5,or3.

3Vsupply.

Bypasscapaci-torsshouldbeassociatedwiththefollowingVDDpins:50.

1μF100.

1μF320.

1μFA1.

0μFshouldalsobeplacedasclosetothedeviceasispractical.

Note:Internalregisternamesareindicatedbyunderlineditalics(e.

g.

,INT_PIN.

SeeSi5319RegisterMap).

Si5319Rev.

1.

04176XBXAIAnalogExternalCrystalorReferenceClock.

Externalcrystalshouldbeconnectedtothesepinstouseinternaloscillatorbasedreference.

RefertotheFamilyReferenceManualforinterfacingtoanexternalreference.

Theexternalreferencemustbefromahigh-qualityclocksource(TCXO,OCXO).

FrequencyofcrystalorexternalclockissetbytheRATEpins.

8,3119,20GNDGNDSupplyGround.

Mustbeconnectedtosystemground.

Minimizethegroundpathimpedanceforoptimalperformanceofthisdevice.

GroundingthesepinsdoesnoteliminatetherequirementtogroundtheGNDPADonthebottomofthepackage.

1115RATE0RATE1I3-LevelExternalCrystalorReferenceClockRate.

ThreelevelinputsthatselectthetypeandrateofexternalcrystalorreferenceclocktobeappliedtotheXA/XBport.

RefertotheFamilyReferenceManualforsettings.

Thesepinshavebothaweakpull-upandaweakpull-down;theydefaulttoM.

The"HH"settingisnotsup-ported.

Note:Lsettingcorrespondstoground.

MsettingcorrespondstoVDD/2.

HsettingcorrespondstoVDD.

Somedesignsmayrequireanexternalresistorvoltagedividerwhendrivenbyanactivedevicethatwilltri-state.

1617CKIN+CKIN–IMultiClockInput.

Differentialinputclock.

Thisinputcanalsobedrivenwithasingle-endedsignal.

Inputfrequencyrangeis2kHzto710MHz.

18LOLOLVCMOSPLLLossofLockIndicator.

ThispinfunctionsastheactivehighPLLlossoflockindicatoriftheLOL_PINregisterbitissetto1.

0=PLLlocked.

1=PLLunlocked.

IfLOL_PIN=0,thispinwilltristate.

ActivepolarityiscontrolledbytheLOL_POLbit.

ThePLLlockstatuswillalwaysbereflectedintheLOL_INTreadonlyregisterbit.

21CSILVCMOSXtal/InputClockSelect.

ThispinselectstheactiveDSPLLinputclock,whichcanbeaclockinputoracrystalinput.

SeetheFREE_ENregisterforfreerunsettings.

0=Selectclockinput(CKIN).

1=Selectcrystalorexternalreferenceclock.

Thispinshouldnotbeleftopen.

22SCLILVCMOSSerialClock/SerialClock.

ThispinfunctionsastheserialclockinputforbothSPIandI2Cmodes.

Thispinhasaweakpull-down.

23SDA_SDOI/OLVCMOSSerialData.

InI2Ccontrolmode(CMODE=0),thispinfunctionsasthebidirec-tionalserialdataport.

InSPIcontrolmode(CMODE=1),thispinfunctionsastheserialdataoutput.

Pin#PinNameI/OSignalLevelDescriptionNote:Internalregisternamesareindicatedbyunderlineditalics(e.

g.

,INT_PIN.

SeeSi5319RegisterMap).

Si531942Rev.

1.

02524A1A0ILVCMOSSerialPortAddress.

InI2Ccontrolmode(CMODE=0),thesepinsfunctionashardwarecontrolledaddressbits.

TheI2Caddressis1101[A2][A1][A0].

InSPIcontrolmode(CMODE=1),thesepinsareignored.

Thesepinshaveaweakpull-down.

26A2_SSILVCMOSSerialPortAddress/SlaveSelect.

InI2Ccontrolmode(CMODE=0),thispinfunctionsasahardwarecontrolledaddressbit[A2].

InSPIcontrolmode(CMODE=1),thispinfunctionsastheslaveselectinput.

Thispinhasaweakpull-down.

27SDIILVCMOSSerialDataIn.

InI2Ccontrolmode(CMODE=0),thispinisignored.

InSPIcontrolmode(CMODE=1),thispinfunctionsastheserialdatainput.

Thispinhasaweakpull-down.

2928CKOUT–CKOUT+OMultiOutputClock.

Differentialoutputclockwithafrequencyrangeof10MHzto1.

4175GHz.

OutputsignalformatisselectedbySFOUT1_REGregis-terbits.

OutputisdifferentialforLVPECL,LVDS,andCMLcompatiblemodes.

ForCMOSformat,bothoutputpinsdriveidenticalsingle-endedclockoutputs.

36CMODEILVCMOSControlMode.

SelectsI2CorSPIcontrolmodefortheSi5319.

0=I2CControlMode1=SPIControlModeGNDPADGNDGNDSupplyGroundPad.

Thegroundpadmustprovidealowthermalandelectricalimpedancetoagroundplane.

Pin#PinNameI/OSignalLevelDescriptionNote:Internalregisternamesareindicatedbyunderlineditalics(e.

g.

,INT_PIN.

SeeSi5319RegisterMap).

Si5319Rev.

1.

0436.

OrderingGuideOrderingPartNumberOutputClockFrequencyRangePackageROHS6,Pb-FreeTemperatureRangeSi5319A-C-GM2kHz–945MHz970–1134MHz1.

213–1.

417GHz36-Lead6x6mmQFNYes–40to85°CSi5319B-C-GM2kHz–808MHz36-Lead6x6mmQFNYes–40to85°CSi5319C-C-GM2kHz–346MHz36-Lead6x6mmQFNYes–40to85°CNote:AddanRattheendofthedevicepartnumbertodenotetapeandreelorderingoptions.

Si531944Rev.

1.

07.

PackageOutline:36-PinQFNFigure6illustratesthepackagedetailsfortheSi5319.

Table10liststhevaluesforthedimensionsshownintheillustration.

Figure6.

36-PinQuadFlatNo-lead(QFN)Table10.

PackageDimensionsSymbolMillimetersSymbolMillimetersMinNomMaxMinNomMaxA0.

800.

850.

90L0.

500.

600.

70A10.

000.

020.

05——12b0.

180.

250.

30aaa——0.

10D6.

00BSCbbb——0.

10D23.

954.

104.

25ccc——0.

08e0.

50BSCddd——0.

10E6.

00BSCeee——0.

05E23.

954.

104.

25Notes:1.

Alldimensionsshownareinmillimeters(mm)unlessotherwisenoted.

2.

DimensioningandTolerancingperANSIY14.

5M-1994.

3.

ThisdrawingconformstoJEDECoutlineMO-220,variationVJJD.

4.

RecommendedcardreflowprofileispertheJEDEC/IPCJ-STD-020specificationforSmallBodyComponents.

Si5319Rev.

1.

0458.

RecommendedPCBLayoutFigure7.

PCBLandPatternDiagramFigure8.

GroundPadRecommendedLayoutSi531946Rev.

1.

0Table11.

PCBLandPatternDimensionsDimensionMINMAXe0.

50BSC.

E5.

42REF.

D5.

42REF.

E24.

004.

20D24.

004.

20GE4.

53—GD4.

53—X—0.

28Y0.

89REF.

ZE—6.

31ZD—6.

31Notes(General):1.

Alldimensionsshownareinmillimeters(mm)unlessotherwisenoted.

2.

DimensioningandTolerancingispertheANSIY14.

5M-1994specification.

3.

ThisLandPatternDesignisbasedonIPC-SM-782guidelines.

4.

AlldimensionsshownareatMaximumMaterialCondition(MMC).

LeastMaterialCondition(LMC)iscalculatedbasedonaFabricationAllowanceof0.

05mm.

Notes(SolderMaskDesign):1.

Allmetalpadsaretobenon-soldermaskdefined(NSMD).

Clearancebetweenthesoldermaskandthemetalpadistobe60μmminimum,allthewayaroundthepad.

Notes(StencilDesign):1.

Astainlesssteel,laser-cutandelectro-polishedstencilwithtrapezoidalwallsshouldbeusedtoassuregoodsolderpasterelease.

2.

Thestencilthicknessshouldbe0.

125mm(5mils).

3.

Theratioofstencilaperturetolandpadsizeshouldbe1:1fortheperimeterpads.

4.

A4x4arrayof0.

80mmsquareopeningson1.

05mmpitchshouldbeusedforthecentergroundpad.

Notes(CardAssembly):1.

ANo-Clean,Type-3solderpasteisrecommended.

2.

TherecommendedcardreflowprofileispertheJEDEC/IPCJ-STD-020specificationforSmallBodyComponents.

Si5319Rev.

1.

0479.

Si5319DeviceTopMarkMarkMethod:LaserFontSize:0.

80mmRight-JustifiedLine1Marking:Si5319CustomerPartNumberQ=SpeedCode:A,B,CSeeOrderingGuideforoptionsLine2Marking:C-GMC=ProductRevisionG=TemperatureRange–40to85°C(RoHS6)M=QFNPackageLine3Marking:YYWWRFYY=YearWW=WorkWeekR=DieRevisionF=InternalcodeAssignedbytheAssemblyHouse.

Correspondstotheyearandworkweekofthemolddate.

Line4Marking:Pin1IdentifierCircle=0.

75mmDiameterLower-LeftJustifiedXXXXInternalCodeSi531948Rev.

1.

0DOCUMENTCHANGELISTRevision0.

1toRevision0.

2Changed1.

8Voperatingrangeto±5%.

UpdatedTable1onpage4.

UpdatedTable2onpage5.

AddedtableunderFigure3onpage14.

Updated"3.

FunctionalDescription"onpage16.

Clarified"5.

PinDescriptions:Si5319"onpage40.

Revision0.

2toRevision0.

3Updated"5.

PinDescriptions:Si5319"onpage40.

CorrectedPins11and15descriptionintable.

Revision0.

3toRevision0.

4UpdatedTable1onpage4.

Added"9.

Si5319DeviceTopMark"onpage47.

Revision0.

4toRevision0.

41UpdatedTable1onpage4.

UpdatedThermalResistanceJunctiontoAmbienttypicalspecification.

UpdatedFigure4,"Si5319TypicalApplicationCircuit(I2CControlMode),"onpage15.

UpdatedFigure5,"Si5319TypicalApplicationCircuit(SPIControlMode),"onpage15.

UpdatedNCpindescriptionin"5.

PinDescriptions:Si5319"onpage40.

Updated"7.

PackageOutline:36-PinQFN"onpage44.

AddedFigure8,"GroundPadRecommendedLayout,"onpage45.

Addedregistermapdocumentation.

UpdatedRise/FallTimevalues.

Revision0.

41toRevision0.

42Changedregisteraddresslabelstodecimal.

Revision0.

42toRevision0.

43Updatedthefollowing:ESDspecificationsphasenoisevaluesabsoluteVddmaximumvoltagetypicalphasenoiseplotAddedspecificationforphasechangesduetotemperaturevariationAddedinformationfortheN32registerAddedJCspecificationRevision0.

43toRevision1.

0Replacedthespecificationtables(tables1and2fromrev.

0.

43)withthespecificationtablesfromtheSi53xReferenceManual,rev0.

42.

Si5319Rev.

1.

049NOTES:DisclaimerSiliconLaboratoriesintendstoprovidecustomerswiththelatest,accurate,andin-depthdocumentationofallperipheralsandmodulesavailableforsystemandsoftwareimplementersusingorintendingtousetheSiliconLaboratoriesproducts.

Characterizationdata,availablemodulesandperipherals,memorysizesandmemoryaddressesrefertoeachspecificdevice,and"Typical"parametersprovidedcananddovaryindifferentapplications.

Applicationexamplesdescribedhereinareforillustrativepurposesonly.

SiliconLaboratoriesreservestherighttomakechangeswithoutfurthernoticeandlimitationtoproductinformation,specifications,anddescriptionsherein,anddoesnotgivewarrantiesastotheaccuracyorcompletenessoftheincludedinformation.

SiliconLaboratoriesshallhavenoliabilityfortheconsequencesofuseoftheinformationsuppliedherein.

Thisdocumentdoesnotimplyorexpresscopyrightlicensesgrantedhereundertodesignorfabricateanyintegratedcircuits.

TheproductsmustnotbeusedwithinanyLifeSupportSystemwithoutthespecificwrittenconsentofSiliconLaboratories.

A"LifeSupportSystem"isanyproductorsystemintendedtosupportorsustainlifeand/orhealth,which,ifitfails,canbereasonablyexpectedtoresultinsignificantpersonalinjuryordeath.

SiliconLaboratoriesproductsaregenerallynotintendedformilitaryapplications.

SiliconLaboratoriesproductsshallundernocircumstancesbeusedinweaponsofmassdestructionincluding(butnotlimitedto)nuclear,biologicalorchemicalweapons,ormissilescapableofdeliveringsuchweapons.

TrademarkInformationSiliconLaboratoriesInc.

,SiliconLaboratories,SiliconLabs,SiLabsandtheSiliconLabslogo,CMEMS,EFM,EFM32,EFR,EnergyMicro,EnergyMicrologoandcombinationsthereof,"theworld'smostenergyfriendlymicrocontrollers",Ember,EZLink,EZMac,EZRadio,EZRadioPRO,DSPLL,ISOmodem,Precision32,ProSLIC,SiPHY,USBXpressandothersaretrademarksorregisteredtrademarksofSiliconLaboratoriesInc.

ARM,CORTEX,Cortex-M3andTHUMBaretrademarksorregisteredtrademarksofARMHoldings.

KeilisaregisteredtrademarkofARMLimited.

Allotherproductsorbrandnamesmentionedhereinaretrademarksoftheirrespectiveholders.

http://www.

silabs.

comSiliconLaboratoriesInc.

400WestCesarChavezAustin,TX78701USAClockBuilderProOne-clickaccesstoTimingtools,documentation,software,sourcecodelibraries&more.

AvailableforWindowsandiOS(CBGoonly).

www.

silabs.

com/CBProTimingPortfoliowww.

silabs.

com/timingSW/HWwww.

silabs.

com/CBProQualitywww.

silabs.

com/qualitySupportandCommunitycommunity.

silabs.

com

- SCLwww.ddd138.com相关文档

- 语言www.ddd138.com

- proportionwww.ddd138.com

- behandelplanwww.ddd138.com

- FGwww.ddd138.com

- constructedwww.ddd138.com

- F0E5E6D0F7F7BDE4DB2C4F074D02062www.ddd138.com

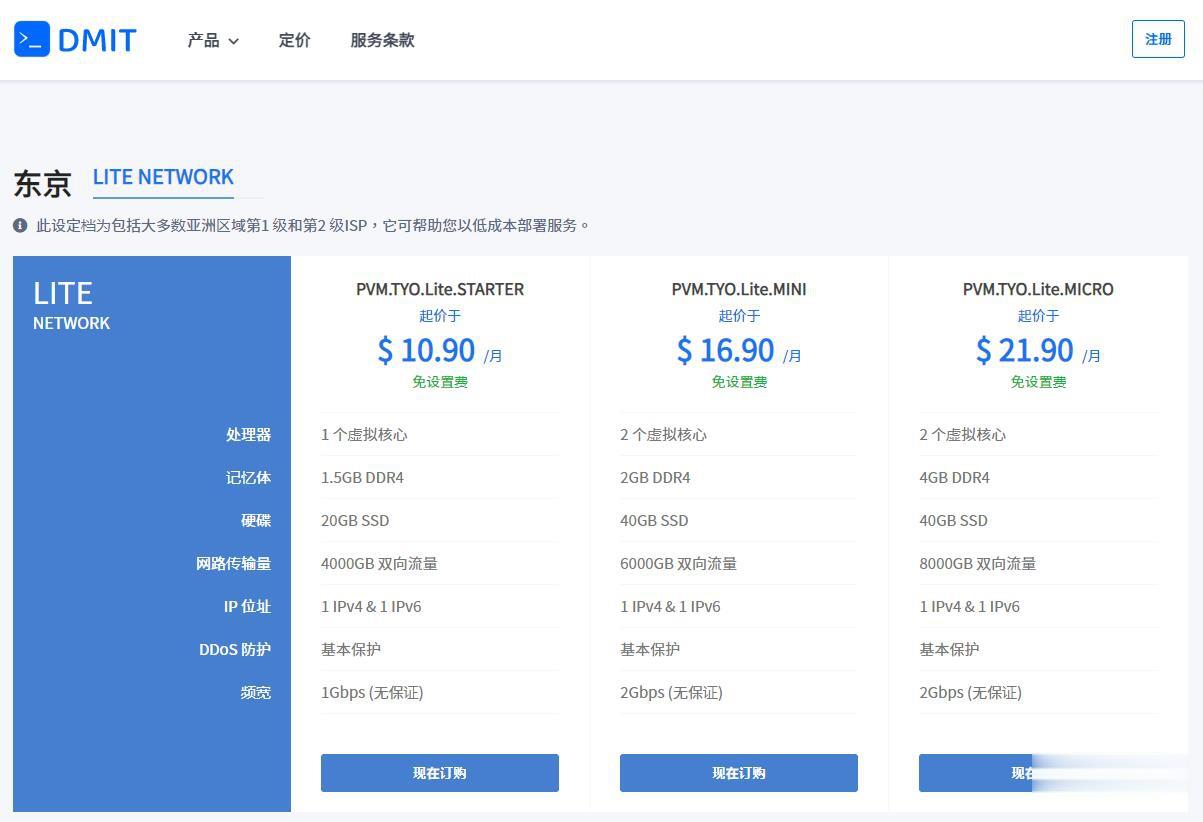

DMIT$10.9/月,日本VPS/三网直连/1核1.5G内存/20GB存储/1Gbps端口

优惠码年付一次性5折优惠码:TYO-Lite-Open-Beta-1y-50OFF永久8折优惠码:TYO-Lite-Open-Beta-Recur-20OFF日本vpsCPU内存SSD流量带宽价格购买1核1.5G20 GB4 TB1Gbps$10.9/月购买2核2 G40 GB6 TB1Gbps$16.9/月购买2核4 G60 GB8 TB1Gbps$21.9/月购买4核4 G80 GB12 TB...

CloudCone(1.99美元),可以额外选择Voxility高防IP

CloudCone 商家也是比较有特点的,和我们熟悉的DO、Vultr、Linode商家均是可以随时删除机器开通的小时计费模式。这个对于有需要短租服务器的来说是比较有性价比的。但是,他们还有一个缺点就是机房比较少,不同于上面几个小时计费服务商可以有多机房可选,如果有这个多机房方案的话,应该更有特点。这次我们可以看到CloudCone闪购活动提供洛杉矶三个促销方案,低至月付1.99美元。商家也可以随...

爱用云互联租用服务器租美国、日本、美国、日本、购买2天内不满意可以退换,IP可免费更换!

爱用云互联怎么样?爱用云是一家成立于2018年的老牌商家旗下的服务器销售品牌,是正规持证IDC/ISP/IRCS商家,主要销售国内、中国香港、国外服务器产品,线路有腾讯云国外线路、自营香港CN2线路等,都是中国大陆直连线路,非常适合免备案建站业务需求和各种负载较高的项目,同时国内服务器也有多个BGP以及高防节点。专注为个人开发者用户,中小型,大型企业用户提供一站式核心网络云端服务部署,促使用户云端...

www.ddd138.com为你推荐

便宜vps 工信部域名备案 什么是域名解析 国外私服 gomezpeer 表格样式 上海域名 空间出租 刀片服务器的优势 双线主机 新家坡 南通服务器 国外视频网站有哪些 万网主机管理 外贸空间 国内域名 石家庄服务器托管 双线空间 美国迈阿密 云销售系统 更多