efficientp2pover官网

p2pover官网 时间:2021-05-24 阅读:()

ICValidatorOverviewICValidatorisacomprehensivesignoffDRC/LVStoolarchitectedandprovenforIn-Designphysicalverificationatleading-edgeprocessnodes.

Itdeliversexcellentscalability,superiorease-of-useforthephysicaldesigner,andhighprogrammabilityforeasierrunsetdevelopment.

ICValidator'shighperformanceDRCandLVSphysicalverificationenginesubstantiallyreducesthetimetoresultsthroughnear-linearscalabilityacrossmultipleCPUcores.

Programmable,extendedelectricalrulechecking(EERC)addsreliablilityverification.

ICValidatorisseamlesslyintegratedwithICCompilerIIforIn-Designphysicalverification.

Thisaward-winningtechnologyacceleratesdesignclosureformanufacturingbyenablingindependentsignoffqualityanalysisandautomaticrepairwithintheimplementationenvironment.

ICValidatorisfullycertifiedandsiliconprovenbymajorfoundriesandIDMsforphysicalsignoff.

BenefitsTurnaroundTimePrevailingapproachestophysicaldesigncanbedescribedasimplement-then-verify,resultinginmultipletime-consumingiterationsbetweendesignandsignoff.

Thiscumbersomeflowisduetothelackofsignoff-qualityphysicalverificationduringdesignimplementation.

Atthe40nmtechnologynodeandbelow,theimplement-then-verifyflowisslowandmaycomplicateconvergenceaslayoutcorrectionscanalterkeydesignmetricssuchasarea,timingandpower.

And,at20nmandbelow,theintroductionofaclearnewchallenge,DPTcompliance,isplacinganunprecedentedburdenonphysicaldesigners.

ICValidatorPhysicalSignoffICValidatorPhysicalSignoffPlanningPlacement/CTSRoutingECOsChipnishingPre-routingchecksRoutingchecksAutomaticrepairTiming-awarellICCompilerICValidatorIn-DesignDRC,LVS,EERCDouble,tripleandquadpatterningPatternmatchingFinFETICValidatorPhysicalVerificationSolutionICValidatorisspecificallyarchitectedforIn-Designphysicalverification,bringingthepoweroffullsignoffphysicalverificationconstraintsintothedesignphasewithICCompilerIIwithoutimposingtime-consumingstream-inandstream-outoflayoutdata.

UsingIn-Designphysicalverification,DRCandmanufacturingissuesarecaughtmuchearlierinthedesigncycle,reducingoreliminatinglate-stagesurprisesclosetotapeout.

WithIn-Designverification,specificlayer,rulesandselectedareasoflayoutaretargetedincrementally,providingaspeed-upinoverall2designcompletiontime.

Designruleviolationsdiscoveredduringverification—includingDPTlimitinglayoutpatterns—canbeautomaticallyfixedwithintheglobaltimingandareacontextofthedesign,reducingtheimpactofthecorrection.

Inaddition,chipfinishingoperationstypicallyperformedduringphysicalverification,suchasmetalfill,aremanagedinasimilarfashion.

WorkingwithICCompilerII,ICValidator'sIn-Designflowdeliverssignificantlyfasterruntimesanddramaticallyreduceschipfinishingiterationsbyperformingsignoffquality,timing-drivenmetalfillandalsodouble,tripleandquadpatterningdecompositionduringthedesignphase.

HighPerformanceandScalabilityThecomplexityofthephysicalverificationtaskhasgrownsubstantiallyatthenewerprocessnodes,andisgettingworseat20nmandbelow.

Toaddressthecapacityandperformancerequirementsofphysicalverificationatadvancednodes,ICValidatorisarchitectedforexcellentscalabilityandefficientutilizationofavailablehardware.

Multi-threading:ICValidator'smultithreadingapproachsignificantlyshortensexecutiontimeonmodernmulticoreCPUs.

Scalability:ICValidatorprovidesnearlinearscalabilityacrossadistributedcomputingnetwork,supportinga40Xruntimeaccelerationona64-CPUnetworkandenablingcompletionofmostphysicalverificationtasksovernight.

(SeeFigure1).

On-DemandLoadBalancing:Intelligentjobschedulingkeepsallcoresequallybusytominimizethetotaljobcompletiontime.

Memory-AwareScheduling:ICValidator'sschedulerdistributesjobstoavoidexceedinganyindividualcomputer'smemorycapacity.

Thisavoidsdelayscausedbypagingwhenmemoryisexceeded.

051015202530354045PerformancescalabilitySinglecore2cores4cores8cores16cores32cores64coresFigure1.

ICValidatorscalabilityextendsto64coresandbeyondEnhancedProductivityWithInDesignPhysicalVerificationAutomaticDRCRepair(ADR)ICValidator'sseamlessintegrationwithICCompilerIIenablesaninnovativelayoutauto-correctioninterface,whichidentifiesDRCviolations,includingDPTdecompositionviolationsandinitiatesautomaticrepairs.

ThecorrectionsareappliedbyICCompilerIItoalleviateDRCandDPTerrors,andthenvalidatedwithinICValidator.

InDesignintegrationmakesitpossibletomaintainhotspot-freedesignsthroughoutimplementation,furthereliminatingiterationswithdownstreamanalysistools.

ADR'stightfind-andrepairloopenablesrapiddiscoveryandrepairoferrors,minimizingdesignerinterventionandspeedingtimetotapeout.

(SeeFigure2).

3Figure2.

ICCompilerIIGUIshowingICValidator-enabledsignoffDRCcommandIncrementalLayer-based,Rule-basedandArea-basedVerificationToacceleratephysicalverificationdesigntime,ICValidatorandICCompilerIIintegrationenablesintelligentincrementalflowstoeliminateunnecessarycheckingbyrestrictingverificationtothespecificlayer,ruleordesignareathatneedsvalidation.

Thetightintegrationprovidesapowerfultooldialogthatallowstheusertoquicklyselecttherules,layersandregionsizeforDRCchecking,patternmatching,oraddingmetalfill.

Byautomaticallylimitingthescopeofthevalidation,moreverificationrunscanbeperformedearlyinthedesigncycle,greatlyreducingthenumberoffulldesignverificationruns,andshorteningthetimetoresults.

(SeeFigure3).

Figure3.

Area-basedincrementalsignoffDRCanalysis.

Onlytheareahighlightedissubmittedforanalysis.

IncrementalverificationisespeciallyimportantforECOvalidation,whichtypicallyimpactsaverysmallsectionofthedesign.

Usingaconventionalflow,criticalverificationtimecanbewastedoncheckingthefullchipevenwhenchangesweremadetoselectedregionsorlayers.

TheIn-DesignflowsavestimebyrestrictingtheverificationtoonlythelayersandareaaffectedbytheECO.

Asaresult,theIn-Designflowsignificantlyspeedsverification.

4Timing-AwareFillAtadvancednodes,fillinsertionismandatorytoensuremanufacturabilityandhighyield.

Butexcessivefillcanleadtobuildupofcouplingcapacitance,impactingtimingandresultinginunpredictableiterationswithdesign.

In-DesigntechnologywithICValidatorenablessingle-passfillimplementationthatistimingawaretopreventsuchproblems.

CombinedwithICValidator'snovelfill-to-targettechnology,timing-awarefillefficientlybalancestiminganddensityandreplacesmultiplefill-analyzeiterationswithasinglestep.

Atthesub-20nmnodestiming-awarenesscoupledwithtrack-basedfillenableshigherfilldensitiesalongwithgreatercontroloverfilldensityvstimingimpact.

ErrorVisualizationTomaintainefficientphysicalverification,rapidvisualizationanderrorcorrectionareasimportantasfastphysicalverificationruntime.

ICValidatorincludestheICValidatorVUEvisualizationtool,whichprovidesaneasy-to-use,intelligenterrornavigationandprioritizationsystemforefficientreviewandcorrectionofDRCandLVSissues,double,tripleandquadpatterningconflicts,andmanufacturing-limitingpatterns.

UsingICValidatorVUE,layoutengineerscanquicklyandeasilyscanphysicalverificationerrorsintheICCompilerIIenvironment,aswellasotherwidelyusedlayouteditors.

ICValidatorVUEenhancesproductivityforphysicalverificationengineers.

PatternMatchingICValidator'sPatternMatchingefficientlyexpandsICValidator'srule-basedsignoffengineforpattern-drivenverification.

Thiscapabilitymakesitpossibletoquicklyidentifyandautomaticallycorrectmanufacturabilityhotspotsinadesignbycomparingagainstalibraryofknownproblematiclayoutpatterns.

ICValidator'spatentedpatternmatchingtechnologyeliminatestheneedforconvolutedrulesand,withalmostzeroruntimepenaltyperpattern,itsignificantlyspeedsupthetimetoachievemanufacturingcompliance.

SignoffDRCandLVSReadyAt20nmandBelowFoundryQualificationComprehensivefoundryqualificationisanecessarycomponentofanysuccessfulphysicalverificationsolution.

ICValidatorisqualifiedandactivelyinuseforFinFETs,SOIandtraditionaltechnologiesatestablishedprocessnodesandadvancedemergingprocessnodesbyleadingfoundries.

Layout-vs-Schematic(LVS)ICValidatorLVSisfoundrycertifiedandprovidesacomprehensiveverificationanddebuggingenvironment.

ThemostimportantaspectofanyLVSsolutionisthepowerandefficiencyofitsdebugenvironment.

ICValidatorexcelswithitsVUEandShortfindertoolsthatquicklyandeasilyidentifyerrors,suchastext-levelshorts,forrapidrepairandrevalidation.

VUEisagraphicalenvironmenttodisplayandcross-probebetweenlayoutandschematics,togetherwithasophisticatederrormanagementsystem.

ICValidatorLVSdeviceextractionsupportsleadingedgetechnologieswheredeviceparametersareoftenaffectedbytheirproximitytoneighboringdevicesthroughlayoutdependenteffects(LDE).

Fill-to-TargetTechnologyICValidator'sFill-to-Targettechnologyisatile-basedparametricfillenginethatinsertstherightshapesintherightplacestogivesuperiorplanarityandsmoothfilldensity,evenaroundmacros.

Thiscorrect-by-constructionapproachimprovesyieldandspeedsturnaroundtimebyreplacingthetraditionaliterativefill-analyzeflowwithasingle-pass.

Double,Triple,QuadPatterningManufacturingat20nmandbelowusuallyreliesonDPT,whichrequiresthatadesignbedecomposableintotwooverlappinglayoutpatterns.

ICValidatorofferscomprehensivesupportfordoublepatterningdevelopedinclosecooperationwithleadingfoundriesandIDMs.

ICValidatorincludesanativecoloring(decomposition)enginebasedonflexiblecodingofDPTrules,andsupportsadvancedcapabilitiessuchasstitchingrules.

WithIn-Designtechnology,ICValidatorprovidesnotonlysignoffqualitydecompositionchecking,butalsoautomaticrepairofDPTconflicts.

(SeeFigure4).

06/27/16.

CE_CS7331_ICValidatorDS.

Synopsys,Inc.

690EastMiddlefieldRoadMountainView,CA94043www.

synopsys.

com2016Synopsys,Inc.

Allrightsreserved.

SynopsysisatrademarkofSynopsys,Inc.

intheUnitedStatesandothercountries.

AlistofSynopsystrademarksisavailableathttp://www.

synopsys.

com/copyright.

html.

Allothernamesmentionedhereinaretrademarksorregisteredtrademarksoftheirrespectiveowners.

Figure4.

Signoffqualitydouble,tripleandquadpatterningverificationandcorrectionforadvancednodesEquation-basedandProperty-basedCheckingNewfoundryrules,likevoltage-domainchecks,oftenrelyonspecificpropertiesthatareattachedtogeometricshapes.

ICValidatorprovidesaflexibleandefficientproperty-basedcheckingmechanismtoenrichphysicalverificationbeyondstrictlycheckinggeometries.

Othercomplexfoundryrulescanrequirelocalizedandselectivepolygoninclusioncriteria,orrequirecontinuousfunctionstodescribeaccurately.

ICValidatoroffersrichprogrammabilityfeaturesthatcanaccuratelycomputeequationbasedgeometriccharacteristics.

Forexample,traditionalbinningcanbetoocrudeforcriticalareacalculation,andacontinuousequation-basedevaluationismoreaccurate.

FlexibleErrorReportingandClassificationICValidatorsupportsaDRCdispositionandreportingutilitythatcanimplementcustomDRCwaiversandrapidcategorizationofDRCviolations.

DRCerrorscanalsobereviewedastheDRCjobcontinuestorun.

Thisapproachspeedstimetotapeoutbyenablingparalleldebugandexecution.

IntegrationwithStarRCICValidatorLVShasanefficientworkingflowwithSynopsysStarRCforparasiticextraction.

ICValidatorsupportsend-to-endhierarchicalparasiticextractionthatminimizesphysicalflatteningandsimplifiesextractionbyimplementingasinglepassflow,providingamajorperformanceincreaseoverthedoubleextractionflowofpreviousgenerationtools.

IntegrationwithGalaxyCustomCompilerICValidatorworkstogetherwithSynopsys'full-customsolution,CustomCompiler,tosupportatightlyintegratedDRCandLVS-enabledcustomdesignflow.

BothICValidatorandCustomCompilerfullysupporttheOpenAccessdatabase.

Inaddition,CustomCompilerisintegratedwiththeVUEerrornavigatorforrapiddebugofDRCandLVSissues.

ReliabilityVerificationInadditiontobeingacomprehensivephysicalverificationplatform,ICValidatorisalsoareliabilityverificationplatform.

Programmable,extendedelectricalrulechecking(EERC)enablescustomizedcheckingforEOS/ESD/ERCrules.

ICValidatorprogrammableEERCisareliabilitysolutionthatunderstandscheckingforissuesthatrequireonlyanetlist(netlistdomainchecksorNDC),thosethatrequireacombinationofboththenetlistandlayoutshapes(mixedmodechecksorMMC),andchecksforcurrentdensityandpoint-to-pointresistance(CDC/P2P).

ICValidatorprogrammableEERCleveragesthepowerandwide-spreadfamiliarityofthePythonscriptinglanguageforrobustandeasyrulecreation.

ProgrammableEERCelevateselectricalrulecheckingfromtime-consuminganderror-pronemanualmethodstohigh-speedautomatedreliabilityverification.

Itdeliversexcellentscalability,superiorease-of-useforthephysicaldesigner,andhighprogrammabilityforeasierrunsetdevelopment.

ICValidator'shighperformanceDRCandLVSphysicalverificationenginesubstantiallyreducesthetimetoresultsthroughnear-linearscalabilityacrossmultipleCPUcores.

Programmable,extendedelectricalrulechecking(EERC)addsreliablilityverification.

ICValidatorisseamlesslyintegratedwithICCompilerIIforIn-Designphysicalverification.

Thisaward-winningtechnologyacceleratesdesignclosureformanufacturingbyenablingindependentsignoffqualityanalysisandautomaticrepairwithintheimplementationenvironment.

ICValidatorisfullycertifiedandsiliconprovenbymajorfoundriesandIDMsforphysicalsignoff.

BenefitsTurnaroundTimePrevailingapproachestophysicaldesigncanbedescribedasimplement-then-verify,resultinginmultipletime-consumingiterationsbetweendesignandsignoff.

Thiscumbersomeflowisduetothelackofsignoff-qualityphysicalverificationduringdesignimplementation.

Atthe40nmtechnologynodeandbelow,theimplement-then-verifyflowisslowandmaycomplicateconvergenceaslayoutcorrectionscanalterkeydesignmetricssuchasarea,timingandpower.

And,at20nmandbelow,theintroductionofaclearnewchallenge,DPTcompliance,isplacinganunprecedentedburdenonphysicaldesigners.

ICValidatorPhysicalSignoffICValidatorPhysicalSignoffPlanningPlacement/CTSRoutingECOsChipnishingPre-routingchecksRoutingchecksAutomaticrepairTiming-awarellICCompilerICValidatorIn-DesignDRC,LVS,EERCDouble,tripleandquadpatterningPatternmatchingFinFETICValidatorPhysicalVerificationSolutionICValidatorisspecificallyarchitectedforIn-Designphysicalverification,bringingthepoweroffullsignoffphysicalverificationconstraintsintothedesignphasewithICCompilerIIwithoutimposingtime-consumingstream-inandstream-outoflayoutdata.

UsingIn-Designphysicalverification,DRCandmanufacturingissuesarecaughtmuchearlierinthedesigncycle,reducingoreliminatinglate-stagesurprisesclosetotapeout.

WithIn-Designverification,specificlayer,rulesandselectedareasoflayoutaretargetedincrementally,providingaspeed-upinoverall2designcompletiontime.

Designruleviolationsdiscoveredduringverification—includingDPTlimitinglayoutpatterns—canbeautomaticallyfixedwithintheglobaltimingandareacontextofthedesign,reducingtheimpactofthecorrection.

Inaddition,chipfinishingoperationstypicallyperformedduringphysicalverification,suchasmetalfill,aremanagedinasimilarfashion.

WorkingwithICCompilerII,ICValidator'sIn-Designflowdeliverssignificantlyfasterruntimesanddramaticallyreduceschipfinishingiterationsbyperformingsignoffquality,timing-drivenmetalfillandalsodouble,tripleandquadpatterningdecompositionduringthedesignphase.

HighPerformanceandScalabilityThecomplexityofthephysicalverificationtaskhasgrownsubstantiallyatthenewerprocessnodes,andisgettingworseat20nmandbelow.

Toaddressthecapacityandperformancerequirementsofphysicalverificationatadvancednodes,ICValidatorisarchitectedforexcellentscalabilityandefficientutilizationofavailablehardware.

Multi-threading:ICValidator'smultithreadingapproachsignificantlyshortensexecutiontimeonmodernmulticoreCPUs.

Scalability:ICValidatorprovidesnearlinearscalabilityacrossadistributedcomputingnetwork,supportinga40Xruntimeaccelerationona64-CPUnetworkandenablingcompletionofmostphysicalverificationtasksovernight.

(SeeFigure1).

On-DemandLoadBalancing:Intelligentjobschedulingkeepsallcoresequallybusytominimizethetotaljobcompletiontime.

Memory-AwareScheduling:ICValidator'sschedulerdistributesjobstoavoidexceedinganyindividualcomputer'smemorycapacity.

Thisavoidsdelayscausedbypagingwhenmemoryisexceeded.

051015202530354045PerformancescalabilitySinglecore2cores4cores8cores16cores32cores64coresFigure1.

ICValidatorscalabilityextendsto64coresandbeyondEnhancedProductivityWithInDesignPhysicalVerificationAutomaticDRCRepair(ADR)ICValidator'sseamlessintegrationwithICCompilerIIenablesaninnovativelayoutauto-correctioninterface,whichidentifiesDRCviolations,includingDPTdecompositionviolationsandinitiatesautomaticrepairs.

ThecorrectionsareappliedbyICCompilerIItoalleviateDRCandDPTerrors,andthenvalidatedwithinICValidator.

InDesignintegrationmakesitpossibletomaintainhotspot-freedesignsthroughoutimplementation,furthereliminatingiterationswithdownstreamanalysistools.

ADR'stightfind-andrepairloopenablesrapiddiscoveryandrepairoferrors,minimizingdesignerinterventionandspeedingtimetotapeout.

(SeeFigure2).

3Figure2.

ICCompilerIIGUIshowingICValidator-enabledsignoffDRCcommandIncrementalLayer-based,Rule-basedandArea-basedVerificationToacceleratephysicalverificationdesigntime,ICValidatorandICCompilerIIintegrationenablesintelligentincrementalflowstoeliminateunnecessarycheckingbyrestrictingverificationtothespecificlayer,ruleordesignareathatneedsvalidation.

Thetightintegrationprovidesapowerfultooldialogthatallowstheusertoquicklyselecttherules,layersandregionsizeforDRCchecking,patternmatching,oraddingmetalfill.

Byautomaticallylimitingthescopeofthevalidation,moreverificationrunscanbeperformedearlyinthedesigncycle,greatlyreducingthenumberoffulldesignverificationruns,andshorteningthetimetoresults.

(SeeFigure3).

Figure3.

Area-basedincrementalsignoffDRCanalysis.

Onlytheareahighlightedissubmittedforanalysis.

IncrementalverificationisespeciallyimportantforECOvalidation,whichtypicallyimpactsaverysmallsectionofthedesign.

Usingaconventionalflow,criticalverificationtimecanbewastedoncheckingthefullchipevenwhenchangesweremadetoselectedregionsorlayers.

TheIn-DesignflowsavestimebyrestrictingtheverificationtoonlythelayersandareaaffectedbytheECO.

Asaresult,theIn-Designflowsignificantlyspeedsverification.

4Timing-AwareFillAtadvancednodes,fillinsertionismandatorytoensuremanufacturabilityandhighyield.

Butexcessivefillcanleadtobuildupofcouplingcapacitance,impactingtimingandresultinginunpredictableiterationswithdesign.

In-DesigntechnologywithICValidatorenablessingle-passfillimplementationthatistimingawaretopreventsuchproblems.

CombinedwithICValidator'snovelfill-to-targettechnology,timing-awarefillefficientlybalancestiminganddensityandreplacesmultiplefill-analyzeiterationswithasinglestep.

Atthesub-20nmnodestiming-awarenesscoupledwithtrack-basedfillenableshigherfilldensitiesalongwithgreatercontroloverfilldensityvstimingimpact.

ErrorVisualizationTomaintainefficientphysicalverification,rapidvisualizationanderrorcorrectionareasimportantasfastphysicalverificationruntime.

ICValidatorincludestheICValidatorVUEvisualizationtool,whichprovidesaneasy-to-use,intelligenterrornavigationandprioritizationsystemforefficientreviewandcorrectionofDRCandLVSissues,double,tripleandquadpatterningconflicts,andmanufacturing-limitingpatterns.

UsingICValidatorVUE,layoutengineerscanquicklyandeasilyscanphysicalverificationerrorsintheICCompilerIIenvironment,aswellasotherwidelyusedlayouteditors.

ICValidatorVUEenhancesproductivityforphysicalverificationengineers.

PatternMatchingICValidator'sPatternMatchingefficientlyexpandsICValidator'srule-basedsignoffengineforpattern-drivenverification.

Thiscapabilitymakesitpossibletoquicklyidentifyandautomaticallycorrectmanufacturabilityhotspotsinadesignbycomparingagainstalibraryofknownproblematiclayoutpatterns.

ICValidator'spatentedpatternmatchingtechnologyeliminatestheneedforconvolutedrulesand,withalmostzeroruntimepenaltyperpattern,itsignificantlyspeedsupthetimetoachievemanufacturingcompliance.

SignoffDRCandLVSReadyAt20nmandBelowFoundryQualificationComprehensivefoundryqualificationisanecessarycomponentofanysuccessfulphysicalverificationsolution.

ICValidatorisqualifiedandactivelyinuseforFinFETs,SOIandtraditionaltechnologiesatestablishedprocessnodesandadvancedemergingprocessnodesbyleadingfoundries.

Layout-vs-Schematic(LVS)ICValidatorLVSisfoundrycertifiedandprovidesacomprehensiveverificationanddebuggingenvironment.

ThemostimportantaspectofanyLVSsolutionisthepowerandefficiencyofitsdebugenvironment.

ICValidatorexcelswithitsVUEandShortfindertoolsthatquicklyandeasilyidentifyerrors,suchastext-levelshorts,forrapidrepairandrevalidation.

VUEisagraphicalenvironmenttodisplayandcross-probebetweenlayoutandschematics,togetherwithasophisticatederrormanagementsystem.

ICValidatorLVSdeviceextractionsupportsleadingedgetechnologieswheredeviceparametersareoftenaffectedbytheirproximitytoneighboringdevicesthroughlayoutdependenteffects(LDE).

Fill-to-TargetTechnologyICValidator'sFill-to-Targettechnologyisatile-basedparametricfillenginethatinsertstherightshapesintherightplacestogivesuperiorplanarityandsmoothfilldensity,evenaroundmacros.

Thiscorrect-by-constructionapproachimprovesyieldandspeedsturnaroundtimebyreplacingthetraditionaliterativefill-analyzeflowwithasingle-pass.

Double,Triple,QuadPatterningManufacturingat20nmandbelowusuallyreliesonDPT,whichrequiresthatadesignbedecomposableintotwooverlappinglayoutpatterns.

ICValidatorofferscomprehensivesupportfordoublepatterningdevelopedinclosecooperationwithleadingfoundriesandIDMs.

ICValidatorincludesanativecoloring(decomposition)enginebasedonflexiblecodingofDPTrules,andsupportsadvancedcapabilitiessuchasstitchingrules.

WithIn-Designtechnology,ICValidatorprovidesnotonlysignoffqualitydecompositionchecking,butalsoautomaticrepairofDPTconflicts.

(SeeFigure4).

06/27/16.

CE_CS7331_ICValidatorDS.

Synopsys,Inc.

690EastMiddlefieldRoadMountainView,CA94043www.

synopsys.

com2016Synopsys,Inc.

Allrightsreserved.

SynopsysisatrademarkofSynopsys,Inc.

intheUnitedStatesandothercountries.

AlistofSynopsystrademarksisavailableathttp://www.

synopsys.

com/copyright.

html.

Allothernamesmentionedhereinaretrademarksorregisteredtrademarksoftheirrespectiveowners.

Figure4.

Signoffqualitydouble,tripleandquadpatterningverificationandcorrectionforadvancednodesEquation-basedandProperty-basedCheckingNewfoundryrules,likevoltage-domainchecks,oftenrelyonspecificpropertiesthatareattachedtogeometricshapes.

ICValidatorprovidesaflexibleandefficientproperty-basedcheckingmechanismtoenrichphysicalverificationbeyondstrictlycheckinggeometries.

Othercomplexfoundryrulescanrequirelocalizedandselectivepolygoninclusioncriteria,orrequirecontinuousfunctionstodescribeaccurately.

ICValidatoroffersrichprogrammabilityfeaturesthatcanaccuratelycomputeequationbasedgeometriccharacteristics.

Forexample,traditionalbinningcanbetoocrudeforcriticalareacalculation,andacontinuousequation-basedevaluationismoreaccurate.

FlexibleErrorReportingandClassificationICValidatorsupportsaDRCdispositionandreportingutilitythatcanimplementcustomDRCwaiversandrapidcategorizationofDRCviolations.

DRCerrorscanalsobereviewedastheDRCjobcontinuestorun.

Thisapproachspeedstimetotapeoutbyenablingparalleldebugandexecution.

IntegrationwithStarRCICValidatorLVShasanefficientworkingflowwithSynopsysStarRCforparasiticextraction.

ICValidatorsupportsend-to-endhierarchicalparasiticextractionthatminimizesphysicalflatteningandsimplifiesextractionbyimplementingasinglepassflow,providingamajorperformanceincreaseoverthedoubleextractionflowofpreviousgenerationtools.

IntegrationwithGalaxyCustomCompilerICValidatorworkstogetherwithSynopsys'full-customsolution,CustomCompiler,tosupportatightlyintegratedDRCandLVS-enabledcustomdesignflow.

BothICValidatorandCustomCompilerfullysupporttheOpenAccessdatabase.

Inaddition,CustomCompilerisintegratedwiththeVUEerrornavigatorforrapiddebugofDRCandLVSissues.

ReliabilityVerificationInadditiontobeingacomprehensivephysicalverificationplatform,ICValidatorisalsoareliabilityverificationplatform.

Programmable,extendedelectricalrulechecking(EERC)enablescustomizedcheckingforEOS/ESD/ERCrules.

ICValidatorprogrammableEERCisareliabilitysolutionthatunderstandscheckingforissuesthatrequireonlyanetlist(netlistdomainchecksorNDC),thosethatrequireacombinationofboththenetlistandlayoutshapes(mixedmodechecksorMMC),andchecksforcurrentdensityandpoint-to-pointresistance(CDC/P2P).

ICValidatorprogrammableEERCleveragesthepowerandwide-spreadfamiliarityofthePythonscriptinglanguageforrobustandeasyrulecreation.

ProgrammableEERCelevateselectricalrulecheckingfromtime-consuminganderror-pronemanualmethodstohigh-speedautomatedreliabilityverification.

- efficientp2pover官网相关文档

- Additionalp2pover官网

- protocolsp2pover官网

- 2.2879999999999998p2pover官网

- servicep2pover官网

- oldsp2pover官网

- chargingp2pover官网

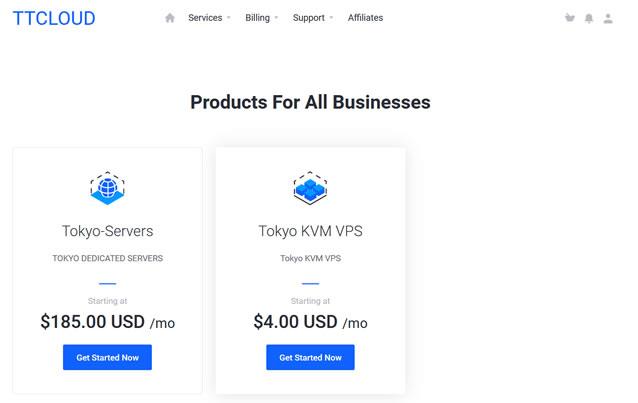

TTcloud(月$70)E3-1270V3 8GB内存 10Mbps带宽 ,日本独立服务器

关于TTCLOUD服务商在今年初的时候有介绍过一次,而且对于他们家的美国圣何塞服务器有过简单的测评,这个服务商主要是提供独立服务器业务的。目前托管硬件已经达到5000台服务器或节点,主要经营圣何塞,洛杉矶以及日本东京三个地区的数据中心业务。这次看到商家有推出了新上架的日本独立服务器促销活动,价格 $70/月起,季付送10Mbps带宽。也可以跟进客户的需求进行各种DIY定制。内存CPU硬盘流量带宽价...

易探云美国云服务器评测,主机低至33元/月,336元/年

美国服务器哪家平台好?美国服务器无需备案,即开即用,上线快。美国服务器多数带防御,且有时候项目运营的时候,防御能力是用户考虑的重点,特别是网站容易受到攻击的行业。现在有那么多美国一年服务器,哪家的美国云服务器好呢?美国服务器用哪家好?这里推荐易探云,有美国BGP、美国CN2、美国高防、美国GIA等云服务器,线路优化的不错。易探云刚好就是做香港及美国云服务器的主要商家之一,我们来看一下易探云美国云服...

NameCheap新注册.COM域名$5.98

随着自媒体和短视频的发展,确实对于传统的PC独立网站影响比较大的。我们可以看到云服务器商家的各种促销折扣活动,我们也看到传统域名商的轮番新注册和转入的促销,到现在这个状态已经不能说这些商家的为用户考虑,而是在不断的抢夺同行的客户。我们看到Namecheap商家新注册域名和转入活动一个接一个。如果我们有需要新注册.COM域名的,只需要5.98美元。优惠码:NEWCOM598。同时有赠送2个月免费域名...

p2pover官网为你推荐

-

人文社科winrar幼儿搜狗拼音输入法4漏洞chrome之路android支持ipad支持ipad支持ipad支持ipadwindows键是哪个windows 快捷键 大全windows键是哪个Windows键是哪个键啊?