指针计数器代码

计数器代码 时间:2021-04-12 阅读:()

异步FIFO的设计CNDLAB程磊I.

综述在多时钟域系统的设计中,跨时钟域的设计在所难免,尤其是在设计模块和外围芯片通信中出现.

当数据从一个时钟域向另一个异步时钟域传递的过程中,由于不同速率器件间的速率匹配问题,一般不能够通过直接传递保证数据传输的正确、完整性,故需要有一个中间数据缓冲来保证数据能够准确无误的传递.

FIFO(FirstInFirstOut)是一种队列,数据从一端进队列,另一端出队列,先进入队列的数据先被读取出,这种机制可以保证数据的时序上的正确性.

除此之外对FIFO的应用不仅仅是跨时钟域接口设计,在同步系统中可以起到防止时钟抖动等因素造成的数据传输错误提高系统稳定性能.

FIFO有同步和异步之分,同步的FIFO的读写时钟为同一时钟信号,而异步FIFO的读写时钟相互独立互不影响.

由于缓冲区是RAM,需要引入读写指针.

写指针总是指向下一个将要被写入的地址,在Reset后归零地址;读指针总是指向当前待读出的指针,在Reset后归零.

0F1U2D3A4N5U6N7I8V9101112131415wptrrptr0F1U2D3A4N5U6N7I8V9E101112131415wptrrptrDataEDataNDataRDataN0F1U2D3A4N5U6N7I8V9E101112131415wptrrptrDataRDataUOriginalStateWriteaByteReadaByteFig.

1读写指针工作原理在进行设计时同步和异步FIFO的最大区别就在于读写指针是否为同步或异步.

同步FIFO中wptr与rptr在同一时钟上升沿变化,而对于异步而言,读指针仅仅在读时钟上升沿变化,写指针仅仅在写时钟上升沿变化.

FIFO的缓冲区空间是有限的,在设计中需要考虑缓冲区的溢出和空的情况.

在缓冲区满时,产生FULL信号,以阻塞数据继续向FIFO写入.

而在缓冲区空时,产生EMPTY信号,以阻塞数据继续从FIFO中读出.

外部的读写控制器将从标志信号FULL、EMPTY决定继续写入或读出.

这种判断是基于对读指针和写指针指向的地址来判断的.

判断标志信号是FIFO的设计重点之一.

在同步的FIFO中读指针和写指针是同步的,所以在时钟的上升沿时比较判断FULL或EMPTY时,读指针和写指针指向的地址都是实际指针所指向的;而异步FIFO的读写指针是不同步的,这样就会造成在进行判断比较时,无论采用读时钟还是写时钟上升沿去判断FULL或EMPTY都将不合适.

所以在异步FIFO中需要一种机制使得能够将读写指针准确传递,一种解决方法是采用握手协议来保证在采样过程中指针不变,但是这样的做法效率很低.

另一种是通过读时钟来采样写指针,写时钟来采样读指针,然后通过采样的写指针和读指针判断是否为EMPTY,采样的读指针和写指针判断是否为FULL.

EMPTY信号对于读时钟而言是同步的,FULL信号对于写时钟是同步的.

Fig.

2一种同步FIFO的读写时序Fig.

3一种异步FIFO的读写时序II.

深入考虑在前面提到如果打算用写时钟取样读指针或用读时钟来取样写指针,将不可避免的遇到一个亚稳态的问题,它将会导致空、满标志的判断错误,并导致设计的失败.

下面分析亚稳态的产生原因和消除方法.

对于采样电路中,一个信号在过渡到另一个时钟域时,如果仅仅用一个触发器将其锁存,那么采样的结果将可能是亚稳态.

这也就是信号在跨时钟域时应该注意的问题.

如Fig.

4中时钟a,b是异步的,第二个触发器通过时钟b采样由寄存器锁存的数据data_a.

显然这种做法是冒险的,我们可以知道触发器工作过程中存在数据的建立(setup)和保持(hold)时间.

对于使用上升沿触发的触发器来说,建立时间就是在时钟上升沿到来之前,触发器数据端数据保持稳定的最小时间.

而保持时间是时钟上升沿到来之后,触发器数据端数据还应该继续保持稳定的最小时间.

我们把这段时间成为setup-hold时间.

在这个时间参数内,输入信号在时钟的上升沿是不允许发生变化的.

如果输入信号在这段时间内发生了变化,输出结果将是不可知的,即亚稳态(Metastability).

信号data经过一个锁存器的输出数据为data_a.

用时钟b_clk进行采样的时候,如果data_a正好在b_clk的setup-hold时间内发生变化,此时data_b就既不是逻辑"1",也不是逻辑"0",而是处于中间状态.

经过一段时间之后,有可能回升到高电平,也有可能降低到低电平.

输出信号处于中间状态到恢复为逻辑"1"或逻辑"0"的这段时间,我们称之为亚稳态时间.

Fig.

4采样电路Fig.

5D触发器的设定保持特性Fig.

6由采样电路产生的亚稳态时序为了考量亚稳态发生的几率可以用参数MTBF(MeanTimeBetweenFailures,平均无故障时间间隔)来描述,MTBF即触发器采样失败的时间间隔,表示为:dataclkresffTtMTBF**=0)/exp(τEq.

1上式rest中为分辨时间,τ和0T为触发器器件特性触发器特性相关参数,clkf是采样时钟频率,dataf是异步信号的触发频率.

如果MTBF很大,就认为这个设计在实际工作中是能够正常运行的,不会因为亚稳态导致整个系统的失效.

当触发器处于亚稳态,且处于亚稳态的时间超过了一个时钟周期,这种不确定的状态还会影响到下一级的触发器,最终导致连锁反应,从而使整个系统功能失常.

为了避免进入亚稳态,应当使参数MTBF尽可能大.

通常采用的方法是双锁存器法,即在一个信号进入另一个时钟域Fig.

7双锁存器法之前,将该信号用两个锁存器连续锁存两次(如图Fig.

7所示),由前给出的MTBF公式可以得到两级触发器的MTBF公式:)/1exp()/exp(02ττpdclkdataclkrestfffTtMTBF***=Eq.

2一般而言τ>>rest所以exp的增长比分母的平方增长快,所以在其他参数不变的条件下Eq.

2比Eq.

1来得大,data_c进入亚稳态的几率就更加减小.

依次类推,多增加锁存器的级数可以进一步降低出现亚稳态的几率,但是作为平衡考虑一般采用2级MTBF就已经足够大了.

Fig.

8双锁存器采样异步信号时序引入两级锁存器的同时带来了对输入信号的一级延时,再如a_clk的频率比b_clk的频率高,将可能出现因为dat变化太快,而使b_clk无法采样的问题.

即在信号从快时钟域向慢时钟域过渡的时候,如果信号变化太快,慢时钟将可能无法对该信号进行正确的采样,所以在使用双锁存器法的时候,应该使原始信号保持足够长的时间,以便另一个时钟域的锁存器可以正确地对其进行采样.

但是在这里的FIFO设计中并不需要过于关心这个两问题,原因将在后面分析.

采用双锁存器可以大大降低亚了稳态的出现几率,但是完全消除亚稳态是不可能的,一旦发生亚稳态那么读写指针所读取的数据就会发生错误.

读写指针在每次写入或读取之后会Fig.

7双锁存器法加一以使指针指向下一个地址,一般我们会采用Binarycode.

但是采用Binarycode是相邻的两个数之间可能有若干位bit改变(7->8==0111->1000四位全部改变),这样增加了产生亚稳态的几率.

一种很好的解决方法是采用Graycode来对地址进行编码.

Graycode是一种最小距离编码方式,既相邻的两数时间仅有1bit的差别,那么在FIFO应用中每次仅有一位改变,OrderBinaryCodeGrayCodeConvertRules000000000G->B100010001nnGB=1+=iiiBGBni≠Eq.

3200100011300110010401000110501010111601100101701110100810001100B->G910011101nnBG=1+=iiiBBGni≠E.

q4101010111111101111101211001010131101101114111010011511111000Table.

1BinaryGrayCode对照以及转换方法读写指针采用了Graycode那么地址译码将使用Graycode,判断空、满就和采用Binarycode就不一样了,接着我们详细分析.

为了最大限度利用RAM资源,FIFO一定是环形队列.

对于环形队列判断其是否空还是满的准则是:当读指针赶上写指针时,队列为空;当写指针赶上读指针时,队列为满.

显然只要是读写的指针的地址n位全都相同就会有空或满的状态,显然这样并不能区分空或满的状态.

则当对2n个地址进行编码时,如果我们再增加一位,即利用n+1位对2n个地址进行编码时,MSB可以表示是读指针赶上写指针还是写指针赶上读指针.

如果是Binarycode的方式,以n=3为例(如Fig.

9)给23个地址编码,多加一位,则一共有23+1个编码,从0000到0111,从1000到1111.

我们可以看到尽管MSB有变化,但是其余的位是相同的在地址译码的过程中,存在周期性只需要取后三位就是地址了.

对于判断空、满则在rptr(MSB-1:0)=wptr(MSB-1:0)条件下rptr(MSB)=wptr(MSB)则代表为队列为空,rptr(MSB)≠wptr(MSB)代表为队列为满;0000011101010100001101100010000110001111110111001011111010101001Fig.

9MSB-1:0的周期性而在Graycode的方式下,由于GrayCode是一种带有镜像对称的编码,故情况比较复杂.

增加一位后我们可以发现剩下的几位并不像BinaryCode那样可以重复出现,而是关于中间对称.

如Fig.

10中,(2:0)关于中心对称,分成的两部分则(1:0)关于中心对称,既然这样,我们可以知道对n+1bit采用GrayCode,n-1bit的编码带有周期为2n周期性.

但是仅是n-1bit,而我们需要的是nbit的地址.

Fig.

10GrayCode镜像对称特性MSB和MSB-1可以进行异或运算作为新的nbit地址的最高位来获得nbit地址(实质上是将+1bit的Graycode转换成nbit的GrayCode).

如Fig.

11中,按照前面所说的方法,将内外圈进行转换,在转换后的图中内外圈的数字完全一样,这样就产生的nbit的周期为2n的地址.

此时由于n+1bit缩减为nbit,不能够用缩减以后的地址来判断是空还是满,但是可以用转换以前的MSB来判断.

把转换前的MSB和转换后的(MSB-1:0)合并成一个新的指针.

这样的表示方法即可以起到判断空满状态,指针中直接包含译码的地址.

利用这种方法,空满的判断和采用BinaryCode方法一样了.

在rptr(MSB-1:0)=wptr(MSB-1:0)条件下,rptr(MSB)=wptr(MSB)则代表为队列为空,rptr(MSB)≠wptr(MSB)代表为队列为满.

这样的做法中还存在一个问题,可以发现在边界处的变化出现了存在2bit的变化过程,如1100->0000,0100->1000,这是一种折中的方法,但可以通过整体系统结构的设计来解决这个问题,我们将在后面讨论.

0000000100110010011001110101010010001001101110101110111111011100(2:0)对称(1:0)对称(1:0)对称Fig.

11GrayCode变换采用GrayCode也必须使用GrayCode的累加器,然而GrayCode的累加器的实现并不容易.

在Fig.

12中,采用BinaryCode累加,将得到的BinaryCode转换成为GrayCode.

加法器的两个加数中,一个是经GrayCode转换成为BinaryCode的数,另一个1bit可以认为是累加器的使能端.

当其为0时,相加后数字不改变,相当于累加器暂停累加;当其为1时,相加后数字增加1,相当于处于累加状态.

控制的使能信号和满或空标志共同作用,当使能为0时,数据不写入(或不读出),则内部的累加器暂停累加,读(写)指针不发生改变.

但是当数据写满(读空)指针也不能发生改变,故累加器也需要暂停累加.

由前面所提到的GrayCode改进方法可以在此图中体现出来,gnext是BinaryCode经过转换后成为GrayCode,将其最高两位进行异或运算成为msbnext通过clk时钟同步锁存,那么在使用地址译码时仅需要将这个得到的结果addrmsb和ptr(n-2:0)组成新的序列就是正确的了.

Fig.

12GrayCode累加器方案一还有一种改进的方案值得讨论一下,在上图中加法器的bin数据其实是经过Binarycode到Graycode转换经过锁存后再由GrayCode到Binarycode转换,需要用到2个转换逻辑电路.

如果把寄存器位置改放到加法器的输出位置,把Binarycode到Graycode转换逻辑置于锁存器输出的位置,那么加法器的bin输入可以直接从寄存器输出得到.

这种改进带来的另一个好处就是不需要产生和寄存addrmsb的逻辑,因为MSBBinaryCode就是addrmsb.

从对于外部电路看来,这种改变带来的唯一区别就是ptr[n:0]在时钟clk上升沿后到改变的Delay增加了,但是只要这个Delay较短这并不影响整个FIFO系统,因为ptr[n:0]是被一个异步的时钟所采样,增加的Delay不产生影响.

由BinaryCode到GrayCode转换公式可以的得到如下代码:rgnext=(rbnext>>1)^rbnext;这个单元的最大延时为一级异或门的延时.

以上改进的方案实现可以见Fig.

13.

当然,如果希望拥有一个深度为32字节(小规模的)的FIFO时,可在格雷码编码的状态机中手工编写计数器代码或是用查找表的方法来实现都是不错的选择.

Fig.

13GrayCode累加器方案二III.

整体结构异步FIFO整体结构可以分为四大模块:写指针控制(FIFOwptr&full)、读指针控制(FIFOrptr&empty)、双端口RAM(FIFOMemoryDualPortRAM)和同步采样模块(sync_r2wsync_w2r).

Fig.

14一种异步FIFO整体结构此结构的中读写指针通过两个同步采样模块交叉传递,使得产生FULL和EMPTY.

wptr和rptr是异步的,试分析一种情形,当rclk频率远大于wclk,则rptr的更新速度远大于wclk,那么从rptr数据更新后,到经sync_r2w同步的wrptr2和wptr产生FULL的时刻,rptr更新了许多次,即又从FIFO中读取了好几个数据,显然此时FIFO并不满.

相反的,有EMPTY产生时,FIFO并不空的情况.

这是一种保守的做法,即等效于提前产生空或满的标志,以保证数据不丢失,这样付出的代价是实际FIFO的空间变小了.

更一般地情形,是前文提到同步采样模块中会有一个时钟周期地Latency,那么当假设当写时钟上升沿后产生FULL时,是由于写指针赶上了一个同步的读指针,那么FULL的信号是准确和即时的.

但是在这个系统中,比较输出FULL中的读指针是被同步采样的异步信号.

当读指针更新一次后,FIFO不再是满的了,但是FULL产生的电路需要在写时钟两个周期后才能将读指针更新到写时钟域中,在此之间除时钟上升沿时刻以外的改变都将无法被同步模块探测到(如Fig.

15).

Fig.

15异步和同步数据对FULL影响在读写时钟差不多的情况下,FIFO的空间也不可能100%地利用,理想地情况是可利用的空间比总量小一,我们一般不计较.

在有些FIFO的设计中不仅会有FULL和EMPTY还会有如AlmostFULL,AlmostEMPTY信号输出.

这一类输出的处理方法就是把读来的指针多加几位进行,在同产生FULL和EMPTY的方法一样对两个指针进行比较.

waddr,wptr,raddr,rptr这四个信号都是GrayCode,注意到前文提到需要采用改进型GrayCode编码方式中提到会有两位同时变化的情况,在整体设计中我们依旧在外部的指针传递中采用GrayCode,能够保证指针信号被同步模块是每次仅有1bit的变化,而在读写控制模块内部采用改进型GrayCode编码,即将输入的wrptr2或rwptr2进行从GrayCode到改进型的转换,是传递后转换,而不是在输出wptr,rptr时进行转换后传递.

异步FIFO中复位采用异步Reset.

且在Reset后各个信号初始值的确定没有多少问题,例如指针值reset后无论是多少都无碍大妨,在环形的队列中,只要读写指针Reset后相同就可以了.

FIFO的关键输出FULL和EMPTY在reset后为了保守考虑都为'1'较为合理.

IV.

测试和结果测试一个异步的FIFO设计正确性几乎很困难,原因就在于即使FIFO指针在RTL的行为仿真是十分理想的,但是如果错误地RTL映射到实现的器件,关键路径的时序约束设计不合理将会导致致命的错误.

在RTL级仿真中,如果前面提到的控制指针的GrayCode累加器中Binary-count将会同步地改变所有的比特位想要查找出发生同步或者比较错误.

在没有寄生参数延时的门级仿真中,如果在时钟上升下降沿的不同,也仅仅有很小的几率能够发现问题的存在.

而对于更高速的设计,信号上升下降的延时之间的区别更加小了,发现问题的可能性也降低了.

所以实际的FIFO设计问题最好能够采用带有寄生参数的门级仿真,但即使是这样,一旦发现问题,有时候也能难再现错误.

基于以上考虑可以对FIFO进行功能上的仿真,再采用FPGA来验证测试FIFO,来模拟在真实器件中FIFO的特性.

采用XilinxSpartan3系列xc3s400-4pq208,综合工具XST.

综合的结果报告中:TimingSummary:488SpeedGrade:-4489Minimumperiod:9.

302ns(MaximumFrequency:107.

504MHz)490Minimuminputarrivaltimebeforeclock:9.

416ns491Maximumoutputrequiredtimeafterclock:12.

762ns492Maximumcombinationalpathdelay:Nopathfound493其中Timingconstraint:DefaultperiodanalysisforClock'wclk'502Clockperiod:9.

302ns(frequency:107.

504MHz)503Totalnumberofpaths/destinationports:1402/667504Timingconstraint:DefaultperiodanalysisforClock'rclk'528Clockperiod:8.

912ns(frequency:112.

205MHz)529Totalnumberofpaths/destinationports:260/21530在更为详细的报告中可以看到对于FULL和EMPTY信号通路是关键路径决定整体FIFO最高工作时钟,如果需要进一步提高FIFO的速度其重点是要对FULL和EMPTY加以改进数据写入读出的正确性取决于对FIFO模块中双端口RAM的操作.

但是前面提到,仅仅是看仿真结果是很难发现问题,基于此本文设计的一种测试思路是设计一个发送一个接收的控制器,发送控制器用于发送连续循环的数据从00~FF到FIFO,而接收模块用于从FIFO读出数据并进行数据的校验.

发送的是连续的数据码流,那么如果接收到的数据流中检测出数据的不连续,那么就有错误ERROR信号产生.

发送和接收模块分别使用不同频率不同相位的时钟,然后采用XilinxChipscope对FPGA内中的信号进行测试.

如果在Chipscope中未发现ERROR信号为高时,不能够完全说明不产生ERROR因为Chipscope的采样深度有限,且只能采用全局时钟作为采样时钟.

可以将ERROR从FPGA管脚引出,用示波器的单次触发功能对其进行测量,如果示波器长时间地没有被触发,则表明FIFO工作一切正常.

从Chipscope中记录的数据中来看,如果读写时钟的稳定性很好时,FULL和EMPTY的信号具有周期性,且有如下的关系2rclkwclkFULLfff=,rclkwclkff>2wclkrclkEMPTYfff=,rclkwclkff5必然地,由于写入读出的速度之差,当写时钟大于读时钟时,FIFO一定会被写满,然后产生FULL,反之写时钟大于读时钟时,FIFO一定会被读空,然后产生EMPTY.

当读写时钟相同时FULL和EMPTY的频率不仅取决读写时钟之间的相位差,还取决于系统的特性很难加以计算出.

而这个相位差具有一定的随机性,所以FULL和EMPTY很难观测出周期性,而更带有一定的随机性.

在FIFO复位以后,读写指针都归零,RAM内数据为空,一旦FIFO满或空后就进入一个稳定的状态,驰豫时间取决于读写时钟频率之差的.

Fig.

16读110MHz写120MHz下的FULL信号Fig.

17读空后的情形Fig.

18EMPTY的周期性Fig.

19发送端数据流Fig.

20Reset后FULL的随机性Fig.

21Reset后FULL的随机性在验证FIFO功能正确性时,手工验证时,只要观察RX模块中data_tmp是否连续,或者直接观察ERROR信号是否为'1'.

由于Chipscope只能用一个时钟采样信号,所以没有办法同时采样异步的发送和接收端数据信号,所以只能分成发送、接受两次测试.

注意以上的波形图中TX代表发送端,RX代表接受端故,在TX中EMPTY和RX_EN是异步的采样的数据是不可信的,在RX中FULL和TX_EN是异步的采样的数据是不可信的.

图中信号data_fifo始终表示的是从FIFO到RX端的数据,所以在一TX时钟采样时是不可信的.

(详细实现FIFO代码,测试模块代码以及测试数据结果见)

综述在多时钟域系统的设计中,跨时钟域的设计在所难免,尤其是在设计模块和外围芯片通信中出现.

当数据从一个时钟域向另一个异步时钟域传递的过程中,由于不同速率器件间的速率匹配问题,一般不能够通过直接传递保证数据传输的正确、完整性,故需要有一个中间数据缓冲来保证数据能够准确无误的传递.

FIFO(FirstInFirstOut)是一种队列,数据从一端进队列,另一端出队列,先进入队列的数据先被读取出,这种机制可以保证数据的时序上的正确性.

除此之外对FIFO的应用不仅仅是跨时钟域接口设计,在同步系统中可以起到防止时钟抖动等因素造成的数据传输错误提高系统稳定性能.

FIFO有同步和异步之分,同步的FIFO的读写时钟为同一时钟信号,而异步FIFO的读写时钟相互独立互不影响.

由于缓冲区是RAM,需要引入读写指针.

写指针总是指向下一个将要被写入的地址,在Reset后归零地址;读指针总是指向当前待读出的指针,在Reset后归零.

0F1U2D3A4N5U6N7I8V9101112131415wptrrptr0F1U2D3A4N5U6N7I8V9E101112131415wptrrptrDataEDataNDataRDataN0F1U2D3A4N5U6N7I8V9E101112131415wptrrptrDataRDataUOriginalStateWriteaByteReadaByteFig.

1读写指针工作原理在进行设计时同步和异步FIFO的最大区别就在于读写指针是否为同步或异步.

同步FIFO中wptr与rptr在同一时钟上升沿变化,而对于异步而言,读指针仅仅在读时钟上升沿变化,写指针仅仅在写时钟上升沿变化.

FIFO的缓冲区空间是有限的,在设计中需要考虑缓冲区的溢出和空的情况.

在缓冲区满时,产生FULL信号,以阻塞数据继续向FIFO写入.

而在缓冲区空时,产生EMPTY信号,以阻塞数据继续从FIFO中读出.

外部的读写控制器将从标志信号FULL、EMPTY决定继续写入或读出.

这种判断是基于对读指针和写指针指向的地址来判断的.

判断标志信号是FIFO的设计重点之一.

在同步的FIFO中读指针和写指针是同步的,所以在时钟的上升沿时比较判断FULL或EMPTY时,读指针和写指针指向的地址都是实际指针所指向的;而异步FIFO的读写指针是不同步的,这样就会造成在进行判断比较时,无论采用读时钟还是写时钟上升沿去判断FULL或EMPTY都将不合适.

所以在异步FIFO中需要一种机制使得能够将读写指针准确传递,一种解决方法是采用握手协议来保证在采样过程中指针不变,但是这样的做法效率很低.

另一种是通过读时钟来采样写指针,写时钟来采样读指针,然后通过采样的写指针和读指针判断是否为EMPTY,采样的读指针和写指针判断是否为FULL.

EMPTY信号对于读时钟而言是同步的,FULL信号对于写时钟是同步的.

Fig.

2一种同步FIFO的读写时序Fig.

3一种异步FIFO的读写时序II.

深入考虑在前面提到如果打算用写时钟取样读指针或用读时钟来取样写指针,将不可避免的遇到一个亚稳态的问题,它将会导致空、满标志的判断错误,并导致设计的失败.

下面分析亚稳态的产生原因和消除方法.

对于采样电路中,一个信号在过渡到另一个时钟域时,如果仅仅用一个触发器将其锁存,那么采样的结果将可能是亚稳态.

这也就是信号在跨时钟域时应该注意的问题.

如Fig.

4中时钟a,b是异步的,第二个触发器通过时钟b采样由寄存器锁存的数据data_a.

显然这种做法是冒险的,我们可以知道触发器工作过程中存在数据的建立(setup)和保持(hold)时间.

对于使用上升沿触发的触发器来说,建立时间就是在时钟上升沿到来之前,触发器数据端数据保持稳定的最小时间.

而保持时间是时钟上升沿到来之后,触发器数据端数据还应该继续保持稳定的最小时间.

我们把这段时间成为setup-hold时间.

在这个时间参数内,输入信号在时钟的上升沿是不允许发生变化的.

如果输入信号在这段时间内发生了变化,输出结果将是不可知的,即亚稳态(Metastability).

信号data经过一个锁存器的输出数据为data_a.

用时钟b_clk进行采样的时候,如果data_a正好在b_clk的setup-hold时间内发生变化,此时data_b就既不是逻辑"1",也不是逻辑"0",而是处于中间状态.

经过一段时间之后,有可能回升到高电平,也有可能降低到低电平.

输出信号处于中间状态到恢复为逻辑"1"或逻辑"0"的这段时间,我们称之为亚稳态时间.

Fig.

4采样电路Fig.

5D触发器的设定保持特性Fig.

6由采样电路产生的亚稳态时序为了考量亚稳态发生的几率可以用参数MTBF(MeanTimeBetweenFailures,平均无故障时间间隔)来描述,MTBF即触发器采样失败的时间间隔,表示为:dataclkresffTtMTBF**=0)/exp(τEq.

1上式rest中为分辨时间,τ和0T为触发器器件特性触发器特性相关参数,clkf是采样时钟频率,dataf是异步信号的触发频率.

如果MTBF很大,就认为这个设计在实际工作中是能够正常运行的,不会因为亚稳态导致整个系统的失效.

当触发器处于亚稳态,且处于亚稳态的时间超过了一个时钟周期,这种不确定的状态还会影响到下一级的触发器,最终导致连锁反应,从而使整个系统功能失常.

为了避免进入亚稳态,应当使参数MTBF尽可能大.

通常采用的方法是双锁存器法,即在一个信号进入另一个时钟域Fig.

7双锁存器法之前,将该信号用两个锁存器连续锁存两次(如图Fig.

7所示),由前给出的MTBF公式可以得到两级触发器的MTBF公式:)/1exp()/exp(02ττpdclkdataclkrestfffTtMTBF***=Eq.

2一般而言τ>>rest所以exp的增长比分母的平方增长快,所以在其他参数不变的条件下Eq.

2比Eq.

1来得大,data_c进入亚稳态的几率就更加减小.

依次类推,多增加锁存器的级数可以进一步降低出现亚稳态的几率,但是作为平衡考虑一般采用2级MTBF就已经足够大了.

Fig.

8双锁存器采样异步信号时序引入两级锁存器的同时带来了对输入信号的一级延时,再如a_clk的频率比b_clk的频率高,将可能出现因为dat变化太快,而使b_clk无法采样的问题.

即在信号从快时钟域向慢时钟域过渡的时候,如果信号变化太快,慢时钟将可能无法对该信号进行正确的采样,所以在使用双锁存器法的时候,应该使原始信号保持足够长的时间,以便另一个时钟域的锁存器可以正确地对其进行采样.

但是在这里的FIFO设计中并不需要过于关心这个两问题,原因将在后面分析.

采用双锁存器可以大大降低亚了稳态的出现几率,但是完全消除亚稳态是不可能的,一旦发生亚稳态那么读写指针所读取的数据就会发生错误.

读写指针在每次写入或读取之后会Fig.

7双锁存器法加一以使指针指向下一个地址,一般我们会采用Binarycode.

但是采用Binarycode是相邻的两个数之间可能有若干位bit改变(7->8==0111->1000四位全部改变),这样增加了产生亚稳态的几率.

一种很好的解决方法是采用Graycode来对地址进行编码.

Graycode是一种最小距离编码方式,既相邻的两数时间仅有1bit的差别,那么在FIFO应用中每次仅有一位改变,OrderBinaryCodeGrayCodeConvertRules000000000G->B100010001nnGB=1+=iiiBGBni≠Eq.

3200100011300110010401000110501010111601100101701110100810001100B->G910011101nnBG=1+=iiiBBGni≠E.

q4101010111111101111101211001010131101101114111010011511111000Table.

1BinaryGrayCode对照以及转换方法读写指针采用了Graycode那么地址译码将使用Graycode,判断空、满就和采用Binarycode就不一样了,接着我们详细分析.

为了最大限度利用RAM资源,FIFO一定是环形队列.

对于环形队列判断其是否空还是满的准则是:当读指针赶上写指针时,队列为空;当写指针赶上读指针时,队列为满.

显然只要是读写的指针的地址n位全都相同就会有空或满的状态,显然这样并不能区分空或满的状态.

则当对2n个地址进行编码时,如果我们再增加一位,即利用n+1位对2n个地址进行编码时,MSB可以表示是读指针赶上写指针还是写指针赶上读指针.

如果是Binarycode的方式,以n=3为例(如Fig.

9)给23个地址编码,多加一位,则一共有23+1个编码,从0000到0111,从1000到1111.

我们可以看到尽管MSB有变化,但是其余的位是相同的在地址译码的过程中,存在周期性只需要取后三位就是地址了.

对于判断空、满则在rptr(MSB-1:0)=wptr(MSB-1:0)条件下rptr(MSB)=wptr(MSB)则代表为队列为空,rptr(MSB)≠wptr(MSB)代表为队列为满;0000011101010100001101100010000110001111110111001011111010101001Fig.

9MSB-1:0的周期性而在Graycode的方式下,由于GrayCode是一种带有镜像对称的编码,故情况比较复杂.

增加一位后我们可以发现剩下的几位并不像BinaryCode那样可以重复出现,而是关于中间对称.

如Fig.

10中,(2:0)关于中心对称,分成的两部分则(1:0)关于中心对称,既然这样,我们可以知道对n+1bit采用GrayCode,n-1bit的编码带有周期为2n周期性.

但是仅是n-1bit,而我们需要的是nbit的地址.

Fig.

10GrayCode镜像对称特性MSB和MSB-1可以进行异或运算作为新的nbit地址的最高位来获得nbit地址(实质上是将+1bit的Graycode转换成nbit的GrayCode).

如Fig.

11中,按照前面所说的方法,将内外圈进行转换,在转换后的图中内外圈的数字完全一样,这样就产生的nbit的周期为2n的地址.

此时由于n+1bit缩减为nbit,不能够用缩减以后的地址来判断是空还是满,但是可以用转换以前的MSB来判断.

把转换前的MSB和转换后的(MSB-1:0)合并成一个新的指针.

这样的表示方法即可以起到判断空满状态,指针中直接包含译码的地址.

利用这种方法,空满的判断和采用BinaryCode方法一样了.

在rptr(MSB-1:0)=wptr(MSB-1:0)条件下,rptr(MSB)=wptr(MSB)则代表为队列为空,rptr(MSB)≠wptr(MSB)代表为队列为满.

这样的做法中还存在一个问题,可以发现在边界处的变化出现了存在2bit的变化过程,如1100->0000,0100->1000,这是一种折中的方法,但可以通过整体系统结构的设计来解决这个问题,我们将在后面讨论.

0000000100110010011001110101010010001001101110101110111111011100(2:0)对称(1:0)对称(1:0)对称Fig.

11GrayCode变换采用GrayCode也必须使用GrayCode的累加器,然而GrayCode的累加器的实现并不容易.

在Fig.

12中,采用BinaryCode累加,将得到的BinaryCode转换成为GrayCode.

加法器的两个加数中,一个是经GrayCode转换成为BinaryCode的数,另一个1bit可以认为是累加器的使能端.

当其为0时,相加后数字不改变,相当于累加器暂停累加;当其为1时,相加后数字增加1,相当于处于累加状态.

控制的使能信号和满或空标志共同作用,当使能为0时,数据不写入(或不读出),则内部的累加器暂停累加,读(写)指针不发生改变.

但是当数据写满(读空)指针也不能发生改变,故累加器也需要暂停累加.

由前面所提到的GrayCode改进方法可以在此图中体现出来,gnext是BinaryCode经过转换后成为GrayCode,将其最高两位进行异或运算成为msbnext通过clk时钟同步锁存,那么在使用地址译码时仅需要将这个得到的结果addrmsb和ptr(n-2:0)组成新的序列就是正确的了.

Fig.

12GrayCode累加器方案一还有一种改进的方案值得讨论一下,在上图中加法器的bin数据其实是经过Binarycode到Graycode转换经过锁存后再由GrayCode到Binarycode转换,需要用到2个转换逻辑电路.

如果把寄存器位置改放到加法器的输出位置,把Binarycode到Graycode转换逻辑置于锁存器输出的位置,那么加法器的bin输入可以直接从寄存器输出得到.

这种改进带来的另一个好处就是不需要产生和寄存addrmsb的逻辑,因为MSBBinaryCode就是addrmsb.

从对于外部电路看来,这种改变带来的唯一区别就是ptr[n:0]在时钟clk上升沿后到改变的Delay增加了,但是只要这个Delay较短这并不影响整个FIFO系统,因为ptr[n:0]是被一个异步的时钟所采样,增加的Delay不产生影响.

由BinaryCode到GrayCode转换公式可以的得到如下代码:rgnext=(rbnext>>1)^rbnext;这个单元的最大延时为一级异或门的延时.

以上改进的方案实现可以见Fig.

13.

当然,如果希望拥有一个深度为32字节(小规模的)的FIFO时,可在格雷码编码的状态机中手工编写计数器代码或是用查找表的方法来实现都是不错的选择.

Fig.

13GrayCode累加器方案二III.

整体结构异步FIFO整体结构可以分为四大模块:写指针控制(FIFOwptr&full)、读指针控制(FIFOrptr&empty)、双端口RAM(FIFOMemoryDualPortRAM)和同步采样模块(sync_r2wsync_w2r).

Fig.

14一种异步FIFO整体结构此结构的中读写指针通过两个同步采样模块交叉传递,使得产生FULL和EMPTY.

wptr和rptr是异步的,试分析一种情形,当rclk频率远大于wclk,则rptr的更新速度远大于wclk,那么从rptr数据更新后,到经sync_r2w同步的wrptr2和wptr产生FULL的时刻,rptr更新了许多次,即又从FIFO中读取了好几个数据,显然此时FIFO并不满.

相反的,有EMPTY产生时,FIFO并不空的情况.

这是一种保守的做法,即等效于提前产生空或满的标志,以保证数据不丢失,这样付出的代价是实际FIFO的空间变小了.

更一般地情形,是前文提到同步采样模块中会有一个时钟周期地Latency,那么当假设当写时钟上升沿后产生FULL时,是由于写指针赶上了一个同步的读指针,那么FULL的信号是准确和即时的.

但是在这个系统中,比较输出FULL中的读指针是被同步采样的异步信号.

当读指针更新一次后,FIFO不再是满的了,但是FULL产生的电路需要在写时钟两个周期后才能将读指针更新到写时钟域中,在此之间除时钟上升沿时刻以外的改变都将无法被同步模块探测到(如Fig.

15).

Fig.

15异步和同步数据对FULL影响在读写时钟差不多的情况下,FIFO的空间也不可能100%地利用,理想地情况是可利用的空间比总量小一,我们一般不计较.

在有些FIFO的设计中不仅会有FULL和EMPTY还会有如AlmostFULL,AlmostEMPTY信号输出.

这一类输出的处理方法就是把读来的指针多加几位进行,在同产生FULL和EMPTY的方法一样对两个指针进行比较.

waddr,wptr,raddr,rptr这四个信号都是GrayCode,注意到前文提到需要采用改进型GrayCode编码方式中提到会有两位同时变化的情况,在整体设计中我们依旧在外部的指针传递中采用GrayCode,能够保证指针信号被同步模块是每次仅有1bit的变化,而在读写控制模块内部采用改进型GrayCode编码,即将输入的wrptr2或rwptr2进行从GrayCode到改进型的转换,是传递后转换,而不是在输出wptr,rptr时进行转换后传递.

异步FIFO中复位采用异步Reset.

且在Reset后各个信号初始值的确定没有多少问题,例如指针值reset后无论是多少都无碍大妨,在环形的队列中,只要读写指针Reset后相同就可以了.

FIFO的关键输出FULL和EMPTY在reset后为了保守考虑都为'1'较为合理.

IV.

测试和结果测试一个异步的FIFO设计正确性几乎很困难,原因就在于即使FIFO指针在RTL的行为仿真是十分理想的,但是如果错误地RTL映射到实现的器件,关键路径的时序约束设计不合理将会导致致命的错误.

在RTL级仿真中,如果前面提到的控制指针的GrayCode累加器中Binary-count将会同步地改变所有的比特位想要查找出发生同步或者比较错误.

在没有寄生参数延时的门级仿真中,如果在时钟上升下降沿的不同,也仅仅有很小的几率能够发现问题的存在.

而对于更高速的设计,信号上升下降的延时之间的区别更加小了,发现问题的可能性也降低了.

所以实际的FIFO设计问题最好能够采用带有寄生参数的门级仿真,但即使是这样,一旦发现问题,有时候也能难再现错误.

基于以上考虑可以对FIFO进行功能上的仿真,再采用FPGA来验证测试FIFO,来模拟在真实器件中FIFO的特性.

采用XilinxSpartan3系列xc3s400-4pq208,综合工具XST.

综合的结果报告中:TimingSummary:488SpeedGrade:-4489Minimumperiod:9.

302ns(MaximumFrequency:107.

504MHz)490Minimuminputarrivaltimebeforeclock:9.

416ns491Maximumoutputrequiredtimeafterclock:12.

762ns492Maximumcombinationalpathdelay:Nopathfound493其中Timingconstraint:DefaultperiodanalysisforClock'wclk'502Clockperiod:9.

302ns(frequency:107.

504MHz)503Totalnumberofpaths/destinationports:1402/667504Timingconstraint:DefaultperiodanalysisforClock'rclk'528Clockperiod:8.

912ns(frequency:112.

205MHz)529Totalnumberofpaths/destinationports:260/21530在更为详细的报告中可以看到对于FULL和EMPTY信号通路是关键路径决定整体FIFO最高工作时钟,如果需要进一步提高FIFO的速度其重点是要对FULL和EMPTY加以改进数据写入读出的正确性取决于对FIFO模块中双端口RAM的操作.

但是前面提到,仅仅是看仿真结果是很难发现问题,基于此本文设计的一种测试思路是设计一个发送一个接收的控制器,发送控制器用于发送连续循环的数据从00~FF到FIFO,而接收模块用于从FIFO读出数据并进行数据的校验.

发送的是连续的数据码流,那么如果接收到的数据流中检测出数据的不连续,那么就有错误ERROR信号产生.

发送和接收模块分别使用不同频率不同相位的时钟,然后采用XilinxChipscope对FPGA内中的信号进行测试.

如果在Chipscope中未发现ERROR信号为高时,不能够完全说明不产生ERROR因为Chipscope的采样深度有限,且只能采用全局时钟作为采样时钟.

可以将ERROR从FPGA管脚引出,用示波器的单次触发功能对其进行测量,如果示波器长时间地没有被触发,则表明FIFO工作一切正常.

从Chipscope中记录的数据中来看,如果读写时钟的稳定性很好时,FULL和EMPTY的信号具有周期性,且有如下的关系2rclkwclkFULLfff=,rclkwclkff>2wclkrclkEMPTYfff=,rclkwclkff

当读写时钟相同时FULL和EMPTY的频率不仅取决读写时钟之间的相位差,还取决于系统的特性很难加以计算出.

而这个相位差具有一定的随机性,所以FULL和EMPTY很难观测出周期性,而更带有一定的随机性.

在FIFO复位以后,读写指针都归零,RAM内数据为空,一旦FIFO满或空后就进入一个稳定的状态,驰豫时间取决于读写时钟频率之差的.

Fig.

16读110MHz写120MHz下的FULL信号Fig.

17读空后的情形Fig.

18EMPTY的周期性Fig.

19发送端数据流Fig.

20Reset后FULL的随机性Fig.

21Reset后FULL的随机性在验证FIFO功能正确性时,手工验证时,只要观察RX模块中data_tmp是否连续,或者直接观察ERROR信号是否为'1'.

由于Chipscope只能用一个时钟采样信号,所以没有办法同时采样异步的发送和接收端数据信号,所以只能分成发送、接受两次测试.

注意以上的波形图中TX代表发送端,RX代表接受端故,在TX中EMPTY和RX_EN是异步的采样的数据是不可信的,在RX中FULL和TX_EN是异步的采样的数据是不可信的.

图中信号data_fifo始终表示的是从FIFO到RX端的数据,所以在一TX时钟采样时是不可信的.

(详细实现FIFO代码,测试模块代码以及测试数据结果见)

- 指针计数器代码相关文档

- "十二五"普通高等教育本科国家级规划教材

- 记数器[新版]计数器原代码

- 毕业设计(毕业设计)转速表计数器的设计制作之程序代码

- 计数器锁存器、可逆计数器、任意进制计数器、分频器源程序代码

- 波形Verilog代码(计数器、交通灯、串并转换)

- 定时器《微机原理及应用》作业参考(浙江大学)定时计数器代码

PhotonVPS:美国Linux VPS半价促销2.5美元/月起,可选美国洛杉矶/达拉斯/芝加哥/阿什本等四机房

photonvps怎么样?photonvps现在针对旗下美国vps推出半价促销优惠活动,2.5美元/月起,免费10Gbps DDoS防御,Linux系统,机房可选美国洛杉矶、达拉斯、芝加哥、阿什本。以前觉得老牌商家PhotonVPS贵的朋友可以先入手一个月PhotonVPS美国Linux VPS试试了。PhotonVPS允许合法大人内容,支持支付宝、paypal和信用卡,30天退款保证。Photo...

lcloud零云:沪港IPLC,70元/月/200Mbps端口/共享IPv4/KVM;成都/德阳/雅安独立服务器低至400元/月起

lcloud怎么样?lcloud零云,UOVZ新开的子站,现在沪港iplc KVM VPS有端午节优惠,年付双倍流量,200Mbps带宽,性价比高。100Mbps带宽,500GB月流量,10个,512MB内存,优惠后月付70元,年付700元。另有国内独立服务器租用,泉州、佛山、成都、德阳、雅安独立服务器低至400元/月起!点击进入:lcloud官方网站地址lcloud零云优惠码:优惠码:bMVbR...

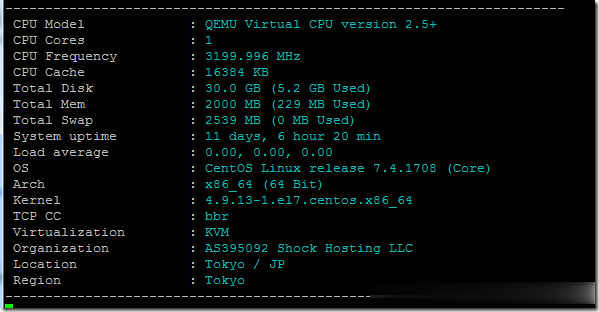

ShockHosting日本机房VPS测试点评

这个月11号ShockHosting发了个新上日本东京机房的邮件,并且表示其他机房可以申请转移到日本,刚好赵容手里有个美国的也没数据就发工单申请新开了一个,这里做个简单的测试,方便大家参考。ShockHosting成立于2013年,目前提供的VPS主机可以选择11个数据中心,包括美国洛杉矶、芝加哥、达拉斯、杰克逊维尔、新泽西、澳大利亚、新加坡、日本、荷兰和英国等。官方网站:https://shoc...

计数器代码为你推荐

-

亿元企业linux防火墙设置LINUX系统怎么关闭防火墙dell服务器bios设置戴尔服务器720bios设置硬盘启动青岛网通测速网通,联通,长城这三个宽带哪个网速最快?我是青岛的即时通EC营销即时通是什么?做什么的?美国独立美国是什么时候独立的?开源网店免费开源网上商城系统有哪些店铺统计店铺运营数据分析,运营要看哪些店铺数据drupal主题4)Drupal建立的网站是否可以自适配屏幕大小,在PC、iPad、iPhone等各机器的浏览器中是否可以正常显示discuz7.2求解答Discuz!7.2 论坛怎么设置