输出触发器的作用

触发器的作用 时间:2021-04-05 阅读:()

1组合电路应用实验1.

字符编码显示电路实验1.

实验目的(1)掌握组合电路逻辑功能的测试方法.

(2)掌握TTL逻辑门组合应用和七段显示器使用方法.

(3)了解组合逻辑电路的设计方法.

2.

实验原理组合逻辑电路的输出状态完全取决于同一时刻输入状态的组合,与电路原来的输出状态无关.

图3-2-5是一个由逻辑门构成编码显示组合电路,可以分析,6个输出Ya,Yb,Yc,Yd,Ye,Yg与两个输入K1,K0有一一对应的逻辑关系.

两个输入组合成四种编码输出状态,控制七段显示器显示四个特定字符.

(1)七段共阴显示器原理七段显示器内部由八个发光二极管组成,七个段划和一个小数点,位置排成"—.

"形.

八个发光二极管的连接方式有共阴接法和共阳接法两种.

共阳接法就是把所有发光二极管的阳极都接在一起,形成一个由高电平驱动的公共端COM,各管的阴极由低电平有效的段码信号a~g控制.

共阴接法则相反,它的公共端COM是所有发光二极管的阴极,由低电平驱动,而各段发光二极管的阳极由高电平驱动.

图3-2-1表示了七段共阴显示器的内部原理、外引线排列图以及常用显示符.

各段发光二极管正向导通时发光,导通电压UD约为2V,导通电流ID约需3-10毫安,电流太大可能会损坏器件.

所以,使用时必须根据所加信号的幅度选择限流电阻.

图3-2-5中,七段共阴显示器的公共端COM接地,段控制端a~g通过限流电阻接5V电源.

由于TTL逻辑门输出的高电平驱动能力有限,所以或非门输出通过反相缓冲器1413(2003)驱动显示器的a,b,c,d,e,g各段.

其中f直接通过限流电阻接电源,不受输入K1,K0控制,所以f段始终发光.

(2)集电极开路的反相缓冲器功能1413(2003)为集电极开路(OpenCollector)反相达林顿结构,内部有7个互相独立的复合达林顿管.

电路原理及引脚排列如图3-2-2(a)所示.

当缓冲器输入为低电平"0"时,复合管截止,OC输出为高阻状态,对外电路没有影响,相应段的发光管仍然导通;当缓冲器输入为高电平"1"时复合管导通,输出低电平使相应段的发光管截止.

所以当图3-2-5电路中或非门输出为"0"时,显示段亮,输出为"1"时,显示段灭.

2(3)动态扫描显示原理图3-2-5电路中采用一个显示器根据K0,K1控制显示不同的字符.

如果K0,K1由一个2位二进制计数器的输出控制,使K0,K1的状态呈"00"→"01"→"10"→"11"→"00"自动顺序变化,则四个字符亦随控制码顺序循环显示.

如果采用四个共阴显示器组成如图3-2-3所示的动态扫描显示电路,替代图3-2-5中的一个七段显示器,则四个显示字符可以同时稳定显示.

四个显示器的阳极a~g一一对应连接,由缓冲器的输出控制.

各显示器的阴极公共端信号Y0~Y3由K0,K1通过2线-4线通用译码器顺序产生,扫描控制时序如图3-2-4所示.

由于任意瞬时只有一个共阴显示器的阴极为低电平,所以此时反相缓冲器输出的阳极控制信号只能对该显示器有效,使之显示相应的字符,其他阴极为高电平的显示器呈灭显状态.

这样,扫描时钟信号CP控制计数器使各显示器分时轮流选通,同时控制逻辑门编码电路产生不同的字符显示段信号,使各显示器逐位顺序显示.

每位显示的时间为一个CP周期,显示扫描周期T为时钟周期的4倍.

只要扫描时钟频率足够高,使每个显示器每秒的导通次数大于50次(四位显示的扫描时钟频率大于200Hz),由于人眼的视觉暂留效应,可以观察到各位显示器同时显示.

时钟频率越高,显示越稳定.

33.

实验参考电路4.

实验预习要求(1)根据图3-2-5,列出电路各输出端的逻辑表达式,并将输入K1,K0为不同状态时,逻辑门电路的输出Ya,Yb,Yc,Yd,Ye,Yg和七段共阴显示器输入a~g及相应的显示字符填入表3-2-1中.

(2)用2输入与非门设计显示自选字符,如"H","O","P","E"("H","E","L","P"或"C","L","E","A"等).

列出真值表,写各输出的逻辑表达式,画出电原理图,标出引脚编号.

逻辑门的个数不能超过8个.

逻辑门采用四-2输入与非门74LS00,引脚排列见实验4.

1图4-1-2(c)(3)根据发光二极管发光时的导通电压和导通电流选择限流电阻的阻值.

*(4)根据动态扫描原理设计电路,画出电路原理图.

其中2位二进制计数器用双JK触发器构成,型号从附录中自选.

双2线-4线译码器的型号为74LS139,功能及引脚排列查阅实验3.

5图3-5-1.

(5)认真阅读实验内容与步骤部分,充分了解实验方法和过程.

表3-2-1图3-2-5电路输入、输出逻辑关系K1K0YaYbYcYdYeYgabcdefg显示字符00亮01亮10亮11亮5.

实验内容和步骤(1)检查实验装置与器件.

根据四-2输入或非门74LS02的逻辑功能检查器件.

或非门的输入信号由数字逻辑实验箱上的逻辑开关提供,输出状态用箱上的逻辑指示灯检查.

当任一开关的状态为高电平"1"时,或非门输出低电平"0",指示灯不亮.

当两个开关的状态均为低电平"0"时,或非门输出高电平"1",指示灯亮.

4(2)按图3-2-5电路连线,输入K1、K0接逻辑开关.

限流电阻采用8联集成电阻,9个引脚,内部连接方式如图3-2-5虚线框所示.

8联电阻的公共端有标记"",接+5V电源.

集成电阻直接插在反相缓冲器的输出引脚边,如图3-2-2所示,以减少连线.

缓冲器输出a~g接共阴显示器的段码输入端,显示器公共端COM接地.

根据表3-2-1改变开关状态,观察显示字符是否与分析的结果相同.

(3)按预习要求(2)设计的电路改接编码组合电路部分(缓冲器和显示器电路不变),观察显示结果并与设计要求比较.

*(4)用JK触发器连接成两位二进制异步计数器,控制编码显示电路的输入K1,K0,扫描时钟采用逻辑实验仪输出的1Hz脉冲信号,观察显示效果.

*(5)按预习内容(4)设计的电路连接动态扫描显示电路,扫描时钟频率改为1kHz,观察实验结果.

6.

实验设备和器材(1)数字逻辑实验箱1台(2)双列直插集成四-2输入TTL或非门74LS022片(3)双列直插集成四-2输入TTL与非门74LS001片(4)七段共阴显示器1个(5)九引脚8联集成电阻1个(6)集成七达林顿OC反相缓冲器1413(2003)1片*(7)双JK触发器1片*(8)2线-4线译码器74LS1391片(9)数字万用表1台7.

实验思考题(1)若限流电阻为1KΩ,当反相缓冲器输入Yb为"1"时,输出信号电平约为0.

3V左右.

根据发光二极管的导通电压和电流,图3-2-5电路中的I,ID,Io各为多少当Yb为"0"时,各电流又为多少(2)若动态扫描显示电路的时钟频率为1Hz,四位字符可能如何显示如果时钟频率为100Hz呢8.

实验报告要求(1)预习要求(1),(2)的内容.

(2)列出限流电阻参数选择的计算方法.

(3)回答思考题.

52.

编码器和译码器实验1.

实验目的(1)掌握中规模集成电路译码器、编码器的逻辑功能和使用方法.

(2)利用译码器、编码器进行组合逻辑电路设计.

2.

实验原理(1)编码器编码器的逻辑功能是将输入信号中的一个有效信号变换成相应的一组二进制代码输出.

优先编码器定义了所有输入信号的优先级别.

当多个输入信号同时有效时,优先编码器输出的是对应优先权最高的信号编码值.

图3–3–18线-3线优先编码器74LS148的引脚排列图图3–3–1给出8线-3线优先编码器74LS148的引脚排列图.

S为使能控制端或称选通输入端.

选通输出端YS和扩展端YEX的功能是实现编码位数(输入信号数)的扩展.

0IN~7IN是8个输入信号(编码对象),低电平有效.

7IN的优先权最高,0IN的优先权最低.

编码输出是3位二进制代码,用012YYY表示.

表3–3–1为8线-3线优先编码器的真值表.

表3–3–18线-3线优先编码器真值表输入输出S0IN1IN2IN3IN4IN5IN6IN7IN2Y1Y0YEXYSYlΦΦΦΦΦΦΦΦ0111111110ΦΦΦΦΦΦΦ00ΦΦΦΦΦΦ01OΦΦΦΦΦ0110ΦΦΦΦ01110ΦΦΦ0ll110ΦΦ0l11110*0111111001ll1111111111111000001001010100l011011000l101011100111101在S="0"时,编码器允许工作.

当70~ININ8个输入中有"0"时,输出一组优先6权最高的有效输入所对应的二进制代码.

比如当S="0"6431ININININ时,IN———6的优先权最高,输出2Y1Y0Y="001"(见表3-3-1第4行).

(2)译码器译码是编码的逆过程,它的逻辑功能是将每个输入的二进制代码,译成对应输出的高、低电平信号.

译码器有变量译码器和显示译码器之分.

①变量译码器变量译码器的逻辑功能是将输入的n位二进制代码译成2n个输出变量.

每个输出变量与唯一的一组输入码对应,当输入为某组码时,仅有与其对应的输出信号为有效电平,其他输出均为无效电平.

典型的变量译码器型号为3线-8线译码器74LS138.

图3–3–2所示为3线-8线译码器74LS138的引脚排列图.

图3–3–23线-8线译码器74LS138的引脚排列图.

其中012AAA为3条译码输入端,0Y~7Y为8条译码输出端,低电平有效.

1S,2S,3S为使能选通端.

表3–3–2所示为3线-8线译码器74LS138的真值表.

表3–3–23线-8线译码器真值表1S32SS2A1A0A0Y1Y2Y3Y4Y5Y6Y7Yφlφφφ0φφφφ1O0O0100011O01010011101001O101101101011111111111111111110111111110111111110111111110111111110111111110111111110111111110由表3–3–2可见,当1S="1",32SS="0"时,不论输入2A、1A、0A为何状态,输出0Y~7Y中有且仅有一个为有效电平"0",有效输出端的下标序号与输入二进制码所对应的十进制数相同.

变量译码器除了实现译码功能外,可以作为数据分配器使用.

如果利用使能选通端中的7一个输入串行数据信号,变量译码器就实现数据分配功能.

另外,变量译码器还可以用来方便地实现多输出逻辑函数.

②显示译码器把输入的二—十进制代码转换成十进制数码各段驱动信号的电路称为显示译码器.

图3–3–3为七段显示译码器74LS48的引脚排列图.

图3–3–3七段显示译码器74LS48引脚排列图其中03~AA为译码器的输入信号,gaYY~为译码器的7个输出,LT为译码器的灯测试输入,RBOBI/为译码器的消隐输入/灭零输出,RBI为灭零输入.

表3–3–3为七段显示译码器的真值表.

表3–3–3七段显示译码器的真值表十进制输入RBOBI输出或功能LTRBI3A2A1A0AaYbYcYdYeYfYgYOl23456789101112131415ll11111l1lll1ll11φφφφφφφφφφφφφφφ00000001001000110100010101100111100010011010l01111001101l110llll1l1lllll111l1l111l11l1001lO000110110lllll00l0ll00ll10l10ll00111111110000llllllll1l00ll000110100110010100011l0010llO00111100000008消隐脉冲消隐灯测试φ10φ0φφφφφ0000φφφφ00l00000000000000ll1lll1根据表3–3–3七段显示译码器74LS48的真值表,简单介绍三个功能端LT,RBOBI/和RBI的工作情况.

灯测试输入:当0LT且1BI时,无论03~AA状态如何,输出Ya~Yg全部为高电平,都可使被驱动数码管的七段同时点亮,以检查该数码管各段能否正常发光.

利用这个功能可以判断显示器的好坏.

消隐输入:也称灭灯输入.

BI为消隐输入,当BI=0时,无论RBILT,及输入03~AA为何值,所有各段输出gaYY~均为低电平,显示器处于熄灭状态.

RBO为灭零输出.

灭零输入:RBI可以按数据显示需要,将显示器所显示的0予以熄灭,而在显示1-9时不受影响.

它在实际应用中是用来熄灭多位数字前后不必要的零位,使显示的结果更醒目.

将灭零输入端与灭零输出端配合使用,很容易实现多位数码显示系统的灭零控制.

在数字系统中,经常需要将被测量或数值运算结果用十进制数码显示出来.

由于显示器件和显示方式不同,在各类显示器件中,目前使用最为广泛的是由发光二极管构成的七段显示数码管.

将七个发光二极管按一定的方式连接在一起,就构成七段显示数码管.

它有共阳极和共阴极两种连接方式,如图3–3–4所示.

(a)(b)(c)图3–3–4七段显示数码管结构(a)七段显示器(b)共阴极连接(c)共阳极连接本实验采用的型号为BS201共阴极式显示器,它与74LS48译码器配套使用.

3.

实验预习要求(1)复习有关编码器和译码器的原理.

(2)了解所用集成电路的功能和外部引线排列.

(3)根据实验任务,画出所需的实验电路图及记录表格4.

实验内容和步骤9(1)按上图接线,D0~D3接数字电路实验箱的电平按键开关,输出L1、L2接发光二极管,3位编码输出分别接内部带译码器的数码管1,2,4输入端,数码管端子8接地.

数电实验箱内部已经为这两个数码管设计连接了译码驱动电路,只要将四位二进制码接入就可显示16进制数0~F.

(2)D3接高电平,D2D1D0三位依次置入000~111,观察数码管显示.

记录此时的YEX和YS.

然后重新将D2D1D0三位置入011,将I6连接到Y6的导线74LS138输出端的一头拔出,改为接地,观察数码管显示.

将结果填入表3-19-4中.

(3)D3改接低电平,观察数码管显示,记录此时的YEX和YS.

将结果填入表3-19-4中.

5.

实验设备与器材(1)数字逻辑实验箱1台(2)双踪示波器1台(3)函数信号发生器1台(4)集成芯片:74LS148,74LS138,显示器若干6.

实验思考题(1)用一片74LS138和一片74LS20设计并实现一位全减器.

103.

数据选择器和数据分配器应用实验1.

实验目的(1)了解变量译码器和数据选择器的逻辑功能和具体应用.

(2)熟悉中规模组合逻辑器件功能的测试和设计方法.

2.

实验原理(1)变量译码器变量译码器有n个输入,2n个输出,每个输出唯一地对应一组输入构成的二进制码,当且仅当输入组合为该码时,输出呈有效电平.

中规模TTL集成译码器有74LS139(双2输入、4输出)、74LS138(3输入、8输出)和74LS154(4输入、16输出),输出均为低电平有效,并具有低电平有效的使能控制端S—-.

变量译码器除在数字系统中起二进制译码作用外,还可实现组合逻辑函数、数据分配等功能.

74LS139的引脚图如图3-5-1(a)所示,片上有两个独立的2线-4线译码器,各输出逻辑表达式为:Y——0=01AAS、Y——1=01AAS、Y——2=01AAS、Y——3=01AAS显然,当使能S—-为有效电平"0"时,如果译码器A1,A0输入的是逻辑函数的输入变量A,B,则Y——i代表了A,B构成的最小项mi的反函数(最大项).

所以,2线-4线通用译码器可附加与非门(与门)实现用标准与-或(标准或-与)表达式表示的二变量组合逻辑函数.

同理,n线-2n线通用译码器可实现n变量的组合逻辑函数.

如果把译码器的使能端S作为数据输入端,则可实现数据分配功能.

被分配的串行数字信号Di从S输入,当A1,A0为不同的二进制码时,Di信号被分配到译码器对应的输出端Y——i.

比如A1A0为"11"时,Di信号被分配到Y——3,此时Y——0~Y——2输出均为高电平.

(2)数据选择器数据选择器有n位控制信号,2n个数据输入.

每组控制码能够选择唯一的一个数据输出,类似由控制码切换的多选一开关.

中规模TTL集成数据选择器有74LS153(双4选1)和74LS151(8选1),都具有低电平有效的使能控制端S.

数据选择器的主要功能是实现多路11信号的选择,当控制端输入函数的逻辑变量、数据端输入函数值时,可以实现组合逻辑函数.

74LS153的引脚功能如图3-5-1(b)所示,片上有两个4选1数据选择器,控制端A1,A0共用.

输出逻辑表达式为:Y=S—-(A—1A—0D0+A—1A0D1+A1A—0D2+A1A0D3)图3-5-2为一个报警控制电路,其中数据选择器选择两个不同频率的信号控制音频蜂鸣器.

音频蜂鸣器的有效信号频率在20Hz~2kHz音频范围内,频率不同音调不同.

声音的强弱与音频蜂鸣器的驱动电流成正比.

由于TTL电路的驱动能力有限,为提高音量,采用NPN三极管9013进行电流放大.

三极管工作在开关状态,当数据选择器输出E为"0"时,三极管截止,蜂鸣器没有电流通过;当E为"1"时,三极管饱和,Uce约为0.

2V,蜂鸣器得电.

当E的信号切换频率在音频范围内时,蜂鸣器鸣响.

9013的引脚如图3-5-1(c)所示.

3.

实验参考电路(1)声光报警电路如图3-5-2所示.

(2)函数发生器如图3-5-3所示.

4.

实验预习要求(1)复习译码器、数据选择器及数据分配器的工作原理.

(2)分析图3-5-2电路的报警控制信号W的有效电平是高还是低报警时蜂鸣器的控制信号E是什么波形蜂鸣器的鸣叫声音可能是怎样的(3)根据图3-5-3列出电路输出CY和SUM的布尔表达式及真值表.

如果输入A,B,C是三个一位的二进制数,分析电路的逻辑功能.

(4)设计一个数据选择、分配电路,设计要求:①四个一位的输入数据D0,D1,D2,D3,用两个逻辑开关编码选择;②四个一位的输出数据Y0,Y1,Y2,Y3,另用两个逻辑开关编码选择;③功能:可以将四个输入数据中的任何一路信号Di选择并分配给四个输出中的任何一个Yi.

选择集成器件设计电路,画出电原理图,标明各集成器件的引脚编号.

(5)用74LS153设计一个一位二进制数的全减器.

输入三个一位的二进制数A,B,C,输出逻辑变量D和V.

其中D是A减B减C的差,V表示了A的值是否够被B,C减,够减时V="0",否则为"1".

列出真值表,画出电原理图.

(6)用74LS139和两个四输入与非门(或四输入与门)实现全减器,画出电原理图.

12(7)用4选1数据选择器74LS153和两位二进制计数器设计一个信号传输方式转换电路,把四位并行码D0~D3转换成一列串行信号.

要求转换位序可以根据需要选择先高位后低位或者相反.

画出设计的电路原理图.

5.

实验内容及步骤(1)译码器功能测试.

根据图3-5-1中74LS139的引脚图,任选其中一个2线-4线译码器测试其功能.

使能端S—-由1Hz脉冲信号控制,输入A1,A0由逻辑开关控制,四个输出Y0~Y3接逻辑指示灯(发光二极管).

改变输入A1,A0的状态,观察Y0~Y3的输出记录在表3-5-1中(记录输出状态是高电平、低电平或1Hz信号).

测试完成后保留电路.

表3-5-12线-4线通用译码器功能测试A1A0Y0Y1Y2Y300100111(2)4选1数据选择器功能测试根据图3-5-1中74LS153的引脚图,任选其中一个数据选择器测试其功能.

使能端S—-接有效电平(GND),四个数据端D0~D3分别输入1Hz,3Hz,10Hz和高电平(Vcc)信号.

其中1Hz,10Hz信号可取自逻辑实验箱上的脉冲信号区,3Hz信号由函数发生器TTL端输出.

用发光二极管观察数据选择器的输出端Y,改变输入A1,A0的状态,在表3-5-2中记录数据选择情况.

(记录输出信号频率或电平状态)表3-5-24选1数据选择器功能测试表输入A1A000011011输出Y(3)根据预习内容4设计的电路,在实验步骤(1),(2)的基础上连接数据选择、分配电路.

观察信号的选择分配情况.

(4)根据图3-5-2连接声光报警电路.

1Hz和1kHz脉冲信号都由逻辑实验箱提供,2kHz脉冲信号由函数发生器的TTL端输出.

报警信号W由逻辑开关控制,警灯L为逻辑指示灯.

改变W的状态,观察实验结果.

当W有效时,警笛鸣响,警灯L闪烁.

微调函数发生器频率,观察频率变化对蜂鸣器音调的影响.

(5)数据选择器构成的函数发生器根据图3-5-3连接电路.

输入A,B,C接逻辑开关,输出用逻辑指示发光二极管检查.

改变输入状态记录函数真值表,与预习时分析的结果比较.

(6)根据预习(5)设计的电路连线,观察实验结果是否满足设计要求.

(7)根据预习(6)设计的电路连线,观察实验结果是否满足设计要求.

(8)根据预习(7)设计的电路连线,观察实验结果是否满足设计要求.

136.

实验设备和器材(1)数字逻辑实验箱1台(2)函数发生器1台(3)双列直插集成TTL2线-4线译码器74LS1391片(4)双列直插集成TTL4选1数据选择器74LS1531片(5)双列直插集成TTL二-4输入与非门74LS201片(6)NPN三极管90131个7.

实验思考题(1)声光报警电路中,是否能用报警信号控制数据选择器的输入端A1为什么(2)如果实验内容(3)只用一组两位的二进制码同时控制数据的选择和分配,结果会如何8.

实验报告要求(1)预习内容要求.

(2)实验内容要求.

(3)回答思考题.

14时序电路应用实验4.

触发器基本功能测试实验1.

实验目的(1)学习触发器逻辑功能的测试方法.

(2)了解基本RS触发器、D触发器及JK触发器的逻辑功能及触发方式.

(3)进一步学习用示波器测量比较两路相关信号波形的周期、脉宽等参数的方法.

2.

实验原理双稳态触发器具有两个互补的输出端Q,Q—,触发器正常工作时,Q与Q—的逻辑电平总是互补,即一个为"0"时另一个一定是"1".

(当触发器工作在非正常状态时,Q和Q—的输出电平有可能相同,使用时必须注意避免出现这种情况).

RS触发器具有两个开关量特性的激励输入端R和S,R的有效电平使触发器复位(Reset),Q="0";S的有效电平使触发器置位(Set),Q="1",所以称为Reset_Set触发器.

图4-1-1是两个与非门互相反馈组成的基本RS触发器电路.

当激励S为有效电平时,输出Q立即置位为"1",而激励R为有效电平时,输出Q复位为"0",两者都为无效电平时,输出保持原来的状态不变.

JK触发器具有两个激励输入端"J","K",其特性方程为:Qn+1=JQ—n+K—Qn.

在有效时钟脉冲触发时,输出可以实现"同步置位"、"同步复位"、"状态不变"、"状态变反"四种功能.

741LS12是下降沿触发有效的集成JK触发器,片上有两个JK触发器,引脚标号以15"1","2"区别,如图4-1-2(a)所示.

D触发器只有一个激励输入端"D",当触发脉冲有效时,D触发器的输出与激励输入相同,由于在时间上滞后于输入,所以又称Delay触发器.

74LS74是上升沿触发有效的双D集成触发器,片上有两个D触发器,引脚排列如图4-1-2(b)所示.

集成触发器一般具有直接(direct)置位、复位控制端Sd、Rd,如图4-1-2中741LS12和74LS74引脚图所示.

当Rd或Sd有效时(为低电平"0"),触发器立即被复位或者置位.

所以,Rd、Sd又称异步复位、置位端.

直接置位、复位功能可以用来预置触发器的初始状态,但在使用时必须注意两者不允许同时有效,而且不允许与时钟触发控制同时有效.

T触发器也只有一个激励控制端"T",其特性方程为:Qn+1=TQ—n+T—Qn.

当触发条件满足时,若激励T="0",触发器的状态不变,当T="1",触发器的状态变反.

Tˊ触发器没有激励输入,只受触发时钟脉冲控制,其特性方程为:Qn+1=Q—n.

只要触发条件满足,Tˊ触发器状态的输出状态随触发脉冲CK输入连续翻转.

如果Tˊ触发器的初始状态为"0",奇数个触发脉冲输入后其状态为"1",偶数个触发脉冲输入后状态为"0",类似以一位二进制数累计触发脉冲输入的个数(进位溢出不计).

T触发器和Tˊ触发器一般没有专门的产品,可以用RS触发器、JK触发器或D触发器构成.

但是要注意所选触发器的时钟控制方式与所设计计数器的计数方式的匹配.

图4-1-3(a)中两个JK触发器构成了下降沿有效的Tˊ触发器(J=K="1"),状态方程为Qin+1=Q—in,具有的计数特性.

FF0的触发脉冲为CP,Q0在每个CP脉冲的下降沿时刻状态变反;FF1的时钟是FF0的输出Q—0,所以FF1在Q0上升沿(Q—0的下降沿)时刻状态变反.

Q0、Q1的输出波形如图4-1-3(b)所示.

由信号波形可见,在每个时钟脉冲下降沿后,Q1、Q0的状态码按"00"→"11"→"10"→"01"→"00"的规律循环变化,循环周期为四个时钟脉冲周期.

状态变化是以两位二进制码递减方式累计输入时钟脉冲的个数,电路功能为两位异步二进制计数器.

同时可以发现,Q0的信号周期是时钟周期的一倍,Q1的信号周期是时钟周期的两倍,fQ0=2cpf,fQ1=4cpf.

所以,该电路又具有分频的功能.

一般,用n个触发器可以构成n位异步二进制计数器.

除最低位触发器,其他各触发器的时钟都由相邻低位的状态输出控制.

可根据触发器的触发方式和所需的计数方式,按表4-1-1选择时钟连接方式.

16表4-1-1用Tˊ触发器构成n位异步二进制计数器的时钟控制关系计数器的计数方式上升沿触发的触发器下降沿触发的触发器加CPi=Q—i-1(i≥1)CPi=Qi-1(i≥1)减CPi=Qi-1(i≥1)CPi=Q—i-1(i≥1)3.

实验参考电路(1)与非门组成的基本RS触发器如图4-1-1(a)所示.

(2)集成触发器电路如图4-1-4所示.

(3)信号传输电路如图4-1-5所示.

(4)两位二进制加计数器如图4-1-3(a)所示.

4.

实验预习要求(1)复习基本RS触发器、JK触发器及D触发器的工作原理及特点.

(2)分析图4-1-1(a)基本RS触发器的输入是高电平有效还是低电平有效.

(3)列出图4-1-4中各触发器的状态方程,考虑D触发器和JK触发器各转换成了什么触发器(T触发器还是Tˊ触发器).

分析C、Q1、Q2的波形.

(4)分析图4-1-5电路中A、B、C的逻辑关系.

(5)若图4-1-3中触发器FF1的时钟由FF0的输出Q0直接控制,分析状态码Q1,Q0如何变化具有怎样的计数特性(6)用74LS74集成双D触发器设计一个两位二进制异步加计数器,实现图4-1-3电路的功能.

175.

实验内容及步骤(1)基本RS触发器功能测试用与非门74LS00组成如图4-1-1所示的基本RS触发器.

按表4-1-2测试其逻辑功能.

完成后保留电路.

最后两项反复操作几遍,看R、S同时从"1"变为"0"后,Q状态是否一致.

(2)集成JK触发器功能测试①观察集成触发器的置位、复位功能.

根据图4-1-2中JK触发器74LS112的引脚图,选择一个触发器.

直接置位Sd、复位表4-1-2与非门组成的基本R-S触发器的逻辑功能测试RSQ0Q—0功能011110110011输入Rd接逻辑开关.

按表4-1-3控制Rd,Sd,记录触发器的输出状态.

最后两项反复操作几遍,看Rd,Sd同时从"1"变为"0"后,输出Q是否为同一状态.

表4-1-3集成J-K触发器的直接置位、复位功能测试RdSdQQ—功能011110110011②触发器的激励输入J,K也接逻辑开关,时钟输入CP由实验步骤(1)中基本RS触发器的输出Q0控制.

先直接复位J-K触发器,然后Rd、Sd都置"1".

按表4-1-4控制其J、K和CP信号,记录JK触发器的输出状态.

其中CP的上升沿↑是指Q0原来的状态为"0",控制基本RS触发器置位端S使Q0变"1".

同理,CP信号的下降沿↓是指Q0从"1"变为"0".

用逻辑指示灯观察CP信号的变化以便记录.

表4-1-4集成J-K触发器的激励功能测试J1100001111K0000111111CP18QQ—③J,K端置"1",Rd或Sd端置"0",观察CP能否影响触发器的输出状态.

④J,K,Rd,Sd都置"1",触发器的CP直接由逻辑开关控制,观察开关从"1"变为"0"时触发器的状态能否正常翻转.

(3)集成触发器应用按图4-1-4电路和图4-1-2的器件引脚排列图接线.

电路的时钟C输入1kHz脉冲波,用示波器同步观察C,Q1,Q2的波形,注意时钟信号和各波形的时序对应关系.

记录波形时先观察C与Q1,然后对照Q1记录Q2.

(4)信号传输中的竞争冒险现象观察①按图4-1-5连接与非门电路.

用示波器同步观察并记录A、B、C三点波形.

②把C点输出的波形作为图4-1-4电路的时钟输入信号,观察能否触发电路.

如果短接E、B两点,电路能否触发*(5)按预习要求(5)改接图4-1-3电路,CP输入10kHz时钟脉冲.

观察并记录输出波形,测试各信号周期.

实验完毕保留电路.

*(6)连接预习要求(6)设计的电路,并将实验内容(5)电路中FF1的输出Q1作为本电路的输入时钟CP.

记录各输出信号波形并测试信号周期.

6.

实验设备和器材(1)数字逻辑实验箱1台(2)双列直插集成四-2输入TTL与非门74LS001片(3)双列直插集成TTL双J-K触发器74LS1121片(4)双列直插集成TTL双D触发器74LS741片(5)双踪示波器1台7.

实验思考题(1)根据实验步骤2(4)的结果说明触发器受时钟控制时,直接置位、复位端应该是什么状态(2)为什么实验步骤2不用逻辑开关而用基本R-S触发器的输出作为JK触发器的时钟CK信号如果用逻辑开关产生CK的上升沿或下降沿,可能会出现什么问题(3)图4-1-1(b)电路中,逻辑上A与B反相,C=AB——始终为逻辑"0",为什么触发器会得到触发脉冲触发翻转(4)根据实验内容(6)的结果,4位二进制计数器的状态以多少个时钟周期循环对时钟脉冲的分频率是多少以此类推,8位二进制计数器的分频率为多少(5)如何用74LS74设计两位二进制异步减计数器.

画出电原理图.

8.

实验报告要求(1)完成预习要求.

(2)完成实验内容中的记录要求,描绘实验波形图.

(3)分析实验内容(5)、(6)各输出信号对时钟的分频率.

(4)回答思考题.

196.

任意进制分频器实验1.

实验目的(1)掌握任意进制分频器的设计方法.

(2)掌握同步计数器74LS161多级级联的方法.

(3)研究不同连接方式时对分频数的影响.

2.

实验原理分频器和计数器是数字电路和自动控制电路中极重要的一种单元电路,分频器由最高位输出分频模数,计数器由其内部各级触发器输出不同的计数模数.

随着中规模电路的出现,分频器的设计方法,主要是合理灵活应用计数器芯片,实现任意进制分频.

74LS161是一种四位二进制可预置的同步加法计数器,图4-4-1是其引脚图,表4-4-1是其功能表.

图4-4-174LS161-163引脚图图4-4-27分频电原理图表4-4-174LS161功能表输入输出CRCPLDEPETD3D2D1D0Q3Q2Q1Q00ФФФФФФФФ00001↑0ФФdcbadcba1↑10ФФФФФQ3Q2Q1Q01↑1Ф0ФФФФQ3Q2Q1Q01↑111ФФФФ状态码加1从功能表中可知,当清零端CR="0",计数器输出Q3、Q2、Q1、Q0立即为全"0",为异步复位功能.

当CR="1"且LD="0"时,在CP脉冲上升沿作用后,74LS161的输出端Q3、Q2、Q1、Q0的状态分别与并行数据输入端D3,D2,D1,D0的状态相同,为同步置数功能.

而当CR=LD="1"、EP、ET中有一个为"0"时,计数器不计数,输出端状态保持不变.

只有当CR=LD=EP=ET="1"、CP脉冲上升沿作用后,计数器加1.

此外74LS161还有一个进位输出端CO,其逻辑关系是CO=Q3Q2Q1Q0ET.

(注:A对应D0,QA对应Q0.

)20合理应用计数器的清零功能和置数功能,一片74LS161可以构成16以下的任意进制分频器.

(1)用异步清零功能设计16以下任意进制分频器图4-4-2是构成7分频的电原理图.

图中每个时钟(CP)脉冲作用后,74LS161就加"1",当Q2=Q1=Q0="1"时,74LS20输入全"1"、输出为"0".

计数器立即复位并重新开始计数.

74LS161输出端随时钟脉冲输入的变化规律列于表4-4-2.

每输入7个时钟脉冲,复位控制与非门的输出端就有一个很窄的负脉冲,脉冲的宽度约为2tpd时间.

同理可列表4-4-3,表示不同分频数时复位控制与非门输入端和74LS161输出端的连接规律,四输入与非门的多余输入端接高电平.

异步复位时在Q3、Q2、Q1、Q0输出端上可能会出现不应有的毛刺信号.

表4-4-2图7分频电路中各触发器的输出状态CPQ3Q2Q1Q00000010001200103001140100501016011070111表4-4-3与非门输入端与分频数的关系表分频数3456789101112131415A11111Q3Q3Q3Q3Q3Q3Q3Q3B1Q2Q2Q2Q21111Q2Q2Q2Q2CQ111Q1Q111Q1Q111Q1Q1四与非门输入DQ01Q01Q01Q01Q01Q01Q0(2)利用同步置数法实现16位以下的任意进制分频图4-4-3是由74LS161和74LS04组成的9分频器,利用进位信号CO反相后产生预置数控制信号.

在CP脉冲作用后,74LS161就加1.

当Q3=Q2=Q1=Q0=ET="1"时,进位端CO输出为"1",反相后使74LS161的置位控制端LD有效,计数器进入置数准备状态.

当下一个时钟脉冲上升沿到达时,数据输入端D3、D2、D1、D0的数据被置入内部触发器,完成置数功能.

LD端的脉冲频率为计数时钟的9分频,负脉冲宽度为一个时钟周期.

利用进位信号CO同步置数的电路分频数N为N=D3*23+D2*22+D1*21+D0*20+1(4-4-1)式中D3、D2、D1、D0接地时为"0",否则为"1".

例如图4.

4.

3中,D3="0",D2=D1=D0="1",代入4-4-1式中可得分频数为21N=0*23+1*22+1*21十1*20+1=9表4-4-4列出了图4-4-3在每个时钟脉冲CP作用下Q3,Q2,Q1,Q0和CO的输出的状态.

图4-4-39分频电原理图表4-4-4图4-4-3中74LS161的输出状态表CPQ3Q2Q1Q0CO001110110000210010310100410110511000611010711100811111901110(3)255以下分频器当分频数要求在17~256之间时,可以采用两片4位二进制(模16)的加计数器74161级联.

级联后计数器的模相乘,分频数为256.

然后可以采用反馈复位或反馈置数方法减少分频数,但要注意级联后的计数器成为一个整体,复位控制或预置控制必须对两片同时作用.

二进制加计数器的级连原则是:当低位计数器从最大编码值状态复位为全"0"状态(溢出)时产生进位,使高位计数器加1.

进位方式分异步和同步两种:①异步进位方式——低位计数器的进位信号控制高位计数器的计数脉冲输入端.

同异步二进制计数器的设计方式类似,根据计数器的时钟触发方式,在低位计数器状态码从最大值复"0"瞬间,选择合适的输出为高位计数器提供有效的计数脉冲边沿.

如果计数器本身有进位输出信号,可利用进位信号的后沿使高位计数器加1.

要注意进位信号有效沿与计数器触发方式的匹配.

②同步进位方式——低位计数器的进位信号控制高位计数器的使能.

只有当低位计数器溢出前(最大有效状态码时),高位计数器的使能才有效,下一个计数脉冲使低位计数器复位同时使高位计数器加1.

所以同步进位方式只适用于具有使能控制的集成计数器.

同样要注意进位信号有效电平与计数器使能有效电平的匹配.

22(a)(b)图4-4-418分频原理图和波形图表4-4-518分频电路中各输出端的状态#274LS161#174LS161CPCO1Q3Q2Q1Q0LDCO2Q3Q2Q1Q0LD↑011101011101↑011101111111↑011111000001↑011111000011↑011111000101↑011111000111↑011111001001↑011111001011↑011111001101↑011111001111↑011111010001↑011111010011↑011111010101↑011111010111↑011111011001↑01111101101123↑011111011101↑111110111110↑011101011101图4-4-4(a)中两片计数器74LS161采用了同步进位方式,#174LS161的进位输出Co控制#274LS161的使能ET.

仅当#174LS161状态计到全"1"时,其进位CO1=Q3.

Q2.

Q1.

Q0.

ET="1",才能使#274LS161的使能有效加1.

即#1计数器每16个脉冲状态循环一次,使#2计数器加1.

所以,两片74161级联后构成模为16*16=256的计数器电路.

若根据二进制位权标注各输出位序,#174LS161的输出为Q3、Q2、Q1、Q0,#274LS161的输出为Q7、Q6、Q5、Q4.

由式4-4-1可知,利用计数器进位信号Co实现同步反馈置数的分频率计算式为:N=D—7*27+D—6*26+D—5*25+D—4*24+D—3*23+D—2*22+D—1*21+D—0*20+1(4.

4.

2)其中D7~D4是#274LS161的预置数,D3~D0是#174LS161的预置数.

改变两片74LS161置数端的状态D7~D0可很方便地改变分频数.

根据图4-4-4(a)电路,其预置数D7~D0="11101110",代入4-4-2,得分频数为N=20+24+1=18图4-4-4(a)电路的工作和预置数过程列于表4-4-5,两片74LS161的CO波形如图4-4-4(b)所示.

3.

实验预习要求(1)复习并掌握任意进制分频器的工作原理.

(2)熟悉74LS161的引脚,正确理解74LS161的真值表.

(3)按实验内容分别设计好电路原理图,并绘制好实验记录所需要的表格.

4.

实验内容及步骤(1)利用74LS161的清零端CR设计一个12分频器.

当时钟频率为1Hz时,用发光二极管显示74LS161Q3~Q0的输出状态,并填入表4-4-6中.

表4-4-612分频电路74LS161输出端状态利用CR端利用LD端时钟Q3Q2Q1Q0CRQ3Q2Q1Q0Co1234567891011241213(2)利用74LS161的置数端LD设计一个12分频器.

当时钟频率为1Hz时,用发光二极管显示74LS161Q3~Q0的输出状态,并填入表4-4-6中.

(3)用两片74LS161和74LS00设计23或33分频器,输入时钟频率为10kHz时,观察并记录CP脉冲、CO1和CO2的波形.

(4)当分频器为23时,把#274LS161的EP和ET对调,观察并记录CP脉冲、CO1和CO2的波形.

5.

实验设备和器材(1)双踪示波器1台(2)数字逻辑实验箱1台(3)TTL集成器件(74LS161、74LS00)2片、1片6.

实验思考题(1)试设计一个分频数为350的分频器电路,画出电原理图.

(2)用74LS161设计一个模24的计数器.

(3)试解释实验时记录在表4-4-6中CR和CO的状态.

7.

实验报告要求(1)按实验要求检查结果,记录波形,填好表格.

(2)分析用74LS161实现12分频的两种电路的特点,试讨论适用范围.

(3)理论分析实验内容的结果.

257.

集成移位寄存器应用实验1.

实验要求和目的(1)了解集成移位寄存器的控制功能.

(2)掌握集成移位寄存器的应用.

2.

实验原理移位寄存器的功能是:当时钟控制脉冲有效时,寄存器中存储的数码同时顺序向高位(左移)或向低位(右移)移动一位.

所以,移位寄存器的各触发器状态必须同时变化,为同步时序电路.

移位寄存器数据可以按序逐位从最低位或最高位串行输入寄存器,也可以通过置数端并行输入寄存器.

所以移位寄存器的数据输入、输出方式有:并行输入/并行输出、并行输入/串行输出、串行输入/并行输出、串行输入/串行输出.

移位寄存器主要应用于实现数据传输方式的转换(串行到并行或并行到串行)、脉冲分配、序列信号产生以及时序电路的周期性循环控制(计数器).

四位移位寄存器74LS194的逻辑功能如表4-5-1所示.

在方式信号S1,S0控制下,74LS194可以实现左移(串行数据从DSL输入)、右移(串行数据从DSH输入)、置数(并行数据从D3~D0输入)及保持(输出不变)功能.

表4-5-1四位移位寄存器74194功能表输入输出功能CRS1S0DSHDSLCKD3D2D1D0Q3Q2Q1Q00φφφφφφ0000异步复位111φφ↑ABCDABCD同步置数110Diφ↑φDiQ3Q2Q1右移101φDi↑φQ2Q1Q0Di左移100φφ↑φQ3Q2Q1Q0保持图4-5-1为简易乒乓球游戏机电路.

输入R,L为球拍击球信号,高电平有效,输出Q3-Q0接四个发光二极管指示乒乓球的运动轨迹.

游戏规则:R或L输入一个正脉冲发球,发光二极管指示球向对方移动,到达对方顶端位置时,对方必须及时接球,使球返回,否则就会失球.

输入的移位脉冲频率越高,球的移动轨迹越快,接球难度越大.

3.

实验参考电路(1)乒乓球游戏机电路原理如图4-5-1所示.

(2)移存型计数器如图4-5-2所示.

4.

实验预习要求(1)分析图4-5-1中两个或非门组成什么功能的逻辑电路说明整个电路的工作原理.

(2)如果希望球的运动轨迹用八个发光二极管指示,怎样改进电路(3)分析图4-5-2电路的状态转换关系、任一输出信号的序列和自启动能力.

(4)用两片74LS194设计一个串行数据传输电路,发送方将并行输入的四位二进制数据转换成串行数据输出,接收方将串行输入的数据转换成并行数据输出,信号传输位序任意选择.

画出电原理图.

(5)用741LS94设计一个四位环形计数器,移位方向任意,可预置初值"0001",画出电原理图.

26(6)用74LS194设计一个四位扭环形计数器,移位方向任意,具有复位控制功能,画出电原理图.

5.

实验内容与步骤(1)乒乓球游戏电路实验①连接图4-5-1电路或非门部分,R,L端接逻辑开关,Q,Q—端接发光二极管.

测试并记录电路的逻辑功能.

②连接4-5-1电路移位寄存器部分,观察游戏效果.

注意:发球或接球动作是给予R或L一个正脉冲,即逻辑开关置"1"后必须复"0",动作必须准确,置"1"的时间过短发不出球或接不住球;置"1"的时间过长,指示球轨迹的发光二极管可能不是一个而是多个,影响游戏效果.

(2)移存型计数器连接4-5-2电路.

电路复位后输入1Hz时钟,观察电路输出状态是否与理论分析相同.

时钟脉冲改为10kHz,用示波器记录Q3和Q2的输出信号波形.

(3)串行信号传输连接串行信号传输电路.

发送方和移位接收方的寄存器分放在两组实验装置上.

发送方的四位并行数据输入由逻辑开关控制,设置值任意.

接收方的四位并行输出接发光二极管.

移位脉冲CP由发送方装置的逻辑脉冲按钮提供,观察数据的串行传输过程.

(4)74LS194构成的四位环形计数器①连接电路,输出接发光二极管,时钟接1Hz脉冲,预置控制端接逻辑开关.

②先预置初值"0001",然后设置移位工作方式,观察实验效果,记录状态转换图.

③时钟脉冲频率改为1kHz,用示波器分别观察四个输出信号的周期及相位关系,画出波形图.

(5)四位扭环形计数器连接电路,输出接发光二极管,时钟接1Hz脉冲,观察实验效果,记录状态转换图.

6.

实验设备与器材(1)数字逻辑实验箱1台(2)集成四-2输入或非门74LS021片(3)集成四异或门74LS861片(4)集成四位移位寄存器74LS1942片277.

实验思考题(1)图4-5-1电路的缺陷是:如果球未到达对方顶端位置,对方击球,球也会返回.

思考能否增加一个发球输入信号改进电路,弥补此缺陷.

(2)如何修改图4-5-2电路使之具有自启动能力8.

实验报告要求(1)完成预习内容要求设计的电原理图.

(2)实验结果处理.

(3)写出图4-5-2电路的输出序列(4)回答思考题.

字符编码显示电路实验1.

实验目的(1)掌握组合电路逻辑功能的测试方法.

(2)掌握TTL逻辑门组合应用和七段显示器使用方法.

(3)了解组合逻辑电路的设计方法.

2.

实验原理组合逻辑电路的输出状态完全取决于同一时刻输入状态的组合,与电路原来的输出状态无关.

图3-2-5是一个由逻辑门构成编码显示组合电路,可以分析,6个输出Ya,Yb,Yc,Yd,Ye,Yg与两个输入K1,K0有一一对应的逻辑关系.

两个输入组合成四种编码输出状态,控制七段显示器显示四个特定字符.

(1)七段共阴显示器原理七段显示器内部由八个发光二极管组成,七个段划和一个小数点,位置排成"—.

"形.

八个发光二极管的连接方式有共阴接法和共阳接法两种.

共阳接法就是把所有发光二极管的阳极都接在一起,形成一个由高电平驱动的公共端COM,各管的阴极由低电平有效的段码信号a~g控制.

共阴接法则相反,它的公共端COM是所有发光二极管的阴极,由低电平驱动,而各段发光二极管的阳极由高电平驱动.

图3-2-1表示了七段共阴显示器的内部原理、外引线排列图以及常用显示符.

各段发光二极管正向导通时发光,导通电压UD约为2V,导通电流ID约需3-10毫安,电流太大可能会损坏器件.

所以,使用时必须根据所加信号的幅度选择限流电阻.

图3-2-5中,七段共阴显示器的公共端COM接地,段控制端a~g通过限流电阻接5V电源.

由于TTL逻辑门输出的高电平驱动能力有限,所以或非门输出通过反相缓冲器1413(2003)驱动显示器的a,b,c,d,e,g各段.

其中f直接通过限流电阻接电源,不受输入K1,K0控制,所以f段始终发光.

(2)集电极开路的反相缓冲器功能1413(2003)为集电极开路(OpenCollector)反相达林顿结构,内部有7个互相独立的复合达林顿管.

电路原理及引脚排列如图3-2-2(a)所示.

当缓冲器输入为低电平"0"时,复合管截止,OC输出为高阻状态,对外电路没有影响,相应段的发光管仍然导通;当缓冲器输入为高电平"1"时复合管导通,输出低电平使相应段的发光管截止.

所以当图3-2-5电路中或非门输出为"0"时,显示段亮,输出为"1"时,显示段灭.

2(3)动态扫描显示原理图3-2-5电路中采用一个显示器根据K0,K1控制显示不同的字符.

如果K0,K1由一个2位二进制计数器的输出控制,使K0,K1的状态呈"00"→"01"→"10"→"11"→"00"自动顺序变化,则四个字符亦随控制码顺序循环显示.

如果采用四个共阴显示器组成如图3-2-3所示的动态扫描显示电路,替代图3-2-5中的一个七段显示器,则四个显示字符可以同时稳定显示.

四个显示器的阳极a~g一一对应连接,由缓冲器的输出控制.

各显示器的阴极公共端信号Y0~Y3由K0,K1通过2线-4线通用译码器顺序产生,扫描控制时序如图3-2-4所示.

由于任意瞬时只有一个共阴显示器的阴极为低电平,所以此时反相缓冲器输出的阳极控制信号只能对该显示器有效,使之显示相应的字符,其他阴极为高电平的显示器呈灭显状态.

这样,扫描时钟信号CP控制计数器使各显示器分时轮流选通,同时控制逻辑门编码电路产生不同的字符显示段信号,使各显示器逐位顺序显示.

每位显示的时间为一个CP周期,显示扫描周期T为时钟周期的4倍.

只要扫描时钟频率足够高,使每个显示器每秒的导通次数大于50次(四位显示的扫描时钟频率大于200Hz),由于人眼的视觉暂留效应,可以观察到各位显示器同时显示.

时钟频率越高,显示越稳定.

33.

实验参考电路4.

实验预习要求(1)根据图3-2-5,列出电路各输出端的逻辑表达式,并将输入K1,K0为不同状态时,逻辑门电路的输出Ya,Yb,Yc,Yd,Ye,Yg和七段共阴显示器输入a~g及相应的显示字符填入表3-2-1中.

(2)用2输入与非门设计显示自选字符,如"H","O","P","E"("H","E","L","P"或"C","L","E","A"等).

列出真值表,写各输出的逻辑表达式,画出电原理图,标出引脚编号.

逻辑门的个数不能超过8个.

逻辑门采用四-2输入与非门74LS00,引脚排列见实验4.

1图4-1-2(c)(3)根据发光二极管发光时的导通电压和导通电流选择限流电阻的阻值.

*(4)根据动态扫描原理设计电路,画出电路原理图.

其中2位二进制计数器用双JK触发器构成,型号从附录中自选.

双2线-4线译码器的型号为74LS139,功能及引脚排列查阅实验3.

5图3-5-1.

(5)认真阅读实验内容与步骤部分,充分了解实验方法和过程.

表3-2-1图3-2-5电路输入、输出逻辑关系K1K0YaYbYcYdYeYgabcdefg显示字符00亮01亮10亮11亮5.

实验内容和步骤(1)检查实验装置与器件.

根据四-2输入或非门74LS02的逻辑功能检查器件.

或非门的输入信号由数字逻辑实验箱上的逻辑开关提供,输出状态用箱上的逻辑指示灯检查.

当任一开关的状态为高电平"1"时,或非门输出低电平"0",指示灯不亮.

当两个开关的状态均为低电平"0"时,或非门输出高电平"1",指示灯亮.

4(2)按图3-2-5电路连线,输入K1、K0接逻辑开关.

限流电阻采用8联集成电阻,9个引脚,内部连接方式如图3-2-5虚线框所示.

8联电阻的公共端有标记"",接+5V电源.

集成电阻直接插在反相缓冲器的输出引脚边,如图3-2-2所示,以减少连线.

缓冲器输出a~g接共阴显示器的段码输入端,显示器公共端COM接地.

根据表3-2-1改变开关状态,观察显示字符是否与分析的结果相同.

(3)按预习要求(2)设计的电路改接编码组合电路部分(缓冲器和显示器电路不变),观察显示结果并与设计要求比较.

*(4)用JK触发器连接成两位二进制异步计数器,控制编码显示电路的输入K1,K0,扫描时钟采用逻辑实验仪输出的1Hz脉冲信号,观察显示效果.

*(5)按预习内容(4)设计的电路连接动态扫描显示电路,扫描时钟频率改为1kHz,观察实验结果.

6.

实验设备和器材(1)数字逻辑实验箱1台(2)双列直插集成四-2输入TTL或非门74LS022片(3)双列直插集成四-2输入TTL与非门74LS001片(4)七段共阴显示器1个(5)九引脚8联集成电阻1个(6)集成七达林顿OC反相缓冲器1413(2003)1片*(7)双JK触发器1片*(8)2线-4线译码器74LS1391片(9)数字万用表1台7.

实验思考题(1)若限流电阻为1KΩ,当反相缓冲器输入Yb为"1"时,输出信号电平约为0.

3V左右.

根据发光二极管的导通电压和电流,图3-2-5电路中的I,ID,Io各为多少当Yb为"0"时,各电流又为多少(2)若动态扫描显示电路的时钟频率为1Hz,四位字符可能如何显示如果时钟频率为100Hz呢8.

实验报告要求(1)预习要求(1),(2)的内容.

(2)列出限流电阻参数选择的计算方法.

(3)回答思考题.

52.

编码器和译码器实验1.

实验目的(1)掌握中规模集成电路译码器、编码器的逻辑功能和使用方法.

(2)利用译码器、编码器进行组合逻辑电路设计.

2.

实验原理(1)编码器编码器的逻辑功能是将输入信号中的一个有效信号变换成相应的一组二进制代码输出.

优先编码器定义了所有输入信号的优先级别.

当多个输入信号同时有效时,优先编码器输出的是对应优先权最高的信号编码值.

图3–3–18线-3线优先编码器74LS148的引脚排列图图3–3–1给出8线-3线优先编码器74LS148的引脚排列图.

S为使能控制端或称选通输入端.

选通输出端YS和扩展端YEX的功能是实现编码位数(输入信号数)的扩展.

0IN~7IN是8个输入信号(编码对象),低电平有效.

7IN的优先权最高,0IN的优先权最低.

编码输出是3位二进制代码,用012YYY表示.

表3–3–1为8线-3线优先编码器的真值表.

表3–3–18线-3线优先编码器真值表输入输出S0IN1IN2IN3IN4IN5IN6IN7IN2Y1Y0YEXYSYlΦΦΦΦΦΦΦΦ0111111110ΦΦΦΦΦΦΦ00ΦΦΦΦΦΦ01OΦΦΦΦΦ0110ΦΦΦΦ01110ΦΦΦ0ll110ΦΦ0l11110*0111111001ll1111111111111000001001010100l011011000l101011100111101在S="0"时,编码器允许工作.

当70~ININ8个输入中有"0"时,输出一组优先6权最高的有效输入所对应的二进制代码.

比如当S="0"6431ININININ时,IN———6的优先权最高,输出2Y1Y0Y="001"(见表3-3-1第4行).

(2)译码器译码是编码的逆过程,它的逻辑功能是将每个输入的二进制代码,译成对应输出的高、低电平信号.

译码器有变量译码器和显示译码器之分.

①变量译码器变量译码器的逻辑功能是将输入的n位二进制代码译成2n个输出变量.

每个输出变量与唯一的一组输入码对应,当输入为某组码时,仅有与其对应的输出信号为有效电平,其他输出均为无效电平.

典型的变量译码器型号为3线-8线译码器74LS138.

图3–3–2所示为3线-8线译码器74LS138的引脚排列图.

图3–3–23线-8线译码器74LS138的引脚排列图.

其中012AAA为3条译码输入端,0Y~7Y为8条译码输出端,低电平有效.

1S,2S,3S为使能选通端.

表3–3–2所示为3线-8线译码器74LS138的真值表.

表3–3–23线-8线译码器真值表1S32SS2A1A0A0Y1Y2Y3Y4Y5Y6Y7Yφlφφφ0φφφφ1O0O0100011O01010011101001O101101101011111111111111111110111111110111111110111111110111111110111111110111111110111111110由表3–3–2可见,当1S="1",32SS="0"时,不论输入2A、1A、0A为何状态,输出0Y~7Y中有且仅有一个为有效电平"0",有效输出端的下标序号与输入二进制码所对应的十进制数相同.

变量译码器除了实现译码功能外,可以作为数据分配器使用.

如果利用使能选通端中的7一个输入串行数据信号,变量译码器就实现数据分配功能.

另外,变量译码器还可以用来方便地实现多输出逻辑函数.

②显示译码器把输入的二—十进制代码转换成十进制数码各段驱动信号的电路称为显示译码器.

图3–3–3为七段显示译码器74LS48的引脚排列图.

图3–3–3七段显示译码器74LS48引脚排列图其中03~AA为译码器的输入信号,gaYY~为译码器的7个输出,LT为译码器的灯测试输入,RBOBI/为译码器的消隐输入/灭零输出,RBI为灭零输入.

表3–3–3为七段显示译码器的真值表.

表3–3–3七段显示译码器的真值表十进制输入RBOBI输出或功能LTRBI3A2A1A0AaYbYcYdYeYfYgYOl23456789101112131415ll11111l1lll1ll11φφφφφφφφφφφφφφφ00000001001000110100010101100111100010011010l01111001101l110llll1l1lllll111l1l111l11l1001lO000110110lllll00l0ll00ll10l10ll00111111110000llllllll1l00ll000110100110010100011l0010llO00111100000008消隐脉冲消隐灯测试φ10φ0φφφφφ0000φφφφ00l00000000000000ll1lll1根据表3–3–3七段显示译码器74LS48的真值表,简单介绍三个功能端LT,RBOBI/和RBI的工作情况.

灯测试输入:当0LT且1BI时,无论03~AA状态如何,输出Ya~Yg全部为高电平,都可使被驱动数码管的七段同时点亮,以检查该数码管各段能否正常发光.

利用这个功能可以判断显示器的好坏.

消隐输入:也称灭灯输入.

BI为消隐输入,当BI=0时,无论RBILT,及输入03~AA为何值,所有各段输出gaYY~均为低电平,显示器处于熄灭状态.

RBO为灭零输出.

灭零输入:RBI可以按数据显示需要,将显示器所显示的0予以熄灭,而在显示1-9时不受影响.

它在实际应用中是用来熄灭多位数字前后不必要的零位,使显示的结果更醒目.

将灭零输入端与灭零输出端配合使用,很容易实现多位数码显示系统的灭零控制.

在数字系统中,经常需要将被测量或数值运算结果用十进制数码显示出来.

由于显示器件和显示方式不同,在各类显示器件中,目前使用最为广泛的是由发光二极管构成的七段显示数码管.

将七个发光二极管按一定的方式连接在一起,就构成七段显示数码管.

它有共阳极和共阴极两种连接方式,如图3–3–4所示.

(a)(b)(c)图3–3–4七段显示数码管结构(a)七段显示器(b)共阴极连接(c)共阳极连接本实验采用的型号为BS201共阴极式显示器,它与74LS48译码器配套使用.

3.

实验预习要求(1)复习有关编码器和译码器的原理.

(2)了解所用集成电路的功能和外部引线排列.

(3)根据实验任务,画出所需的实验电路图及记录表格4.

实验内容和步骤9(1)按上图接线,D0~D3接数字电路实验箱的电平按键开关,输出L1、L2接发光二极管,3位编码输出分别接内部带译码器的数码管1,2,4输入端,数码管端子8接地.

数电实验箱内部已经为这两个数码管设计连接了译码驱动电路,只要将四位二进制码接入就可显示16进制数0~F.

(2)D3接高电平,D2D1D0三位依次置入000~111,观察数码管显示.

记录此时的YEX和YS.

然后重新将D2D1D0三位置入011,将I6连接到Y6的导线74LS138输出端的一头拔出,改为接地,观察数码管显示.

将结果填入表3-19-4中.

(3)D3改接低电平,观察数码管显示,记录此时的YEX和YS.

将结果填入表3-19-4中.

5.

实验设备与器材(1)数字逻辑实验箱1台(2)双踪示波器1台(3)函数信号发生器1台(4)集成芯片:74LS148,74LS138,显示器若干6.

实验思考题(1)用一片74LS138和一片74LS20设计并实现一位全减器.

103.

数据选择器和数据分配器应用实验1.

实验目的(1)了解变量译码器和数据选择器的逻辑功能和具体应用.

(2)熟悉中规模组合逻辑器件功能的测试和设计方法.

2.

实验原理(1)变量译码器变量译码器有n个输入,2n个输出,每个输出唯一地对应一组输入构成的二进制码,当且仅当输入组合为该码时,输出呈有效电平.

中规模TTL集成译码器有74LS139(双2输入、4输出)、74LS138(3输入、8输出)和74LS154(4输入、16输出),输出均为低电平有效,并具有低电平有效的使能控制端S—-.

变量译码器除在数字系统中起二进制译码作用外,还可实现组合逻辑函数、数据分配等功能.

74LS139的引脚图如图3-5-1(a)所示,片上有两个独立的2线-4线译码器,各输出逻辑表达式为:Y——0=01AAS、Y——1=01AAS、Y——2=01AAS、Y——3=01AAS显然,当使能S—-为有效电平"0"时,如果译码器A1,A0输入的是逻辑函数的输入变量A,B,则Y——i代表了A,B构成的最小项mi的反函数(最大项).

所以,2线-4线通用译码器可附加与非门(与门)实现用标准与-或(标准或-与)表达式表示的二变量组合逻辑函数.

同理,n线-2n线通用译码器可实现n变量的组合逻辑函数.

如果把译码器的使能端S作为数据输入端,则可实现数据分配功能.

被分配的串行数字信号Di从S输入,当A1,A0为不同的二进制码时,Di信号被分配到译码器对应的输出端Y——i.

比如A1A0为"11"时,Di信号被分配到Y——3,此时Y——0~Y——2输出均为高电平.

(2)数据选择器数据选择器有n位控制信号,2n个数据输入.

每组控制码能够选择唯一的一个数据输出,类似由控制码切换的多选一开关.

中规模TTL集成数据选择器有74LS153(双4选1)和74LS151(8选1),都具有低电平有效的使能控制端S.

数据选择器的主要功能是实现多路11信号的选择,当控制端输入函数的逻辑变量、数据端输入函数值时,可以实现组合逻辑函数.

74LS153的引脚功能如图3-5-1(b)所示,片上有两个4选1数据选择器,控制端A1,A0共用.

输出逻辑表达式为:Y=S—-(A—1A—0D0+A—1A0D1+A1A—0D2+A1A0D3)图3-5-2为一个报警控制电路,其中数据选择器选择两个不同频率的信号控制音频蜂鸣器.

音频蜂鸣器的有效信号频率在20Hz~2kHz音频范围内,频率不同音调不同.

声音的强弱与音频蜂鸣器的驱动电流成正比.

由于TTL电路的驱动能力有限,为提高音量,采用NPN三极管9013进行电流放大.

三极管工作在开关状态,当数据选择器输出E为"0"时,三极管截止,蜂鸣器没有电流通过;当E为"1"时,三极管饱和,Uce约为0.

2V,蜂鸣器得电.

当E的信号切换频率在音频范围内时,蜂鸣器鸣响.

9013的引脚如图3-5-1(c)所示.

3.

实验参考电路(1)声光报警电路如图3-5-2所示.

(2)函数发生器如图3-5-3所示.

4.

实验预习要求(1)复习译码器、数据选择器及数据分配器的工作原理.

(2)分析图3-5-2电路的报警控制信号W的有效电平是高还是低报警时蜂鸣器的控制信号E是什么波形蜂鸣器的鸣叫声音可能是怎样的(3)根据图3-5-3列出电路输出CY和SUM的布尔表达式及真值表.

如果输入A,B,C是三个一位的二进制数,分析电路的逻辑功能.

(4)设计一个数据选择、分配电路,设计要求:①四个一位的输入数据D0,D1,D2,D3,用两个逻辑开关编码选择;②四个一位的输出数据Y0,Y1,Y2,Y3,另用两个逻辑开关编码选择;③功能:可以将四个输入数据中的任何一路信号Di选择并分配给四个输出中的任何一个Yi.

选择集成器件设计电路,画出电原理图,标明各集成器件的引脚编号.

(5)用74LS153设计一个一位二进制数的全减器.

输入三个一位的二进制数A,B,C,输出逻辑变量D和V.

其中D是A减B减C的差,V表示了A的值是否够被B,C减,够减时V="0",否则为"1".

列出真值表,画出电原理图.

(6)用74LS139和两个四输入与非门(或四输入与门)实现全减器,画出电原理图.

12(7)用4选1数据选择器74LS153和两位二进制计数器设计一个信号传输方式转换电路,把四位并行码D0~D3转换成一列串行信号.

要求转换位序可以根据需要选择先高位后低位或者相反.

画出设计的电路原理图.

5.

实验内容及步骤(1)译码器功能测试.

根据图3-5-1中74LS139的引脚图,任选其中一个2线-4线译码器测试其功能.

使能端S—-由1Hz脉冲信号控制,输入A1,A0由逻辑开关控制,四个输出Y0~Y3接逻辑指示灯(发光二极管).

改变输入A1,A0的状态,观察Y0~Y3的输出记录在表3-5-1中(记录输出状态是高电平、低电平或1Hz信号).

测试完成后保留电路.

表3-5-12线-4线通用译码器功能测试A1A0Y0Y1Y2Y300100111(2)4选1数据选择器功能测试根据图3-5-1中74LS153的引脚图,任选其中一个数据选择器测试其功能.

使能端S—-接有效电平(GND),四个数据端D0~D3分别输入1Hz,3Hz,10Hz和高电平(Vcc)信号.

其中1Hz,10Hz信号可取自逻辑实验箱上的脉冲信号区,3Hz信号由函数发生器TTL端输出.

用发光二极管观察数据选择器的输出端Y,改变输入A1,A0的状态,在表3-5-2中记录数据选择情况.

(记录输出信号频率或电平状态)表3-5-24选1数据选择器功能测试表输入A1A000011011输出Y(3)根据预习内容4设计的电路,在实验步骤(1),(2)的基础上连接数据选择、分配电路.

观察信号的选择分配情况.

(4)根据图3-5-2连接声光报警电路.

1Hz和1kHz脉冲信号都由逻辑实验箱提供,2kHz脉冲信号由函数发生器的TTL端输出.

报警信号W由逻辑开关控制,警灯L为逻辑指示灯.

改变W的状态,观察实验结果.

当W有效时,警笛鸣响,警灯L闪烁.

微调函数发生器频率,观察频率变化对蜂鸣器音调的影响.

(5)数据选择器构成的函数发生器根据图3-5-3连接电路.

输入A,B,C接逻辑开关,输出用逻辑指示发光二极管检查.

改变输入状态记录函数真值表,与预习时分析的结果比较.

(6)根据预习(5)设计的电路连线,观察实验结果是否满足设计要求.

(7)根据预习(6)设计的电路连线,观察实验结果是否满足设计要求.

(8)根据预习(7)设计的电路连线,观察实验结果是否满足设计要求.

136.

实验设备和器材(1)数字逻辑实验箱1台(2)函数发生器1台(3)双列直插集成TTL2线-4线译码器74LS1391片(4)双列直插集成TTL4选1数据选择器74LS1531片(5)双列直插集成TTL二-4输入与非门74LS201片(6)NPN三极管90131个7.

实验思考题(1)声光报警电路中,是否能用报警信号控制数据选择器的输入端A1为什么(2)如果实验内容(3)只用一组两位的二进制码同时控制数据的选择和分配,结果会如何8.

实验报告要求(1)预习内容要求.

(2)实验内容要求.

(3)回答思考题.

14时序电路应用实验4.

触发器基本功能测试实验1.

实验目的(1)学习触发器逻辑功能的测试方法.

(2)了解基本RS触发器、D触发器及JK触发器的逻辑功能及触发方式.

(3)进一步学习用示波器测量比较两路相关信号波形的周期、脉宽等参数的方法.

2.

实验原理双稳态触发器具有两个互补的输出端Q,Q—,触发器正常工作时,Q与Q—的逻辑电平总是互补,即一个为"0"时另一个一定是"1".

(当触发器工作在非正常状态时,Q和Q—的输出电平有可能相同,使用时必须注意避免出现这种情况).

RS触发器具有两个开关量特性的激励输入端R和S,R的有效电平使触发器复位(Reset),Q="0";S的有效电平使触发器置位(Set),Q="1",所以称为Reset_Set触发器.

图4-1-1是两个与非门互相反馈组成的基本RS触发器电路.

当激励S为有效电平时,输出Q立即置位为"1",而激励R为有效电平时,输出Q复位为"0",两者都为无效电平时,输出保持原来的状态不变.

JK触发器具有两个激励输入端"J","K",其特性方程为:Qn+1=JQ—n+K—Qn.

在有效时钟脉冲触发时,输出可以实现"同步置位"、"同步复位"、"状态不变"、"状态变反"四种功能.

741LS12是下降沿触发有效的集成JK触发器,片上有两个JK触发器,引脚标号以15"1","2"区别,如图4-1-2(a)所示.

D触发器只有一个激励输入端"D",当触发脉冲有效时,D触发器的输出与激励输入相同,由于在时间上滞后于输入,所以又称Delay触发器.

74LS74是上升沿触发有效的双D集成触发器,片上有两个D触发器,引脚排列如图4-1-2(b)所示.

集成触发器一般具有直接(direct)置位、复位控制端Sd、Rd,如图4-1-2中741LS12和74LS74引脚图所示.

当Rd或Sd有效时(为低电平"0"),触发器立即被复位或者置位.

所以,Rd、Sd又称异步复位、置位端.

直接置位、复位功能可以用来预置触发器的初始状态,但在使用时必须注意两者不允许同时有效,而且不允许与时钟触发控制同时有效.

T触发器也只有一个激励控制端"T",其特性方程为:Qn+1=TQ—n+T—Qn.

当触发条件满足时,若激励T="0",触发器的状态不变,当T="1",触发器的状态变反.

Tˊ触发器没有激励输入,只受触发时钟脉冲控制,其特性方程为:Qn+1=Q—n.

只要触发条件满足,Tˊ触发器状态的输出状态随触发脉冲CK输入连续翻转.

如果Tˊ触发器的初始状态为"0",奇数个触发脉冲输入后其状态为"1",偶数个触发脉冲输入后状态为"0",类似以一位二进制数累计触发脉冲输入的个数(进位溢出不计).

T触发器和Tˊ触发器一般没有专门的产品,可以用RS触发器、JK触发器或D触发器构成.

但是要注意所选触发器的时钟控制方式与所设计计数器的计数方式的匹配.

图4-1-3(a)中两个JK触发器构成了下降沿有效的Tˊ触发器(J=K="1"),状态方程为Qin+1=Q—in,具有的计数特性.

FF0的触发脉冲为CP,Q0在每个CP脉冲的下降沿时刻状态变反;FF1的时钟是FF0的输出Q—0,所以FF1在Q0上升沿(Q—0的下降沿)时刻状态变反.

Q0、Q1的输出波形如图4-1-3(b)所示.

由信号波形可见,在每个时钟脉冲下降沿后,Q1、Q0的状态码按"00"→"11"→"10"→"01"→"00"的规律循环变化,循环周期为四个时钟脉冲周期.

状态变化是以两位二进制码递减方式累计输入时钟脉冲的个数,电路功能为两位异步二进制计数器.

同时可以发现,Q0的信号周期是时钟周期的一倍,Q1的信号周期是时钟周期的两倍,fQ0=2cpf,fQ1=4cpf.

所以,该电路又具有分频的功能.

一般,用n个触发器可以构成n位异步二进制计数器.

除最低位触发器,其他各触发器的时钟都由相邻低位的状态输出控制.

可根据触发器的触发方式和所需的计数方式,按表4-1-1选择时钟连接方式.

16表4-1-1用Tˊ触发器构成n位异步二进制计数器的时钟控制关系计数器的计数方式上升沿触发的触发器下降沿触发的触发器加CPi=Q—i-1(i≥1)CPi=Qi-1(i≥1)减CPi=Qi-1(i≥1)CPi=Q—i-1(i≥1)3.

实验参考电路(1)与非门组成的基本RS触发器如图4-1-1(a)所示.

(2)集成触发器电路如图4-1-4所示.

(3)信号传输电路如图4-1-5所示.

(4)两位二进制加计数器如图4-1-3(a)所示.

4.

实验预习要求(1)复习基本RS触发器、JK触发器及D触发器的工作原理及特点.

(2)分析图4-1-1(a)基本RS触发器的输入是高电平有效还是低电平有效.

(3)列出图4-1-4中各触发器的状态方程,考虑D触发器和JK触发器各转换成了什么触发器(T触发器还是Tˊ触发器).

分析C、Q1、Q2的波形.

(4)分析图4-1-5电路中A、B、C的逻辑关系.

(5)若图4-1-3中触发器FF1的时钟由FF0的输出Q0直接控制,分析状态码Q1,Q0如何变化具有怎样的计数特性(6)用74LS74集成双D触发器设计一个两位二进制异步加计数器,实现图4-1-3电路的功能.

175.

实验内容及步骤(1)基本RS触发器功能测试用与非门74LS00组成如图4-1-1所示的基本RS触发器.

按表4-1-2测试其逻辑功能.

完成后保留电路.

最后两项反复操作几遍,看R、S同时从"1"变为"0"后,Q状态是否一致.

(2)集成JK触发器功能测试①观察集成触发器的置位、复位功能.

根据图4-1-2中JK触发器74LS112的引脚图,选择一个触发器.

直接置位Sd、复位表4-1-2与非门组成的基本R-S触发器的逻辑功能测试RSQ0Q—0功能011110110011输入Rd接逻辑开关.

按表4-1-3控制Rd,Sd,记录触发器的输出状态.

最后两项反复操作几遍,看Rd,Sd同时从"1"变为"0"后,输出Q是否为同一状态.

表4-1-3集成J-K触发器的直接置位、复位功能测试RdSdQQ—功能011110110011②触发器的激励输入J,K也接逻辑开关,时钟输入CP由实验步骤(1)中基本RS触发器的输出Q0控制.

先直接复位J-K触发器,然后Rd、Sd都置"1".

按表4-1-4控制其J、K和CP信号,记录JK触发器的输出状态.

其中CP的上升沿↑是指Q0原来的状态为"0",控制基本RS触发器置位端S使Q0变"1".

同理,CP信号的下降沿↓是指Q0从"1"变为"0".

用逻辑指示灯观察CP信号的变化以便记录.

表4-1-4集成J-K触发器的激励功能测试J1100001111K0000111111CP18QQ—③J,K端置"1",Rd或Sd端置"0",观察CP能否影响触发器的输出状态.

④J,K,Rd,Sd都置"1",触发器的CP直接由逻辑开关控制,观察开关从"1"变为"0"时触发器的状态能否正常翻转.

(3)集成触发器应用按图4-1-4电路和图4-1-2的器件引脚排列图接线.

电路的时钟C输入1kHz脉冲波,用示波器同步观察C,Q1,Q2的波形,注意时钟信号和各波形的时序对应关系.

记录波形时先观察C与Q1,然后对照Q1记录Q2.

(4)信号传输中的竞争冒险现象观察①按图4-1-5连接与非门电路.

用示波器同步观察并记录A、B、C三点波形.

②把C点输出的波形作为图4-1-4电路的时钟输入信号,观察能否触发电路.

如果短接E、B两点,电路能否触发*(5)按预习要求(5)改接图4-1-3电路,CP输入10kHz时钟脉冲.

观察并记录输出波形,测试各信号周期.

实验完毕保留电路.

*(6)连接预习要求(6)设计的电路,并将实验内容(5)电路中FF1的输出Q1作为本电路的输入时钟CP.

记录各输出信号波形并测试信号周期.

6.

实验设备和器材(1)数字逻辑实验箱1台(2)双列直插集成四-2输入TTL与非门74LS001片(3)双列直插集成TTL双J-K触发器74LS1121片(4)双列直插集成TTL双D触发器74LS741片(5)双踪示波器1台7.

实验思考题(1)根据实验步骤2(4)的结果说明触发器受时钟控制时,直接置位、复位端应该是什么状态(2)为什么实验步骤2不用逻辑开关而用基本R-S触发器的输出作为JK触发器的时钟CK信号如果用逻辑开关产生CK的上升沿或下降沿,可能会出现什么问题(3)图4-1-1(b)电路中,逻辑上A与B反相,C=AB——始终为逻辑"0",为什么触发器会得到触发脉冲触发翻转(4)根据实验内容(6)的结果,4位二进制计数器的状态以多少个时钟周期循环对时钟脉冲的分频率是多少以此类推,8位二进制计数器的分频率为多少(5)如何用74LS74设计两位二进制异步减计数器.

画出电原理图.

8.

实验报告要求(1)完成预习要求.

(2)完成实验内容中的记录要求,描绘实验波形图.

(3)分析实验内容(5)、(6)各输出信号对时钟的分频率.

(4)回答思考题.

196.

任意进制分频器实验1.

实验目的(1)掌握任意进制分频器的设计方法.

(2)掌握同步计数器74LS161多级级联的方法.

(3)研究不同连接方式时对分频数的影响.

2.

实验原理分频器和计数器是数字电路和自动控制电路中极重要的一种单元电路,分频器由最高位输出分频模数,计数器由其内部各级触发器输出不同的计数模数.

随着中规模电路的出现,分频器的设计方法,主要是合理灵活应用计数器芯片,实现任意进制分频.

74LS161是一种四位二进制可预置的同步加法计数器,图4-4-1是其引脚图,表4-4-1是其功能表.

图4-4-174LS161-163引脚图图4-4-27分频电原理图表4-4-174LS161功能表输入输出CRCPLDEPETD3D2D1D0Q3Q2Q1Q00ФФФФФФФФ00001↑0ФФdcbadcba1↑10ФФФФФQ3Q2Q1Q01↑1Ф0ФФФФQ3Q2Q1Q01↑111ФФФФ状态码加1从功能表中可知,当清零端CR="0",计数器输出Q3、Q2、Q1、Q0立即为全"0",为异步复位功能.

当CR="1"且LD="0"时,在CP脉冲上升沿作用后,74LS161的输出端Q3、Q2、Q1、Q0的状态分别与并行数据输入端D3,D2,D1,D0的状态相同,为同步置数功能.

而当CR=LD="1"、EP、ET中有一个为"0"时,计数器不计数,输出端状态保持不变.

只有当CR=LD=EP=ET="1"、CP脉冲上升沿作用后,计数器加1.

此外74LS161还有一个进位输出端CO,其逻辑关系是CO=Q3Q2Q1Q0ET.

(注:A对应D0,QA对应Q0.

)20合理应用计数器的清零功能和置数功能,一片74LS161可以构成16以下的任意进制分频器.

(1)用异步清零功能设计16以下任意进制分频器图4-4-2是构成7分频的电原理图.

图中每个时钟(CP)脉冲作用后,74LS161就加"1",当Q2=Q1=Q0="1"时,74LS20输入全"1"、输出为"0".

计数器立即复位并重新开始计数.

74LS161输出端随时钟脉冲输入的变化规律列于表4-4-2.

每输入7个时钟脉冲,复位控制与非门的输出端就有一个很窄的负脉冲,脉冲的宽度约为2tpd时间.

同理可列表4-4-3,表示不同分频数时复位控制与非门输入端和74LS161输出端的连接规律,四输入与非门的多余输入端接高电平.

异步复位时在Q3、Q2、Q1、Q0输出端上可能会出现不应有的毛刺信号.

表4-4-2图7分频电路中各触发器的输出状态CPQ3Q2Q1Q00000010001200103001140100501016011070111表4-4-3与非门输入端与分频数的关系表分频数3456789101112131415A11111Q3Q3Q3Q3Q3Q3Q3Q3B1Q2Q2Q2Q21111Q2Q2Q2Q2CQ111Q1Q111Q1Q111Q1Q1四与非门输入DQ01Q01Q01Q01Q01Q01Q0(2)利用同步置数法实现16位以下的任意进制分频图4-4-3是由74LS161和74LS04组成的9分频器,利用进位信号CO反相后产生预置数控制信号.

在CP脉冲作用后,74LS161就加1.

当Q3=Q2=Q1=Q0=ET="1"时,进位端CO输出为"1",反相后使74LS161的置位控制端LD有效,计数器进入置数准备状态.

当下一个时钟脉冲上升沿到达时,数据输入端D3、D2、D1、D0的数据被置入内部触发器,完成置数功能.

LD端的脉冲频率为计数时钟的9分频,负脉冲宽度为一个时钟周期.

利用进位信号CO同步置数的电路分频数N为N=D3*23+D2*22+D1*21+D0*20+1(4-4-1)式中D3、D2、D1、D0接地时为"0",否则为"1".

例如图4.

4.

3中,D3="0",D2=D1=D0="1",代入4-4-1式中可得分频数为21N=0*23+1*22+1*21十1*20+1=9表4-4-4列出了图4-4-3在每个时钟脉冲CP作用下Q3,Q2,Q1,Q0和CO的输出的状态.

图4-4-39分频电原理图表4-4-4图4-4-3中74LS161的输出状态表CPQ3Q2Q1Q0CO001110110000210010310100410110511000611010711100811111901110(3)255以下分频器当分频数要求在17~256之间时,可以采用两片4位二进制(模16)的加计数器74161级联.

级联后计数器的模相乘,分频数为256.

然后可以采用反馈复位或反馈置数方法减少分频数,但要注意级联后的计数器成为一个整体,复位控制或预置控制必须对两片同时作用.

二进制加计数器的级连原则是:当低位计数器从最大编码值状态复位为全"0"状态(溢出)时产生进位,使高位计数器加1.

进位方式分异步和同步两种:①异步进位方式——低位计数器的进位信号控制高位计数器的计数脉冲输入端.

同异步二进制计数器的设计方式类似,根据计数器的时钟触发方式,在低位计数器状态码从最大值复"0"瞬间,选择合适的输出为高位计数器提供有效的计数脉冲边沿.

如果计数器本身有进位输出信号,可利用进位信号的后沿使高位计数器加1.

要注意进位信号有效沿与计数器触发方式的匹配.

②同步进位方式——低位计数器的进位信号控制高位计数器的使能.

只有当低位计数器溢出前(最大有效状态码时),高位计数器的使能才有效,下一个计数脉冲使低位计数器复位同时使高位计数器加1.

所以同步进位方式只适用于具有使能控制的集成计数器.

同样要注意进位信号有效电平与计数器使能有效电平的匹配.

22(a)(b)图4-4-418分频原理图和波形图表4-4-518分频电路中各输出端的状态#274LS161#174LS161CPCO1Q3Q2Q1Q0LDCO2Q3Q2Q1Q0LD↑011101011101↑011101111111↑011111000001↑011111000011↑011111000101↑011111000111↑011111001001↑011111001011↑011111001101↑011111001111↑011111010001↑011111010011↑011111010101↑011111010111↑011111011001↑01111101101123↑011111011101↑111110111110↑011101011101图4-4-4(a)中两片计数器74LS161采用了同步进位方式,#174LS161的进位输出Co控制#274LS161的使能ET.

仅当#174LS161状态计到全"1"时,其进位CO1=Q3.

Q2.

Q1.

Q0.

ET="1",才能使#274LS161的使能有效加1.

即#1计数器每16个脉冲状态循环一次,使#2计数器加1.

所以,两片74161级联后构成模为16*16=256的计数器电路.

若根据二进制位权标注各输出位序,#174LS161的输出为Q3、Q2、Q1、Q0,#274LS161的输出为Q7、Q6、Q5、Q4.

由式4-4-1可知,利用计数器进位信号Co实现同步反馈置数的分频率计算式为:N=D—7*27+D—6*26+D—5*25+D—4*24+D—3*23+D—2*22+D—1*21+D—0*20+1(4.

4.

2)其中D7~D4是#274LS161的预置数,D3~D0是#174LS161的预置数.

改变两片74LS161置数端的状态D7~D0可很方便地改变分频数.

根据图4-4-4(a)电路,其预置数D7~D0="11101110",代入4-4-2,得分频数为N=20+24+1=18图4-4-4(a)电路的工作和预置数过程列于表4-4-5,两片74LS161的CO波形如图4-4-4(b)所示.

3.

实验预习要求(1)复习并掌握任意进制分频器的工作原理.

(2)熟悉74LS161的引脚,正确理解74LS161的真值表.

(3)按实验内容分别设计好电路原理图,并绘制好实验记录所需要的表格.

4.

实验内容及步骤(1)利用74LS161的清零端CR设计一个12分频器.

当时钟频率为1Hz时,用发光二极管显示74LS161Q3~Q0的输出状态,并填入表4-4-6中.

表4-4-612分频电路74LS161输出端状态利用CR端利用LD端时钟Q3Q2Q1Q0CRQ3Q2Q1Q0Co1234567891011241213(2)利用74LS161的置数端LD设计一个12分频器.

当时钟频率为1Hz时,用发光二极管显示74LS161Q3~Q0的输出状态,并填入表4-4-6中.

(3)用两片74LS161和74LS00设计23或33分频器,输入时钟频率为10kHz时,观察并记录CP脉冲、CO1和CO2的波形.

(4)当分频器为23时,把#274LS161的EP和ET对调,观察并记录CP脉冲、CO1和CO2的波形.

5.

实验设备和器材(1)双踪示波器1台(2)数字逻辑实验箱1台(3)TTL集成器件(74LS161、74LS00)2片、1片6.

实验思考题(1)试设计一个分频数为350的分频器电路,画出电原理图.

(2)用74LS161设计一个模24的计数器.

(3)试解释实验时记录在表4-4-6中CR和CO的状态.

7.

实验报告要求(1)按实验要求检查结果,记录波形,填好表格.

(2)分析用74LS161实现12分频的两种电路的特点,试讨论适用范围.

(3)理论分析实验内容的结果.

257.

集成移位寄存器应用实验1.

实验要求和目的(1)了解集成移位寄存器的控制功能.

(2)掌握集成移位寄存器的应用.

2.

实验原理移位寄存器的功能是:当时钟控制脉冲有效时,寄存器中存储的数码同时顺序向高位(左移)或向低位(右移)移动一位.

所以,移位寄存器的各触发器状态必须同时变化,为同步时序电路.

移位寄存器数据可以按序逐位从最低位或最高位串行输入寄存器,也可以通过置数端并行输入寄存器.

所以移位寄存器的数据输入、输出方式有:并行输入/并行输出、并行输入/串行输出、串行输入/并行输出、串行输入/串行输出.

移位寄存器主要应用于实现数据传输方式的转换(串行到并行或并行到串行)、脉冲分配、序列信号产生以及时序电路的周期性循环控制(计数器).

四位移位寄存器74LS194的逻辑功能如表4-5-1所示.

在方式信号S1,S0控制下,74LS194可以实现左移(串行数据从DSL输入)、右移(串行数据从DSH输入)、置数(并行数据从D3~D0输入)及保持(输出不变)功能.

表4-5-1四位移位寄存器74194功能表输入输出功能CRS1S0DSHDSLCKD3D2D1D0Q3Q2Q1Q00φφφφφφ0000异步复位111φφ↑ABCDABCD同步置数110Diφ↑φDiQ3Q2Q1右移101φDi↑φQ2Q1Q0Di左移100φφ↑φQ3Q2Q1Q0保持图4-5-1为简易乒乓球游戏机电路.

输入R,L为球拍击球信号,高电平有效,输出Q3-Q0接四个发光二极管指示乒乓球的运动轨迹.

游戏规则:R或L输入一个正脉冲发球,发光二极管指示球向对方移动,到达对方顶端位置时,对方必须及时接球,使球返回,否则就会失球.

输入的移位脉冲频率越高,球的移动轨迹越快,接球难度越大.

3.

实验参考电路(1)乒乓球游戏机电路原理如图4-5-1所示.

(2)移存型计数器如图4-5-2所示.

4.

实验预习要求(1)分析图4-5-1中两个或非门组成什么功能的逻辑电路说明整个电路的工作原理.

(2)如果希望球的运动轨迹用八个发光二极管指示,怎样改进电路(3)分析图4-5-2电路的状态转换关系、任一输出信号的序列和自启动能力.

(4)用两片74LS194设计一个串行数据传输电路,发送方将并行输入的四位二进制数据转换成串行数据输出,接收方将串行输入的数据转换成并行数据输出,信号传输位序任意选择.

画出电原理图.

(5)用741LS94设计一个四位环形计数器,移位方向任意,可预置初值"0001",画出电原理图.

26(6)用74LS194设计一个四位扭环形计数器,移位方向任意,具有复位控制功能,画出电原理图.

5.

实验内容与步骤(1)乒乓球游戏电路实验①连接图4-5-1电路或非门部分,R,L端接逻辑开关,Q,Q—端接发光二极管.

测试并记录电路的逻辑功能.

②连接4-5-1电路移位寄存器部分,观察游戏效果.

注意:发球或接球动作是给予R或L一个正脉冲,即逻辑开关置"1"后必须复"0",动作必须准确,置"1"的时间过短发不出球或接不住球;置"1"的时间过长,指示球轨迹的发光二极管可能不是一个而是多个,影响游戏效果.

(2)移存型计数器连接4-5-2电路.

电路复位后输入1Hz时钟,观察电路输出状态是否与理论分析相同.

时钟脉冲改为10kHz,用示波器记录Q3和Q2的输出信号波形.

(3)串行信号传输连接串行信号传输电路.

发送方和移位接收方的寄存器分放在两组实验装置上.

发送方的四位并行数据输入由逻辑开关控制,设置值任意.

接收方的四位并行输出接发光二极管.

移位脉冲CP由发送方装置的逻辑脉冲按钮提供,观察数据的串行传输过程.

(4)74LS194构成的四位环形计数器①连接电路,输出接发光二极管,时钟接1Hz脉冲,预置控制端接逻辑开关.

②先预置初值"0001",然后设置移位工作方式,观察实验效果,记录状态转换图.

③时钟脉冲频率改为1kHz,用示波器分别观察四个输出信号的周期及相位关系,画出波形图.

(5)四位扭环形计数器连接电路,输出接发光二极管,时钟接1Hz脉冲,观察实验效果,记录状态转换图.

6.

实验设备与器材(1)数字逻辑实验箱1台(2)集成四-2输入或非门74LS021片(3)集成四异或门74LS861片(4)集成四位移位寄存器74LS1942片277.

实验思考题(1)图4-5-1电路的缺陷是:如果球未到达对方顶端位置,对方击球,球也会返回.

思考能否增加一个发球输入信号改进电路,弥补此缺陷.

(2)如何修改图4-5-2电路使之具有自启动能力8.

实验报告要求(1)完成预习内容要求设计的电原理图.

(2)实验结果处理.

(3)写出图4-5-2电路的输出序列(4)回答思考题.

触摸云 26元/月 ,美国200G高防云服务器

触摸云触摸云(cmzi.com),国人商家,有IDC/ISP正规资质,主营香港线路VPS、物理机等产品。本次为大家带上的是美国高防2区的套餐。去程普通线路,回程cn2 gia,均衡防御速度与防御,防御值为200G,无视UDP攻击,可选择性是否开启CC防御策略,超过峰值黑洞1-2小时。最低套餐20M起,多数套餐为50M,适合有防御型建站需求使用。美国高防2区 弹性云[大宽带]· 配置:1-16核· ...

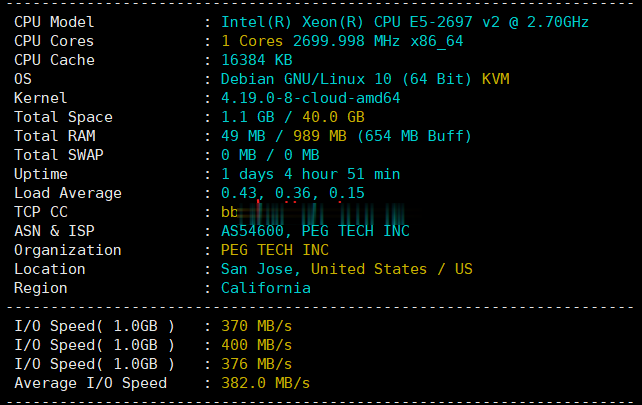

raksmart:全新cloud云服务器系列测评,告诉你raksmart新产品效果好不好

2021年6月底,raksmart开发出来的新产品“cloud-云服务器”正式上线对外售卖,当前只有美国硅谷机房(或许以后会有其他数据中心加入)可供选择。或许你会问raksmart云服务器怎么样啊、raksm云服务器好不好、网络速度快不好之类的废话(不实测的话),本着主机测评趟雷、大家受益的原则,先开一个给大家测评一下!官方网站:https://www.raksmart.com云服务器的说明:底层...

TmhHost暑假活动:高端线路VPS季付8折优惠,可选洛杉矶CN2 GIA/日本软银/香港三网CN2 GIA/韩国双向CN2等

tmhhost怎么样?tmhhost正在搞暑假大促销活动,全部是高端线路VPS,现在直接季付8折优惠,活动截止时间是8月31日。可选机房及线路有美国洛杉矶cn2 gia+200G高防、洛杉矶三网CN2 GIA、洛杉矶CERA机房CN2 GIA,日本软银(100M带宽)、香港BGP直连200M带宽、香港三网CN2 GIA、韩国双向CN2。点击进入:tmhhost官方网站地址tmhhost优惠码:Tm...

触发器的作用为你推荐

-

微盟赔付方案2017最新公司破产员工赔偿的标准是什么?bbs.99nets.com怎么制作RO单机月神谭给点人妖。变身类得小说。www.522av.com跪求 我的三个母亲高清在线观看地址 我的三个母亲高清QVOD下载播放地址 我的三个母亲高清迅雷高速下载地址www.622hh.comwww.710av.com怎么不可以看了www.kanav001.com翻译为日文: 主人,请你收养我一天吧. 带上罗马音标会更好www百度指数词百度指数为0的词 为啥排名没有partnersonline我家Internet Explorer为什么开不起来dadi.tv电视机如何从iptv转换成tv?dadi.tvApple TV是干嘛的?怎么用?多少钱?