波形ubuntu11.10下载

"所见即所得"波形发生器【摘要】任意波形发生器(AWG),是信号源的一种,它不仅可以输出标准信号,而且可以方便地产生任意波形,在测控、通信,医疗等领域有着广泛的应用.

本文设计了一个基于直接数字频率合成技术(DDS)和Qt编程的任意波形发生器.

DDS模块采用FPGA来实现,具有高速,可扩展等突出优点,通过接收来自Qt程序的数据生成波形.

Qt编程以Linux2.

6和ARM9为平台,提供友好的用户界面(GUI),实现参数设置,触摸笔输入,提取波形参数和数据,传输数据等功能.

通过触摸笔绘制任意波形,即可产生与所绘波形的各种参数和数据均相同的实际电信号,达到"所见即所得"的效果.

此外还提供了单次触发和循环触发模式及延时输出功能,可用于快速方便的产生任意波形.

通过使用多种仪器对系统性能和技术参数进行测试,证明系统符合设计要求.

最后本文还提出了系统改进和完善的一些思路和设想.

【关键字】任意波形发生器;所见即所得;DDS;FPGA;Qt[Abstract]ArbitraryWaveformGenerator(AWG),isonekindofthesignalsources,itcanproducenotonlystandardsignalsbutalsoarbitrarysignalsexpediently,itisusedforavarietyofapplicationsinthefieldofmeasuringandcontrol,communicationsandmediacaletc.

Thispaperpresentsandesignofarbitrarywaveformgeneratorbasedondirectdigitalfrequencysynthesis(DDS)andQtprogramming.

TheDDSmoduleisimplementedthroughFPGA,thismeansithasthecharacterofhighspeedandexpansibility,itgeneratewaveformwiththedatareceivedfromtheQtapplication.

TheQtprogrammingisbasedonLinux2.

6andARM9platform,itprovidesafriendlygraphicaluserinterface(GUI),achievesparametersetting,touchingpeninput,waveformparameteranddataidentificationanddatatransmissionetc.

wecanobtainanelectricalsignalwhichhasthesameparameteranddatawiththewaveformdrawnbythetouchingpen,achieving"WhatWouSeeIsWhatYouGet".

Alsopresentisone-slot-trigger,cycle-triggermdoeanddelayoutput,thesystemcanbeusedtoproducearbitrarywaveformquicklyandeasily.

Throughsystemperformanceandtechnicalparametertesting,allofthedesigningrequirementsareobtained.

Intheendofthepapertherealsopresentssomethoughtsandtentativeplansforimprovingandperfectingthesystem.

[Keywords]ArbitraryWaveformGenerator,WhatWouSeeIsWhatYouGet,DDS,FPGA,Qt目录绪论11整体设计方案及论证21.

1设计要求21.

2系统方案选择及论证21.

3系统总体结构22系统硬件设计32.

1硬件开发平台的选择32.

1.

1FPGA及CycloneII系列简介32.

1.

2DDS简介42.

1.

3ARM简介42.

1.

4硬件开发工具链42.

2硬件设计原理42.

2.

1DDS原理42.

2.

2DDS在FPGA中的实现52.

2.

3DDS控制寄存器的设计62.

2.

4通信接口模块的操作时序72.

3硬件模块的设计82.

3.

1分频器模块82.

3.

2相位累加器模块82.

3.

3DDS控制及通信模块92.

3.

4电平偏移电路102.

4硬件调试113系统软件设计123.

1软件开发平台123.

1.

1嵌入式Linux简介123.

1.

2Qt及Qt/Embedded简介123.

1.

3开发工具链123.

2软件总体设计133.

2.

1GUI设计133.

2.

2编程原理和方法143.

2.

3驱动程序设计153.

3软件调试174软硬件联合调试174.

1系统调试174.

1.

1系统组装和测试174.

1.

2联合调试184.

1.

3调试小结194.

2系统测试194.

2.

1测试仪器194.

2.

2测试波形20结论23致谢24参考文献25附录1分频器模块源代码26附录2相位累加器模块源代码27附录3DDS控制及通信模块源代码28绪论随着计算机技术和微电子技术的不断进步,来自很多行业的用户都在面对各种新型电路,这些电路在设计、生产和测试过程中需要一些传统函数信号发生器难以生成的测试信号,并且对信号源的各项性能指标均不断提出了更高的要求.

任意波形发生器(AWG)就在这种情况下应运而生了.

AWG通常提供较深的存储器,较大的动态范围以及较宽的带宽,来满足各式各样的应用,包括通信、半导体和系统测试.

AWG接收来自用户自定义的数据,并利用这些数据来生成任意波形.

直接数字频率合成器DDS(DirectDigitalFrequencySynthesizer)的基本结构由J.

Tiemev在1971年首次提出,其在"ADigitalFrequencySynthesizer"一文首先提出了以全数字技术,从相位概念出发直接合成所需波形的一种新合成原理.

限于当时的技术和器件产品,它的性能指标不能与以有的技术相比,故未受到重视.

近年来随着VLSI技术的进步,这种结构独特的频率合成技术得到了充分的发展但是由于DDS数字化实现的固有特点,其输出频谱杂散比较大,因此80年代末90年代初,掀起了对DDS频谱研究的热潮.

建立了杂散信号模型,对DDS相位截断引起的杂散进行了深入的分析,并以数论为基础得到了一些有益的结论.

随后从波形分析角度,和从傅氏分析角度进行了类似的讨论[1].

DDS的基本优点是在微处理器的控制下,能够准确而快捷地调节输出信号的频率、相位和幅度.

搭配波形存储器可以实现任意波形的产生.

此外,DDS具有频率和相位分辨率高、频率切换速度快、易于智能控制等突出特点.

这些特点使新出现的DDS及其与锁相环技术组合技术已经成为频率合成技术的理想的解决方案之一.

1整体设计方案及论证1.

1设计要求本系统要求波形通过触摸笔绘制,然后生成与所绘波形周期,峰值等各参数均相同的实际电信号,也可对波形进行适当的处理和优化,然后输出波形.

具体的参数如下:(1)时标5MHZ,输出信号周期分辨率最高200ns(2)存储深度2048点(可扩展)(3)输出电压范围±5V(分辨率50mV)(4)输出阻抗50Ω±2%(5)具备单次触发和循环触发功能(6)具备输出延时功能,延时范围1s-999s(7)具备直流输出能力1.

2系统方案选择及论证本系统总体上分为硬件和软件两部分.

硬件部分主要是一个由DDS模块构成的任意波形发生器.

软件部分需要提供一个人机交互界面,通过触摸笔输入,获取波形数据,并传输给DDS模块.

因为使用触摸笔及图形界面,需要选用较高处理能力的微控制器,在此选用ARM9作为软件部分的编程平台.

DDS模块构成的任意波形发生器是本系统的核心,它的实现方式有多种,较为常见的有以下两种方案:方案1:采用专用DDS芯片,具有编程容易,精度高,稳定性好等优点;但是其存储深度固定,灵活性和可扩展性较差,而且价格昂贵.

方案2:采用FPGA实现DDS,这种方式的优点是具有极大的灵活性和可扩展性,可以对DDS及通信接口的结构做适当的修改以适应系统的需要;可通过外部扩展SDRAM增加存储深度;便于集成化.

其缺点是设计较为复杂.

统筹以上两个方案,本系统选用方案2.

1.

3系统总体结构本系统软件和硬件都采用模块化设计的方法,按照功能将软件和硬件划分为许多模块,以模块为单位进行设计,这样有利于降低系统的复杂度,使设计和维护简单化.

系统总体的结构如下图.

图1.

1系统结构图其中硬件部分主要是一个用FPGA实现的DDS模块,包括通信接口,波形存储器,相位累加器,分频器,D/A,低通滤波器等几个子模块,负责接收波形数据和参数并产生波形.

软件部分采用Linux2.

6内核和Qt编程,提供友好的图形交互界面,输入设备为触摸笔,允许用户输入任意波形,通过Qt编程获取用户输入的任意波形并作适当处理,然后通过底层的驱动程序将波形数据和参数传输给DDS模块.

同时Qt通过驱动程序监控DDS模块的运行状态并随时显示出来.

2系统硬件设计2.

1硬件开发平台的选择2.

1.

1FPGA及CycloneII系列简介FPGA(Field-ProgrammableGateArray),即现场可编程门阵列,它是在PAL、GAL、CPLD等可编程器件的基础上进一步发展的产物.

它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点.

目前以硬件描述语言(Verilog或VHDL)所完成的电路设计,可以经过简单的综合与布局,快速的烧录至FPGA上进行测试,是现代IC设计验证的技术主流.

这些可编辑元件可以被用来实现一些基本的逻辑门电路(比如AND、OR、XOR、NOT)或者更复杂一些的组合功能比如解码器或数学方程式.

在大多数的FPGA里面,这些可编辑的元件里也包含记忆元件例如触发器(Flip-flop)或者其他更加完整的记忆块[2].

CycloneII是Altera于2005年推出的FPGA系列芯片,采用90nm工艺,1.

2v内核供电,属于低成本FPGA.

CycloneII器件提供了4,608到68,416个逻辑单元(LE),并具有一整套最佳的功能,包括嵌入式18比特x18比特乘法器、专用外部存储器接口电路、4kbit嵌入式存储器块、锁相环(PLL)和高速差分I/O能力.

CycloneII器件提供针对低成本应用的用户定制FPGA特性,其密度分布范围广,含有丰富的存储器和嵌入式乘法器,并提供多种封装选择[3].

2.

1.

2DDS简介直接数字频率合成(DDS)技术是60年代末出现的第三代频率合成技术,以Nyquist时域采样定理为基础,在时域中进行频率合成.

DDS具有相对带宽很宽,频率转换时间极短,频率分辨率可以做到很高等优点;另外,全数字化结构便于集成,输出相位连续,频率、相位、幅度都可以实现程控,通过更换波形数据可以轻易实现任意波形功能[1].

2.

1.

3ARM简介ARM(AdvancedRISCMachines)是一类32位RISC微处理器的通称.

目前ARM微处理器及技术已经深入到工业控制,无线通讯,消费电子等多个领域[4].

ARM处理器具有体积小,低功耗,高性能等特点.

ARM9是ARM家族中主流的处理器,主要应用于手持设备,PDA,机顶盒等设备中.

2.

1.

4硬件开发工具链本系统的FPGA芯片采用CycloneII系列的EP2C35F484,它具有33216个逻辑单元(LE),105个M4KRAM块,完全满足要求.

FPGA开发工具选用Altera公司的QuartusII5.

1,支持原理图,VerilogHDL等多种设计输入形式,内嵌自有的综合器以及仿真器,可以完成从设计输入到硬件配置的完整FPGA设计流程.

FPGA的仿真和调试工具采用Mentor公司的ModelsimSE6.

4c和Quartus内置的SignalTap.

编程语言选用VerilogHDL,VerilogHDL是一种硬件描述语言(hardwaredescriptionlanguage),为了制作数字电路而用来描述ASICs和FPGA的设计之用.

Verilog接近于C语言,学习使用都较为容易.

2.

2硬件设计原理2.

2.

1DDS原理DDS的基本原理是利用采样定理,通过查表法产生波形.

DDS的结构有很多种,其基本的电路原理可用图2.

1表示.

图2.

1DDS原理通常DDS由相位累加器,波形存储器,DA,低通滤波器,参考时钟等部分组成.

相位累加器由N位加法器与N位累加寄存器级联构成.

每来一个时钟脉冲fs,加法器将频率控制字K与累加寄存器输出的累加相位数据相加,把相加后的结果送至累加寄存器的数据输入端.

累加寄存器将加法器在上一个时钟脉冲作用后所产生的新相位数据反馈到加法器的输入端,以使加法器在下一个时钟脉冲的作用下继续与频率控制字相加.

这样,相位累加器在时钟作用下,不断对频率控制字进行线性相位累加.

由此可以看出,相位累加器在每一个时钟脉冲输入时,把频率控制字累加一次,相位累加器输出的数据就是合成信号的相位,相位累加器的溢出频率就是DDS输出的信号频率.

用相位累加器输出的数据作为波形存储器(ROM)的相位取样地址,这样就可把存储在波形存储器内的波形抽样值(二进制编码)经查找表查出,完成相位到幅值转换.

波形存储器的输出送到D/A转换器,D/A转换器将数字量形式的波形幅值转换成所要求合成频率的模拟量形式信号.

低通滤波器用于滤除不需要的取样分量,以便输出频谱纯净的正弦波信号.

DDS在相对带宽、频率转换时间、高分辨力、相位连续性、正交输出以及集成化等一系列性能指标方面远远超过了传统频率合成技术所能达到的水平,为系统提供了优于模拟信号源的性能.

2.

2.

2DDS在FPGA中的实现DDS的实现方式有多种.

因为本系统需要产生任意的信号,因此其波形存储器需要采用RAM;需要产生频率较高的基准时钟和输出信号,因此选用FPGA来实现DDS,可以实现较高的速度和精度.

设计框图如下图.

图2.

2本系统DDS结构图根据本系统的需要,对DDS的结构作了适当的修改:把RAM作为波形存储器;相位累加器设置步进值固定为1;参考时钟可通过参数控制.

同时这几个模块受控于DDS控制模块,并通过通信接口与ARM通信.

基准时钟采用5MHZ,经过分频之后周期分辨率最高可达200ns(即分频为1);分频器用于产生DDS和DA的时钟信号,它受控于控制寄存器中的低32位数据,因此可以分频1~232;相位累加器在DDS时钟作用下产生递增的相位信号,通过对RAM进行寻址获取波形数据,再通过DA转换为模拟电压信号;DA的输出信号中叠加了直流分量,因此需要采用一个电平偏移电路将直流分量抵消,并将信号放大适当的倍数;低通滤波器滤除DA转换产生的高频噪声信号.

RAM的容量决定了本系统的存储深度,本系统设置RAM的容量为2048字节,即存储深度可以达到2048点.

可以通过扩展RAM的容量来增加存储深度(DDS控制模块和相位累加器需要做适当调整),最大可以达到32768点.

2.

2.

3DDS控制寄存器的设计DDS的控制寄存器位于DDS控制模块内部,完全控制整个DDS模块的运行参数和状态,并通过通信接口接收来自ARM的数据.

根据波形参数和控制的需要,共设置了8个寄存器,地址从0到7.

其功能和分配如表2.

1所示其中0-3字节存储分频参数,占用32位,因此分频范围为1~232.

4-5字节存储相位累加器的参数,用于控制波形点数和触发模式,其各位的含义如表2.

2所示.

6字节只使用了最低位,为1则启动DDS,为0则停止DDS.

地址7是一个虚地址,并不对应着实际的物理寄存器,而是指向RAM的某一个单元,通过对地址7的写操作就间接的实现了对整个RAM的操作,类似于单片机中的间接寻址.

这样大大简化了对DDS的控制操作.

表2.

1控制寄存器的功能及分配ADDR01234567DATA分频参数波形点个数及循环控制位启动/停止RAM控制及间接寻址表2.

2相位累加器各位含义bit1514~1110~0含义触发模式0:单次触发1:循环触发保留波形点数2.

2.

4通信接口模块的操作时序因为对地址7的操作就是对RAM的操作,因此为了统一操作时序,对其他寄存器的操作也采用了与RAM相同的时序.

RAM的操作时序如图2.

4所示,其写时序为上升沿锁存数据,下降沿写入数据.

图2.

3RAM操作时序2.

3硬件模块的设计2.

3.

1分频器模块分频器模块根据分频参数对基准时钟进行分频,以提供给DDS时钟信号.

而分频参数是根据触摸屏上的刻度计算而来,因此分频器模块保证了触摸屏时间刻度和在示波器上的观察到的刻度一致!

其源代码见附录1.

其符号如下图.

图2.

4分频器模块引脚功能分配如下:clk:输入时钟rst:分频器复位,高电平有效param:分频参数,32位无符号数,可分频范围1-232clk_out:输出时钟ModelSim仿真波形如下图,其中param=0时不分频;param=1时2分频;param=2时3分频图2.

5分频器模块仿真波形2.

3.

2相位累加器模块此模块在DDS运行期间产生递增的相位信号,作为RAM的读取地址信号获得相应的波形数据;在与ARM通信过程中(此时DDS被强制停止)负责产生RAM的写入地址,与DDS控制寄存器的虚拟地址7配合使用,完成RAM的间接寻址操作.

DDS控制寄存器的4,5字节对应此模块的参数,其中低11位为计数参数(即计数的最大值),最高位为phase_cycle,用于控制单次输出还是循环输出波形,详见表2.

2.

此模块的源代码见附录2,其符号如下图.

图2.

6相位累加器模块引脚功能分配如下:clk:输入时钟rst:模块复位,高电平有效phase_param:计数参数,即计数的最大值,11位无符号数no_param在与ARM通信过程中有效,其值为1,在DDS运行期间须为0addr:输出相位/地址,11位无符号数,最大可寻址2048个字节stop:强制停止信号,只在产生单次波形时有效其仿真波形如下图,单次模式下,计数参数为10,计数到则产生stop信号图2.

7相位累加器模块仿真波形2.

3.

3DDS控制及通信模块此模块将DDS控制模块和通信模块整合在一块,负责与ARM通信和控制DDS的波形数据和运行状态.

其源代码见附录3,其符号如下图.

图2.

8DDS控制及通信模块引脚功能分配如下:clk:输入时钟rst:模块复位,高电平有效w_en:写使能,当ARM要写入数据的时候必须置为1,否则不能写入数据force_stop:强制停止DDS,主要用于单次信号的产生,一旦输出完毕即强制停止w_addr:写入地址,3位无符号数,用于寻址DDS的控制寄存器w_data:写入数据,8位freq_divide_param:分频参数输出,32位无符号数,用于控制分频模块phase_param:相位累加器参数,11位无符号数,用于控制相位累加器模块phase_cycle_bit:触发模式控制位,为1则表明为循环触发模式;为0则表明为单次触发模式.

start_stop_bit:启动/停止位,为1则启动DDS;为0则停止DDSram_en_bit:操作ram使能其操作时序如下图,图2.

9DDS控制及通信模块仿真波形2.

3.

4电平偏移电路电平偏移电路用于消除输出信号中的直流分量和调整信号增益,其电路图如下图.

图2.

10电平偏移电路根据此电路有,可见,适当调整的值即可消除输出信号的直流分量.

适当调整可以实现输出信号与输入信号的特定比例关系.

这样就可以使触摸屏上的刻度与实际波形的刻度一致!

2.

4硬件调试因为本硬件的设计必须在软件的控制下才能执行,因此硬件部分的单独调试主要通过Modelsim的仿真来实现.

更详细的调试见软硬件的联合调试一节.

3系统软件设计3.

1软件开发平台3.

1.

1嵌入式Linux简介嵌入式Linux是以Linux为基础的嵌入式操作系统,它被广泛应用在消费性电子产品以及航空航天等领域中.

嵌入式Linux突出的优点是开放源代码,可定制,裁剪性好,性能稳定,支持多种CPU和硬件平台,且开发和使用都较容易,有大量的工具和文档可供使用和参考.

3.

1.

2Qt及Qt/Embedded简介Qt是一个跨平台的C++图形用户界面应用程序框架.

它提供给应用程序开发者建立图形用户界面所需的所用功能[5].

Qt是完全面向对象的,模块化程度非常高,很容易扩展,并且允许真正地组件编程.

Qt具有优良的跨平台特性,支持多种系统和平台,包括Windows系统,所有的UNIX系统以及嵌入式系统等.

Qt遵循GPL协议,开放主要的源代码,用户可以在GPL的规定下自由添加新特性.

Qt/Embedded是面向嵌入式系统的Qt版本.

它是专门为嵌入式系统设计图形用户界面的工具包,包括一个完整的窗口系统.

它的特点是可移植性比较好,设计者能轻易的加入各种显示设备和硬件输入设备,很多基于Qt的XWindow程序都可以非常方便的移植到嵌入式版本.

Qt/Embedded为开发者提供了丰富的API调用功能和非常丰富的窗口小部件(Widgets),并且还支持窗口部件的定制,可以为用户提供友好的图形界面.

3.

1.

3开发工具链基于上述特点,本系统采用了嵌入式Linux平台和Qt/Embedded图形库开发图形用户界面.

本系统在设计过程中采用软件开发平台为(1)UbuntuLinux9.

10系统(2)Emacs编辑器(3)arm-linux-gcc4.

3.

2交叉编译器,gdb调试器(4)嵌入式Qt选用qtopia-2.

2.

0(5)项目管理采用Linux下的make,tmake等工具(6)宿主机采用FriendlyARM公司的micro2440开发板,这是一个基于三星S3C2440微处理器的开发板,支持多种外设,具有320X240分辨率的触摸屏,满足本系统的需要.

另外,Qt的编程语言为C++,底层驱动程序采用C语言编程.

3.

2软件总体设计3.

2.

1GUI设计GUI,即图形用户界面,是人机交互的窗口.

GUI的设计直接关系到产品的可操作性,是软件设计中非常重要的一部分.

本系统GUI的外观及说明如下图图3.

1GUI设计本GUI设计直观易懂,界面友好,各按钮和功能的安排合理,紧凑,有效的利用了触摸屏的空间.

左侧工具栏从上到下依次设置了几个工具区,其功能分别如下述:(1)绘图模式选择区,提供了4个预定义的绘图模式,任意波形模式允许用于绘制任意波形而不做任何修饰,这样可以用于产生精度要求不高的任意波形;正弦波绘图模式下,系统会根据用户输入的数据提取关键点,对波形进行圆滑,去抖,滤波等修饰功能,使最终输出的波形平滑,减少不需要的频率分量,可以达到较高的精度.

三角波及方波模式与此类似.

(2)波形输出设定区,提供了两种输出触发模式,即单次输出模式和循环模式.

单次模式下仅将用户输入的波形输出一次,可以应用于某些有限长度信号的情况,可通过示波器的单次触发模式捕捉和观察输出信号.

循环模式则将波形循环输出,形成连续波形.

图4.

2(2)和图4.

2(3)显示了这种区别.

此外还提供了一个停止按钮和一个状态指示,三种状态以3种颜色的信号灯来指示,方便用户了解和控制当前状态.

(3)时间设定区,包括时间刻度的设定和延迟输出时间的设定.

时间刻度,即时间轴(横轴)每一格的标度,可选择三种时间单位:us,ms和s,us模式下步进值为10,其他模式下步进值为1,这样的设计方便了用户快速设定时间刻度.

比如用户需要设置时间刻度为23ms,则可以先调到us模式,快速调节到20us,然后切换到ms模式,再前进3次加计数即可到23ms.

这对于没有键盘的设备是非常快速的.

延迟输出时间是指从用户点击启动到波形输出之间的延迟时间,只所以设定这个功能是因为很多情况下用户不需要立即产生波形,而是等待一小段时间之后输出.

尤其是单次输出情况下,用户可以设定延迟一段时间输出,在输出之前做好捕捉信号的准备,等待信号的到来.

(4)左下侧提供了清屏和退出功能.

中间的黄色区域是绘图区,画布带有刻度,横轴为时间,纵轴为电压;用户可通过触摸笔在上面绘制波形,波形只能从左向右绘制而不可以反向绘制;但是可以修改已绘波形,修改的波形自动变为红色,直到用户松开触摸笔,波形自动修改过来并显示为蓝色.

本GUI还提供了滚动条,用于绘制超出屏幕范围的波形.

可以绘制较长的序列信号.

3.

2.

2编程原理和方法本程序采用面向对象和事件驱动的编程方法,整个GUI程序划分为两个类,其中主窗口为一个类,类名为MainWindow,继承自Qt的QMainWindow类,它提供了工具条(toolbar)和一个主窗口(mainwindow);另一个类是DrawWidget,提供了一个绘图区域,有4种事件,分别为触摸笔按下(mousePressEvent),移动(mouseMoveEvent),松开(mouseReleaseEvent)和绘图区重绘事件(paintEvent).

同时提供了处理波形的函数waveProcess和调用底层驱动的接口.

滚动条是通过QScrollView类提供的视图功能来实现的.

触摸笔的3个事件的发生顺序和处理过程如下图:图3.

2触摸笔的事件及发生顺序对象间的通信,如工具栏的工具按钮和相应的处理函数,通信函数和状态指示控件的通信,使用Qt著名的信号/槽机制.

信号/槽机制是Qt的一个中心特征,用于对象间的通讯[6].

在图形用户界面编程中,我们经常希望一个窗口部件的一个变化被通知给另一个窗口部件.

更一般地,我们希望任何一类的对象可以和其它对象进行通讯.

当一个特定事件发生的时候,一个信号被发射.

Qt的窗口部件有很多预定义的信号,但是我们总是可以通过继承来加入我们自己的信号.

槽就是一个可以被调用处理特定信号的函数.

绘图事件(paintEvent)采用双缓冲机制.

双缓冲技术是一种GUI编程技术,它指的是在一个不在屏幕上的位图上渲染一个物件并把此位图拷贝到屏幕上,常用于消除闪烁和提供一个快速用户界面[7].

本程序采用了QPixmap类来实现双缓冲.

时间刻度设置用来修改在绘图区显示的时间轴(横轴)的刻度和获取传给DDS控制寄存器的分频参数.

本系统中时间轴(横轴)每一格为50个像素,时间刻度的最小值为10us,这样每一个像素对应10us/50=200ns,因此基准时钟采用了5MHZ.

这样,刻度为10us则对应1分频;则任意的刻度值Nus,对应N/10分频,因us模式下步进值为10,而ms,s模式下的刻度转换为us必然都是10的倍数,因此最终的分频数据必然是整数.

通过对基准时钟的分频实现了绘图区的刻度和在示波器中观察波形的时间刻度保持完全一致!

在实际应用中延迟输出不需要精确的定时,因此可以通过软件来实现,以节省硬件资源.

本系统采用Qt的QTimer类来实现延时(定时)输出.

3.

2.

3驱动程序设计系统调用是操作系统内核与应用程序之间的接口,设备驱动程序是操作系统内核与机器硬件之间的接口.

设备驱动程序是内核的一部分,它完成以下功能:对设备初始化和释放把数据从内核传送到硬件和从硬件读取数据读取应用程序传送给设备文件的数据和回送应用程序请求的数据检测和处理设备出现的错误在Linux操作系统下有3类主要的设备文件类型:块设备、字符设备和网络设备.

字符设备与块设备的主要区别是:在对字符设备发出读/写请求时,实际的硬件I/O一般紧接着发生[8].

本系统即采用字符设备驱动.

在系统内部,I/O设备的存/取通过一组固定的入口点来进行,这组入口点是由每个设备的驱动程序提供的.

具体到Linux系统,设备驱动程序所提供的这组入口点由一个文件操作结构file_operation来向系统进行说明.

在用户自己的驱动程序中,首先要根据驱动程序的功能,完成file_operation结构中函数实现.

不需要的函数接口可以直接在file_operation结构中初始化为NULL.

file_operation变量会在驱动程序初始化时注册到系统内部.

当操作系统对设备操作时,会调用驱动程序注册的file_operation结构中的函数指针.

本系统的驱动函数需要提供3个函数调用,read函数用于读取DDS运行状态,write函数用于向DDS写入参数和波形数据,ioctl函数用于复位/启动/停止DDS.

另外还需要打开(open)和关闭设备函数(close).

file_operatio的定义如下staticstructfile_operationsdev_fops={.

owner=THIS_MODULE,.

ioctl=wave_ioctl,//对DDS复位/启动/停止等控制操作.

write=wave_write,//写入数据.

read=wave_read,//读取状态};驱动程序在wave_ioctl,wave_wirte,wave_read等几个函数中具体实现.

wave_write函数用于向DDS模块写入数据,其函数原型为ssize_twave_write(structfile*filp,constchar__user*buf,size_tcount,loff_t*f_pos);所需的波形参数和数据通过Qt程序打包,调用write函数(对应驱动程序中的wave_wrtie函数)一次性写入DDS模块.

wave_write函数的流程图如下.

图3.

3驱动程序wave_write函数流程图最终将驱动程序编译为模块文件(*.

ko),通过linux的命令modprobe和rmmod来加载和卸载驱动模块.

3.

3软件调试软件调试是编程的一个重要部分,也往往是最花费时间的部分.

一个稳定的程序必须经过反复的调试.

根据软件层次和编程语言的不同,将本系统的软件调试分为两个部分,即高层的Qt程序的调试和底层的驱动程序调试.

1.

Qt程序的调试采用GDB调试工具.

GDB是GNU开源组织发布的一个强大的UNIX下的程序调试工具.

GDB主要有四个方面的功能:(1)启动程序,可以按照自定义的要求运行程序.

(2)可让被调试的程序在你所指定的调置的断点处停住(断点可以是条件表达式)(3)当程序被停住时,可以检查此时程序中所发生的事.

(4)动态的改变程序的执行环境.

Qt程序的调试相对较为简单.

2.

驱动程序调试.

因为驱动程序属于内核的一部分,其调试也属于内核级的调试,相对要复杂一些.

同时驱动程序与硬件直接打交道,因此也需要结合硬件来调试.

在本系统驱动程序的编写过程中,采用了软硬件相结合的方式,软件方面采用printk函数输出相关的运行参数,然后通过cat/proc/kmsg命令获取内核信息以分析程序运行状态;硬件方面,采用数字示波器对GPIO口的输出信号进行捕捉,以分析时序是否满足要求.

经过反复调试,修改,再调试,最终驱动程序达到了预想的功能.

4软硬件联合调试4.

1系统调试在前面的章节中,我们详细讨论了"所见即所得"信号发生器的硬件设计和软件设计,并单独调试通过,但要使我们的软硬件设计达到系统的指标和功能,还必须进行软硬件联合调试、数据的测试,以验证方案的可行性,在必要的时候,我们还需要对系统的硬件和软件进行反复的改进,从而达到系统的优化设计.

在调试前,将程序修改为调试模式,将运行的参数输出到终端,方便对比和观察.

4.

1.

1系统组装和测试本系统主要采用已有的ARM9开发板和FPGA开发板,只有DA输出部分的电平偏移等电路需要自己制作.

(1)元件焊接焊接前首先要对电阻、电感、电容等的量值进行测量,以避免不必要的失误.

对芯片型号和封装需要注意.

焊接的时候要遵循两个原则:第一,先焊接贴片封装的器件,再焊接直插式的器件.

第二,对于直插式器件,先焊接封装较低的器件,再焊接封装较高的器件.

程序下载Qt程序编译为二进制文件通过ftp传输给ARM9开发板,建立快捷方式,并设置用户权限为可执行.

FPGA程序编译后通过JTAG下载器下载至EPCS(即行存贮器)中.

(3)模块连线连线必须在未加电时进行,主要是ARM9和FPGA的通信连接线,包括数据线,地址线和控制线,多达十几根,连线的时候注意ARM9开发板和FPGA开发板的引脚排列区别,连接完成之后再对每根连线进行检查,查看是否有接触不良或连线端子相碰的情况.

直到全部测试无误才连线完成.

(4)上电功能测试上电测试是调试的关键部分,按照模块化设计思想,应该分模块测试系统.

因为之前单独对硬件和软件模块测试通过,因此这里主要是检查电路是否运行正常.

以便为后面的联合调试做准备.

系统上电以后,测试各模块的电压和输入输出是否有异常,如果有异常则继续检查;如果没有问题,则可以进行下一步的操作.

4.

1.

2联合调试上述测试通过之后,开始联合调试,主要的软件调试工具是FPGA开发平台Quartus的SignalTap工具,硬件工具主要是示波器和万用表.

在Quartus中设置SignalTap,添加观察信号如下:ram的地址信号wraddress,数据信号data,写使能wren,时钟clock;DDS控制模块的地址信号w_addr,数据信号w_data,使能信号w_en;设定SignalTap的触发条件为ram的使能信号wren的上升沿.

采样时钟采用本系统的基准时钟(5MHZ).

编译下载并运行;在ARM板的绘图区绘制一个近似的正弦波,设置时间刻度为100us,周期近似为400us(占4格).

如图4.

2(1).

点击循环模式启动DDS,通过SignalTap捕捉到了数据.

如下图所示.

图4.

1SignalTap捕捉到的数据传输过程分析其时序,并与ARM9开发板上的输出数据(通过printk函数输出,包括波形的数据和参数)对比,看看是否一致,如果一致则表明通信模块工作正常,进行下一步操作;如果不正确则必须修改驱动程序,再次编译和调试.

之后的调试步骤如下.

(1)在确定通信模块工作正常之后,再使用频率计测量分频器的输出测试端,此时的频率应该为500KHz,则表明分频器模块工作正常.

否则需要修改分频器的verilog程序,再次编译测试,直到成功.

(2)观察wraddress为7时,依次写入的数据(写入的第一个数据对应波形的第一个有效点,第二个数据对应第二个有效点,依此类推),也就是写入RAM的数据.

如果与ARM9开发板上输出的波形数据一致,则表明RAM的操作正确,波形数据已写入ram,此时应有波形输出;否则需要修改DDS控制模块直到数据能正常写入ram.

(3)用示波器的直流输入模式下观察信号的输出端,如果信号有较大的直流量,则调节电平偏移电路的,使直流量基本抵消,然后重画一条电压等于0的信号,输出,再细调使输出信号等于0.

这样电平偏移就设定完毕.

(4)再绘制一个峰值是±5V的正弦信号(或方波),通过示波器观察输出信号的实际峰值,然后调节使示波器上的信号峰值也是±5V,这样放大倍数就调节完毕.

如图4.

2(3)所示.

(5)通过示波器的捕捉功能测试单次输出是否正常,波形如图4.

2(2)所示.

测试停止按钮是否正常以上调试都通过则表明整个系统运行正常,绘制任意的波形就可以产生实际的电信号,且电压值和频率都与实际值都一致,即"所见即所得"!

如果有不通过的则需要不断的修改,编译,下载,调试,直到成功为止.

4.

1.

3调试小结在本系统设计的调试过程中,最主要把握的是每个模块单独调试的方法和顺序,一旦单个模块正常,总体的调试就变的相对简单.

其次调试工具的使用对于提高效率起到了很大的作用!

期间还发现了一些未预料到的情况,比如传输数据的误码问题,还需要不断的完善.

总的来说,虽然在调试过程中出现了很多问题,但最终还是在不断解决问题并改进后调试出来了.

最初的设想终于变成了实际!

4.

2系统测试4.

2.

1测试仪器(1)示波器GWGDS-815C数字示波器(带宽100MHz)(2)频率计SS7201通用智能计数器(0.

001Hz~200MHz)(3)万用表Agilent34401A6位半数字万用表(4)失真度仪2N4116失真度测量仪4.

2.

2测试波形系统整体调试通过并调整好参数之后,开始进行波形的测试和测量.

在经过大量反复的测试和测量之后,现选取几组有代表性的波形,以验证系统的实现情况和相应的指标.

以下例子均设置绘图模式为任意波形模式.

1.

设置触摸屏时间刻度为100us,绘制一个正峰值为5V(最大值),负峰值为-3V;周期为400us的近似正弦波.

如图4.

2(1)所示.

调节示波器的时间刻度也为100us,电压刻度为2V,分别在单次触发模式和循环触发模式下捕捉波形,如图4.

2(2)和(3).

从图中可以看出:(1)生成的实际电信号正峰值为5.

04V或4.

92V,与绘制波形相近(因为手工绘制的波形无法确定具体的电压值,因此此处计算误差没有意义,下同);负峰值为-3.

02V或-3.

04V,与绘制波形一致.

(2)生成的实际电信号周期约为400us,通过频率计测得频率约为2.

5KHz,与绘制的波形一致.

通过此次测量可以确定实际产生的电信号与触摸屏上绘制的波形周期,峰值等参数均相同,即触摸屏上的时间刻度和电压刻度与示波器的时间刻度和电压刻度(需适当调整)一致,并且单次触发和循环触发功能都实现了.

另外,输出电压的最大值约为5V,满足需求.

2.

清屏,绘制一个包含正弦波,方波,三角波的波形,即任意波形,如图4.

3(1).

示波器的设置不变,设置循环触发模式并启动DDS,此时捕捉到的波形如图4.

3(2).

可见,生成的实际波形形状与绘制波形一致,即本系统实现了输出任意波形的功能.

3.

清屏,设置时间刻度为10us,绘制一个正脉动直流,如图4.

4(1)所示.

示波器相应设置时间刻度为10us,其余设置不变.

设置循环触发模式并启动DDS,此时捕捉到的波形如图4.

4(2).

可见,本系统实现了输出直流的功能,并且再次验证了触摸屏上时间刻度与示波器的时间刻度相同.

4.

清屏,设置时间刻度为100us,延时2s输出,绘制一个任意的正脉冲序列,如图4.

5(1)所示.

单次触发模式启动DDS,按下示波器的开始按钮,等待2s捕捉到的波形如图4.

5(2)所示.

这验证了延时输出功能.

这种脉冲序列可用于红外发射编码,数字电路的测试等,能明显提高实验的效率.

(1)用户绘制波形(2)单次输出波形(3)循环输出波形图4.

2单次与循环输出波形对比(1)用户绘制波形(2)实际输出波形图4.

3任意波形(1)用户绘制波形(2)实际输出波形图4.

4正脉动直流(1)用户绘制波形(2)实际输出波形图4.

5正脉冲序列结论经过老师的悉心指导和自己的努力,在详细了解FPGA和Qt编程的基础上,制作了完整的系统,圆满完成了设计要求.

经测试,该系统完成了预定的功能和指标:波形通过手写输入;可绘制任意波形,包扩直流和交流信号;可存储2048个波形数据点;输出电压范围±5V,分辨率为50mV;周期分辨率最大为200ns;具备单次触发和循环触发功能;具备延时输出功能.

总体上达到了输出波形与绘制波形一致,即"所见即所得"的效果.

整个系统集成度高,速度快,易于扩展;操作方便,可以快速产生任意波形.

当然系统现在还不够成熟,在测试过程中也发现了未考虑到的情况,比如数据传输误码问题,尤其表现在数据量很大的时候.

还有待进一步的修改和完善.

在波形的处理和优化方面尚存在不足,绘图的四种模式中只实现了任意波形模式,在此种模式下手工绘制的波形难以达到较高的精度,波形不够平滑,噪音多,缺少对波形数据点的精确设置.

在此以产生平滑正弦波为例提供改进的思路和方法,以备下一步的修改和完善.

- 波形ubuntu11.10下载相关文档

- 单击ubuntu11.10下载

- 郑州高新技术产业开发区管委会教育体育局创客教室采购项目

- 投标ubuntu11.10下载

- 投标人ubuntu11.10下载

- 政府采购项目名称:肇庆市工业贸易学校新疆班一体化教学实训设备采购

- 支持ubuntu11.10下载

ZJI:韩国BGP+CN2线路服务器,国内三网访问速度优秀,8折优惠码每月实付440元起

zji怎么样?zji最近新上韩国BGP+CN2线路服务器,国内三网访问速度优秀,适用8折优惠码zji,优惠后韩国服务器最低每月440元起。zji主机支持安装Linux或者Windows操作系统,会员中心集成电源管理功能,8折优惠码为终身折扣,续费同价,全场适用。ZJI是原Wordpress圈知名主机商:维翔主机,成立于2011年,2018年9月启用新域名ZJI,提供中国香港、台湾、日本、美国独立服...

Vultr VPS新增第18个数据中心 瑞典斯德哥尔摩欧洲VPS主机机房

前几天还在和做外贸业务的网友聊着有哪些欧洲机房的云服务器、VPS商家值得选择的。其中介绍他选择的还是我们熟悉的Vultr VPS服务商,拥有比较多达到17个数据中心,这不今天在登录VULTR商家的时候看到消息又新增一个新的机房。这算是第18个数据中心,也是欧洲VPS主机,地区是瑞典斯德哥尔摩。如果我们有需要欧洲机房的朋友现在就可以看到开通的机房中有可以选择瑞典机房。目前欧洲已经有五个机房可以选择,...

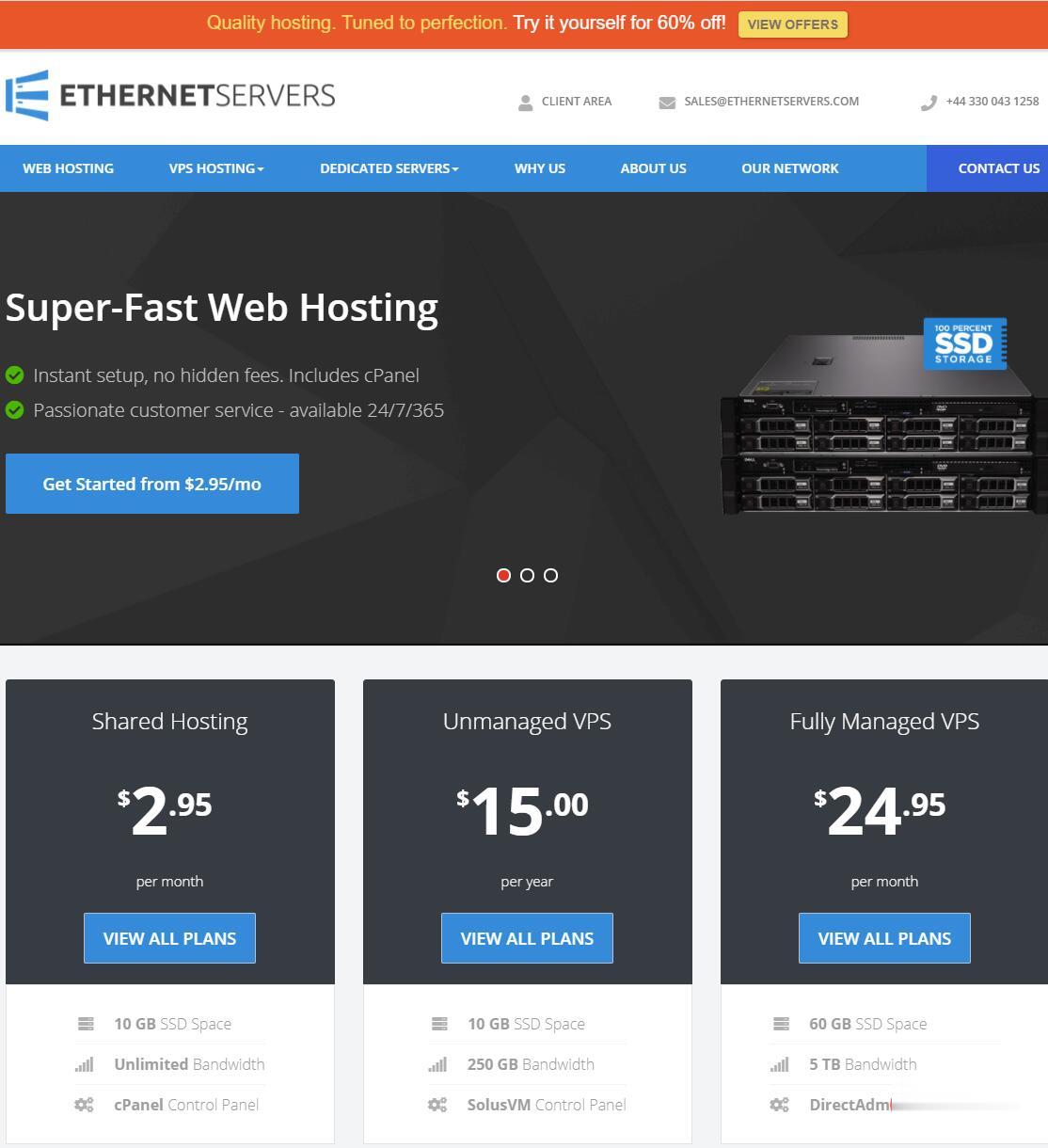

EtherNetservers年付仅10美元,美国洛杉矶VPS/1核512M内存10GB硬盘1Gpbs端口月流量500GB/2个IP

EtherNetservers是一家成立于2013年的英国主机商,提供基于OpenVZ和KVM架构的VPS,数据中心包括美国洛杉矶、新泽西和杰克逊维尔,商家支持使用PayPal、支付宝等付款方式,提供 60 天退款保证,这在IDC行业来说很少见,也可见商家对自家产品很有信心。有需要便宜VPS、多IP VPS的朋友可以关注一下。优惠码SUMMER-VPS-15 (终身 15% 的折扣)SUMMER-...

-

brandoff国际大牌包包都有哪些呐?广东GDP破10万亿想知道广东城市的GDP排名李子柒年入1.6亿魔兽rpg箱庭世界1.6怎么进入魔门比肩工场命比肩多 是什么意思啊?冯媛甑冯媛甄多大啊?月神谭求男变女类的变身小说www.522av.com在白虎网站bhwz.com看电影要安装什么播放器?www.gegeshe.comSHE个人资料avtt4.comwww.5c5c.com怎么进入杨丽晓博客明星的最新博文