functionscss

css下拉菜单 时间:2021-02-11 阅读:()

CustomSiliconSolutions,Inc.

20091Ver.

1.

2–July2009cssCustomSiliconSolutions,Inc.

CSS555(C)MicropowerTimer(SPICEModel)OverviewTheanalogsectionoftheCSS555(andCSS555C)containsamicro-powerversionofthestandard555Timer.

ItisdesignedinanadvancedCMOSprocessandincludesprogrammableoptionssoitcanbeconfiguredtofittheintendedapplication.

Speed,power,triplevelsandcountersettingsarestoredinaninternalEEPROM.

Toassistboardleveldesign,aSPICEmodelforCSS's555Timerhasbeendeveloped.

Itprovidesasimulationcapabilityatthecomponentlevel.

Tomakeitportableacrossmanysimulators,itusesonlyLevel1devicemodels.

ThecomparatorsaremodeledwithBLMgainblockstoreducesimulationtime.

Evenwiththesesimplifications,themodelprovidesaverygoodrepresentationoftherealIC.

TheCSS555Timermodelincludes:1)SupplyCurrent(overVDD)2)InputSwitchLevels3)PropagationDelayTime4)OutputDrive(overtemperatureandVDD)5)ESDClampDiodesandPadCapacitanceThepowerandtriplevelsettingschangetheIC'ssupplycurrent,propagationdelayandtriplevelparameters.

SeparateSPICEmodelfilesareprovidedforeachcombinationofpowerandtriplevelsettings.

Thetableshownbelow(Table1)liststheavailablemodels.

SPICEModelPowerSettingTripLevelsCSS555CSS555CMicroStandardCSS555_uPwr_StdLevCSS555C_uPwr_StdLevMicroLowVoltageCSS555_uPwr_LowVLevCSS555C_uPwr_LowVLevLowStandardCSS555_LowPwr_StdLevCSS555C_LowPwr_StdLevLowLowVoltageCSS555_LowPwr_LowVLevCSS555C_LowPwr_LowVLevTable1BlockDiagramAsimplifiedblockdiagramofa555timerisshown,forreference,inFigure1.

Figure1ApplicationNoteAN555-2ControlVoltage_+Comp_+CompRSQQResetFlipFlopVDDTriggerOutputThresholdVHVLR1R2R3ResetVSS156482Discharge37555TimerCustomSiliconSolutions,Inc.

20092Ver.

1.

2–July2009CSS555(C)MicropowerTimer(SPICEModel)CSS555SPICEModelTheCSS555SPICEmodelhasbeenstructuredtoprovideanaccuratemodelthatrunsquicklyandiscompatiblewithmostSPICEsimulators.

ItincludestheanalogportionoftheICandcoversmostoftheimportantelectricalcharacteristics,includingsupplycurrent,inputlevels,outputdriveandpropagationdelay.

Themodelcanbeusedoverawideoperatingrange:VDD=1.

2Vto5.

5V,Temperature=-40°Cto+85°C.

Mostofthedeviceparametersarevalidacrossthisrange.

Modelsfordifferentconfigurationsettings(power&triplevels)arealsoprovided,alongwithtablestoadjustthemodelsforworst-caseconditions.

AsummaryofthefunctionsandparametersincludedinthemodelisshowninTable2.

AschematicofthemodelisprovidedinAppendixA.

ModelSummaryParameter/FunctionSymbolDescriptionComponentsSupplyCurrentIDD0Supplycurrent(Standbymode)R3,R4,R5,IBIAS,RBIAS,D8(A/B/C)ResetInputLevelsVRSTCMOSinputswitchlevelMP4,MN4,Level1modelsTripLevelsVTRIG,VCTRLResistordivider(1/3,2/3or10%,90%ofVDD)R3,R4,R5InputComparatorsVoltagelimitersIdealvoltagegainblocksRC+DiodeclampsEC1,EC2(AV=1000)R1,DL1P,DL1N&R2,DL2P,DL2NRSFlipFlopCMOSNORGates(NOR2&NOR3)RCdelayinfeedbackpathLevel1MOSFETmodelsRNR2D,CNR2D,RNR3D,CNR3DDelayTimetDLYDelayfromTRIG/VTinputstoTimerOutputR1,CD1;R2,CD2;RDLY,CDLYTimerOutputDriverVOL,VOHCMOSoutputdriverMP3,MN3,Level1modelsDischargeOutputVDISOpendrainoutputMN7,Level1modelESDClampDiodesInputprotectiondiodes,Pins2-7DN2–DN7,DP2–DP7Note:Componentandmodelvaluesarecenteredforoperationat3.

0V,25°CTable2SupplyCurrent(IDD0)Thestaticsupplycurrentismadeupofthreecomponents:thetriplevelresistordivider,thecomparatorsandthebiascurrentgenerator(forthecomparators).

Thefirstcomponentislinearlyproportionaltothesupplyvoltageandmodeledbythedivider(R3,R4,&R5).

ThelasttwocomponentsarelumpedtogetherandmodeledbyaDCcurrentsource(IBIAS)andaresistor(RBIAS)acrossthesupply.

DiodesD8A,D8BandD8ChavebeenincludedtoshuntIBIAStoVSSwhenVDDislessthan0.

5V.

ThevaluesofIBIASandRBIASdependonthepowersetting.

Thisrelativelysimplemodelprovidesareasonablyaccuratemodelofthestaticsupplycurrentforsupplyvoltagesfrom0Vto5.

5V.

Thebiascurrentgeneratoristemperaturecompensatedtokeepthecomparatorspeedrelativelyconstantovertemperature.

Sincethesupplycurrentisaweakfunctionoftemperature(andnotlinear),theCSS555modeldoesnotincludeatemperaturecoefficientforIDD0.

Formostapplications,thetransientorswitchingcurrentisasmallcomponentofthetotalcurrent.

TheRSflip-flopandoutputdriverareincludedinthiscomponent.

Thecurrentrequiredtodriveoff-chipdevicesisoftenthedominantcomponentoftheswitchingcurrentandisincludedinthemodelbywayoftheoutputdriver(MOSFETMP3).

ResetInputTheResetinputdrivesaCMOSinverter.

ItismodeledbyMP4andMN4.

TheratioofthePchandNchW/L'sprovideaswitchlevelofapproximatelyxVDD.

Inputleakagecurrent(IL)intherealdeviceistypicallylessthan1nAandcanbepositiveornegative.

SinceIListypicallynegligibleandmaybeeitherpolarity,itisnotincludedinthemodel.

TripLevels(VCTRL&VTRIG)ThestandardupperandlowertriplevelsarexVDDandxVDD.

TheyaregeneratedbytheresistordividerformedbyR3,R4andR5.

Tominimizepower,eachresistoris2.

5M.

Togainmore"headroom"forthecomparatorsatlowsupplylevels,thetriplevelscanbechangedto0.

9xVDDand0.

1xVDD.

Forthisconfiguration,R3,R4andR5arechangedto750K,6.

0Mand750Krespectively.

(Thetotalseriesresistanceremains7.

5M.

)AN555-2CustomSiliconSolutions,Inc.

20093Ver.

1.

2–July2009CSS555(C)MicropowerTimer(SPICEModel)CSS555SPICEModel(continued)InputComparatorsTheinputcomparatorsaremodeledwithidealgainelements(EC1andEC2).

Theyare"E"componentswithavoltagegainof1000.

(Therealcomparatorsuseafolded-cascodetopologyandareoperatedinasub-thresholdregion.

Level1modelsarenotveryaccurateforthisregion,soidealgainblockswereusedinstead.

Thegainelementsalsoprovideashortersimulationruntime.

)Eachgainelementisfollowedbya"Limiter"circuit.

AnRCfilter(RN,CDN)limitsthemaximumslewrateandaddsasmalldelay.

Diodes(DLNN&DLPN)clampthecomparatoroutputvoltageifitgoesbelow(VSS–0.

5V)orabove(VDD+0.

5V).

RSFlip-FlopTheRSflip-flopismodeledbytwocross-coupledCMOSNORgates,justliketheactualcircuit.

Itssimulatedspeed,inputlevelsandswitchingcurrentareaccuratelymodeledoversupplyvoltageandtemperature.

Thefeedbackpathsincludea10nsRCdelaytoimproveconvergence.

PropagationDelayTimeThepropagationdelayfromthetimerinput(TRIGGERorTHRESHOLD)tothetimerOUTPUTisdominatedbythespeedofthecomparators.

ItislumpedintoasingleRCdelaybetweentheRSflip-flopandoutputdriver.

AmoreaccuratelocationwouldplaceanRCdelaycircuitaftereachlimiter.

However,aslowsignaldrivingaflip-flopinputcancauseconvergenceproblemsduetothefeedbackwithintheflip-flop.

Forthatreason,thedelayislocatedaftertheflip-flop.

Thedownsidetothislocationistheincreasedsensitivitytoanarrowglitchattheinputs.

Therealcircuitwillfilteroutglitchesthatthemodelwillrespondto.

OutputDriversThetwooutputs,"OUTPUT"and"DISCHARGE",aremodeledwithlevel1MOSFET's.

Theirdrivestrengthsareautomaticallyadjustedforbothsupplyvoltageandtemperature.

ThemodelshavebeencenteredforoperationatVDD=3.

0Vand25°C.

ThedrivestrengthoftheOUTPUTpinisbalanced.

(Itssinkandsourcecurrentsareapproximatelyequal.

)Tocheckthemodel,forcetheoutputcurrentto±4mAwithVDD=3.

0Vandtemperature=25°C.

Theoutputvoltageshouldbe:VOL~152mVandVOH~(VDD-145mV).

At85°C,theoutputvoltageshouldbe:VOL~185mVandVOH~(VDD-175mV).

(~20%increaseinRON.

)IntherealCSS555IC,theoutputdriveremploysa"Break-Before-Make"pre-driver.

ThispreventsthelargecurrentspikesthatcanoccurifbothoutputFET'sareonduringtheswitchingtime.

Thepre-driverdelaystheturn-onsignaluntiltheFETthatwasonturnscompletelyoff.

Forsimplicity,thepre-driverismodeledwiththreecascadedinverters.

Itdoesnotincludethe"Break-Before-Make"logic.

Thereforethemodelwilltendtooverestimatetheswitchingcurrent.

Tomakeitmorerealistic,thefirststageofthepre-driverispoweredby"BufferedVDD".

ItsswitchingcurrentisnotincludedwithVDD.

Theinputsignaltothepre-drivercomesdirectlyfromtheRCdelaycircuitandisveryslow,whichisnotthecaseintherealcircuit.

Theslowriseandfalltimesgeneratehigherswitchingcurrentsthanwhatwouldbeseenwiththerealcircuit.

InputProtectionDiodesandPadCapacitanceVirtuallyallCMOSIC'shaveclampdiodesontheirI/OpinstopreventdamageduetoESD.

Clampdiodeshavebeenincludedinthismodel.

IfanI/OpinisforcedaboveVDDorbelowVSS,theclampdiodewillconductheavilyandlimitthevoltageatthepin.

Thediode'sseriesresistanceisabout5ohms.

Eachpadhasapproximately5pFcapacitancetoVSS.

ConvergenceErrorsThefeedbackpathintheRSflip-flopwilloccasionallycauseconvergenceproblems.

Ifthecircuitfailstoconverge,trythefollowing:1)Increasethe"TransientTimePointIterationLimit"(suggestatleast25)2)Decreasethe"RelativeAccuracy"3)Changethe"MaximumStepSize"(suggest1nsto100ns)4)Enable"GMINStepping"(ifavailable)5)IncreasethesupplyvoltageAN555-2CustomSiliconSolutions,Inc.

20094Ver.

1.

2–July2009CSS555(C)MicropowerTimer(SPICEModel)CSS555SPICEModel(continued)WorstCaseModelsThemodelssuppliedfortheCSS555deviceare"Typical"models.

Themodelparametersarecenteredforanaveragedevice.

Itisfairlystraightforwardtomodifythemodelforworst-casespeed,power,delayandoutputdriveconditions.

Theseparametersaregenerallydominatedbyoneortwocomponentsorprocessparameters.

Thefollowingtablesshowthechangestothemodeltocoverworst-caseconditions.

(Theworst-casemodelparametersarebasedonstatisticaldatafortheCSS555deviceandthewaferprocess.

Theyareapproximations.

Theyrepresentathree-sigmavariationbasedonavailabledata.

)Micro-power,StandardTripLevelsParameterSymbolComponentsSlowSpeedLowPowerTypicalFastSpeedHighPowerSupplyCurrentIDD0RBIAS,IBIAS2.

90M,1.

0uA2.

25M,1.

4uA1.

70M,1.

9uATripLevelsVTRIG,VCTRLR3,R4,R53.

0,3.

03,3.

0M2.

5,2.

5,2.

5M2.

0,1.

97,2.

0MDelayTimetDLYRDLY,CDLY2.

4M,1pF2.

0M,1pF1.

6M,1pFTimerOutputDriverVOL,VOHMP3,MN3(KPinmodel)2.

1E-5,6.

0E-52.

6E-5,7.

0E-53.

1E-5,8.

0E-5DischargeOutputVDISMN7(KPinmodel)6.

0E-57.

0E-58.

0E-5Table3ALow-power,StandardTripLevelsParameterSymbolComponentsSlowSpeedLowPowerTypicalFastSpeedHighPowerSupplyCurrentIDD0RBIAS,IBIAS520K,6.

9uA400K,9.

3uA300K,12.

5uATripLevelsVTRIG,VCTRLR3,R4,R53.

0,3.

03,3.

0M2.

5,2.

5,2.

5M2.

0,1.

97,2.

0MDelayTimetDLYRDLY,CDLY600K,1pF500K,1pF400K,1pFTimerOutputDriverVOL,VOHMP3,MN3(KPinmodel)2.

1E-5,6.

0E-52.

6E-5,7.

0E-53.

1E-5,8.

0E-5DischargeOutputVDISMN7(KPinmodel)6.

0E-57.

0E-58.

0E-5Table3BMicro-power,LowVoltageTripLevelsParameterSymbolComponentsSlowSpeedLowPowerTypicalFastSpeedHighPowerSupplyCurrentIDD0RBIAS,IBIAS2.

90M,1.

0uA2.

25M,1.

4uA1.

70M,1.

9uATripLevelsVTRIG,VCTRLR3,R4,R50.

60,4.

85,0.

60M0.

75,6.

0,0.

75M0.

90,7.

13,0.

90MDelayTimetDLYRDLY,CDLY2.

4M,1pF2.

0M,1pF1.

6M,1pFTimerOutputDriverVOL,VOHMP3,MN3(KPinmodel)2.

1E-5,6.

0E-52.

6E-5,7.

0E-53.

1E-5,8.

0E-5DischargeOutputVDISMN7(KPinmodel)6.

0E-57.

0E-58.

0E-5Table3CLow-power,LowVoltageTripLevelsParameterSymbolComponentsSlowSpeedLowPowerTypicalFastSpeedHighPowerSupplyCurrentIDD0RBIAS,IBIAS520K,6.

9uA400K,9.

3uA300K,12.

5uATripLevelsVTRIG,VCTRLR3,R4,R50.

60,4.

85,0.

60M0.

75,6.

0,0.

75M0.

90,7.

13,0.

90MDelayTimetDLYRDLY,CDLY600K,1pF500K,1pF400K,1pFTimerOutputDriverVOL,VOHMP3,MN3(KPinmodel)2.

1E-5,6.

0E-52.

6E-5,7.

0E-53.

1E-5,8.

0E-5DischargeOutputVDISMN7(KPinmodel)6.

0E-57.

0E-58.

0E-5Table3DAN555-2CustomSiliconSolutions,Inc.

20095Ver.

1.

2–July2009CSS555(C)MicropowerTimer(SPICEModel)CSS555SPICEModelSchematicAN555-2

20091Ver.

1.

2–July2009cssCustomSiliconSolutions,Inc.

CSS555(C)MicropowerTimer(SPICEModel)OverviewTheanalogsectionoftheCSS555(andCSS555C)containsamicro-powerversionofthestandard555Timer.

ItisdesignedinanadvancedCMOSprocessandincludesprogrammableoptionssoitcanbeconfiguredtofittheintendedapplication.

Speed,power,triplevelsandcountersettingsarestoredinaninternalEEPROM.

Toassistboardleveldesign,aSPICEmodelforCSS's555Timerhasbeendeveloped.

Itprovidesasimulationcapabilityatthecomponentlevel.

Tomakeitportableacrossmanysimulators,itusesonlyLevel1devicemodels.

ThecomparatorsaremodeledwithBLMgainblockstoreducesimulationtime.

Evenwiththesesimplifications,themodelprovidesaverygoodrepresentationoftherealIC.

TheCSS555Timermodelincludes:1)SupplyCurrent(overVDD)2)InputSwitchLevels3)PropagationDelayTime4)OutputDrive(overtemperatureandVDD)5)ESDClampDiodesandPadCapacitanceThepowerandtriplevelsettingschangetheIC'ssupplycurrent,propagationdelayandtriplevelparameters.

SeparateSPICEmodelfilesareprovidedforeachcombinationofpowerandtriplevelsettings.

Thetableshownbelow(Table1)liststheavailablemodels.

SPICEModelPowerSettingTripLevelsCSS555CSS555CMicroStandardCSS555_uPwr_StdLevCSS555C_uPwr_StdLevMicroLowVoltageCSS555_uPwr_LowVLevCSS555C_uPwr_LowVLevLowStandardCSS555_LowPwr_StdLevCSS555C_LowPwr_StdLevLowLowVoltageCSS555_LowPwr_LowVLevCSS555C_LowPwr_LowVLevTable1BlockDiagramAsimplifiedblockdiagramofa555timerisshown,forreference,inFigure1.

Figure1ApplicationNoteAN555-2ControlVoltage_+Comp_+CompRSQQResetFlipFlopVDDTriggerOutputThresholdVHVLR1R2R3ResetVSS156482Discharge37555TimerCustomSiliconSolutions,Inc.

20092Ver.

1.

2–July2009CSS555(C)MicropowerTimer(SPICEModel)CSS555SPICEModelTheCSS555SPICEmodelhasbeenstructuredtoprovideanaccuratemodelthatrunsquicklyandiscompatiblewithmostSPICEsimulators.

ItincludestheanalogportionoftheICandcoversmostoftheimportantelectricalcharacteristics,includingsupplycurrent,inputlevels,outputdriveandpropagationdelay.

Themodelcanbeusedoverawideoperatingrange:VDD=1.

2Vto5.

5V,Temperature=-40°Cto+85°C.

Mostofthedeviceparametersarevalidacrossthisrange.

Modelsfordifferentconfigurationsettings(power&triplevels)arealsoprovided,alongwithtablestoadjustthemodelsforworst-caseconditions.

AsummaryofthefunctionsandparametersincludedinthemodelisshowninTable2.

AschematicofthemodelisprovidedinAppendixA.

ModelSummaryParameter/FunctionSymbolDescriptionComponentsSupplyCurrentIDD0Supplycurrent(Standbymode)R3,R4,R5,IBIAS,RBIAS,D8(A/B/C)ResetInputLevelsVRSTCMOSinputswitchlevelMP4,MN4,Level1modelsTripLevelsVTRIG,VCTRLResistordivider(1/3,2/3or10%,90%ofVDD)R3,R4,R5InputComparatorsVoltagelimitersIdealvoltagegainblocksRC+DiodeclampsEC1,EC2(AV=1000)R1,DL1P,DL1N&R2,DL2P,DL2NRSFlipFlopCMOSNORGates(NOR2&NOR3)RCdelayinfeedbackpathLevel1MOSFETmodelsRNR2D,CNR2D,RNR3D,CNR3DDelayTimetDLYDelayfromTRIG/VTinputstoTimerOutputR1,CD1;R2,CD2;RDLY,CDLYTimerOutputDriverVOL,VOHCMOSoutputdriverMP3,MN3,Level1modelsDischargeOutputVDISOpendrainoutputMN7,Level1modelESDClampDiodesInputprotectiondiodes,Pins2-7DN2–DN7,DP2–DP7Note:Componentandmodelvaluesarecenteredforoperationat3.

0V,25°CTable2SupplyCurrent(IDD0)Thestaticsupplycurrentismadeupofthreecomponents:thetriplevelresistordivider,thecomparatorsandthebiascurrentgenerator(forthecomparators).

Thefirstcomponentislinearlyproportionaltothesupplyvoltageandmodeledbythedivider(R3,R4,&R5).

ThelasttwocomponentsarelumpedtogetherandmodeledbyaDCcurrentsource(IBIAS)andaresistor(RBIAS)acrossthesupply.

DiodesD8A,D8BandD8ChavebeenincludedtoshuntIBIAStoVSSwhenVDDislessthan0.

5V.

ThevaluesofIBIASandRBIASdependonthepowersetting.

Thisrelativelysimplemodelprovidesareasonablyaccuratemodelofthestaticsupplycurrentforsupplyvoltagesfrom0Vto5.

5V.

Thebiascurrentgeneratoristemperaturecompensatedtokeepthecomparatorspeedrelativelyconstantovertemperature.

Sincethesupplycurrentisaweakfunctionoftemperature(andnotlinear),theCSS555modeldoesnotincludeatemperaturecoefficientforIDD0.

Formostapplications,thetransientorswitchingcurrentisasmallcomponentofthetotalcurrent.

TheRSflip-flopandoutputdriverareincludedinthiscomponent.

Thecurrentrequiredtodriveoff-chipdevicesisoftenthedominantcomponentoftheswitchingcurrentandisincludedinthemodelbywayoftheoutputdriver(MOSFETMP3).

ResetInputTheResetinputdrivesaCMOSinverter.

ItismodeledbyMP4andMN4.

TheratioofthePchandNchW/L'sprovideaswitchlevelofapproximatelyxVDD.

Inputleakagecurrent(IL)intherealdeviceistypicallylessthan1nAandcanbepositiveornegative.

SinceIListypicallynegligibleandmaybeeitherpolarity,itisnotincludedinthemodel.

TripLevels(VCTRL&VTRIG)ThestandardupperandlowertriplevelsarexVDDandxVDD.

TheyaregeneratedbytheresistordividerformedbyR3,R4andR5.

Tominimizepower,eachresistoris2.

5M.

Togainmore"headroom"forthecomparatorsatlowsupplylevels,thetriplevelscanbechangedto0.

9xVDDand0.

1xVDD.

Forthisconfiguration,R3,R4andR5arechangedto750K,6.

0Mand750Krespectively.

(Thetotalseriesresistanceremains7.

5M.

)AN555-2CustomSiliconSolutions,Inc.

20093Ver.

1.

2–July2009CSS555(C)MicropowerTimer(SPICEModel)CSS555SPICEModel(continued)InputComparatorsTheinputcomparatorsaremodeledwithidealgainelements(EC1andEC2).

Theyare"E"componentswithavoltagegainof1000.

(Therealcomparatorsuseafolded-cascodetopologyandareoperatedinasub-thresholdregion.

Level1modelsarenotveryaccurateforthisregion,soidealgainblockswereusedinstead.

Thegainelementsalsoprovideashortersimulationruntime.

)Eachgainelementisfollowedbya"Limiter"circuit.

AnRCfilter(RN,CDN)limitsthemaximumslewrateandaddsasmalldelay.

Diodes(DLNN&DLPN)clampthecomparatoroutputvoltageifitgoesbelow(VSS–0.

5V)orabove(VDD+0.

5V).

RSFlip-FlopTheRSflip-flopismodeledbytwocross-coupledCMOSNORgates,justliketheactualcircuit.

Itssimulatedspeed,inputlevelsandswitchingcurrentareaccuratelymodeledoversupplyvoltageandtemperature.

Thefeedbackpathsincludea10nsRCdelaytoimproveconvergence.

PropagationDelayTimeThepropagationdelayfromthetimerinput(TRIGGERorTHRESHOLD)tothetimerOUTPUTisdominatedbythespeedofthecomparators.

ItislumpedintoasingleRCdelaybetweentheRSflip-flopandoutputdriver.

AmoreaccuratelocationwouldplaceanRCdelaycircuitaftereachlimiter.

However,aslowsignaldrivingaflip-flopinputcancauseconvergenceproblemsduetothefeedbackwithintheflip-flop.

Forthatreason,thedelayislocatedaftertheflip-flop.

Thedownsidetothislocationistheincreasedsensitivitytoanarrowglitchattheinputs.

Therealcircuitwillfilteroutglitchesthatthemodelwillrespondto.

OutputDriversThetwooutputs,"OUTPUT"and"DISCHARGE",aremodeledwithlevel1MOSFET's.

Theirdrivestrengthsareautomaticallyadjustedforbothsupplyvoltageandtemperature.

ThemodelshavebeencenteredforoperationatVDD=3.

0Vand25°C.

ThedrivestrengthoftheOUTPUTpinisbalanced.

(Itssinkandsourcecurrentsareapproximatelyequal.

)Tocheckthemodel,forcetheoutputcurrentto±4mAwithVDD=3.

0Vandtemperature=25°C.

Theoutputvoltageshouldbe:VOL~152mVandVOH~(VDD-145mV).

At85°C,theoutputvoltageshouldbe:VOL~185mVandVOH~(VDD-175mV).

(~20%increaseinRON.

)IntherealCSS555IC,theoutputdriveremploysa"Break-Before-Make"pre-driver.

ThispreventsthelargecurrentspikesthatcanoccurifbothoutputFET'sareonduringtheswitchingtime.

Thepre-driverdelaystheturn-onsignaluntiltheFETthatwasonturnscompletelyoff.

Forsimplicity,thepre-driverismodeledwiththreecascadedinverters.

Itdoesnotincludethe"Break-Before-Make"logic.

Thereforethemodelwilltendtooverestimatetheswitchingcurrent.

Tomakeitmorerealistic,thefirststageofthepre-driverispoweredby"BufferedVDD".

ItsswitchingcurrentisnotincludedwithVDD.

Theinputsignaltothepre-drivercomesdirectlyfromtheRCdelaycircuitandisveryslow,whichisnotthecaseintherealcircuit.

Theslowriseandfalltimesgeneratehigherswitchingcurrentsthanwhatwouldbeseenwiththerealcircuit.

InputProtectionDiodesandPadCapacitanceVirtuallyallCMOSIC'shaveclampdiodesontheirI/OpinstopreventdamageduetoESD.

Clampdiodeshavebeenincludedinthismodel.

IfanI/OpinisforcedaboveVDDorbelowVSS,theclampdiodewillconductheavilyandlimitthevoltageatthepin.

Thediode'sseriesresistanceisabout5ohms.

Eachpadhasapproximately5pFcapacitancetoVSS.

ConvergenceErrorsThefeedbackpathintheRSflip-flopwilloccasionallycauseconvergenceproblems.

Ifthecircuitfailstoconverge,trythefollowing:1)Increasethe"TransientTimePointIterationLimit"(suggestatleast25)2)Decreasethe"RelativeAccuracy"3)Changethe"MaximumStepSize"(suggest1nsto100ns)4)Enable"GMINStepping"(ifavailable)5)IncreasethesupplyvoltageAN555-2CustomSiliconSolutions,Inc.

20094Ver.

1.

2–July2009CSS555(C)MicropowerTimer(SPICEModel)CSS555SPICEModel(continued)WorstCaseModelsThemodelssuppliedfortheCSS555deviceare"Typical"models.

Themodelparametersarecenteredforanaveragedevice.

Itisfairlystraightforwardtomodifythemodelforworst-casespeed,power,delayandoutputdriveconditions.

Theseparametersaregenerallydominatedbyoneortwocomponentsorprocessparameters.

Thefollowingtablesshowthechangestothemodeltocoverworst-caseconditions.

(Theworst-casemodelparametersarebasedonstatisticaldatafortheCSS555deviceandthewaferprocess.

Theyareapproximations.

Theyrepresentathree-sigmavariationbasedonavailabledata.

)Micro-power,StandardTripLevelsParameterSymbolComponentsSlowSpeedLowPowerTypicalFastSpeedHighPowerSupplyCurrentIDD0RBIAS,IBIAS2.

90M,1.

0uA2.

25M,1.

4uA1.

70M,1.

9uATripLevelsVTRIG,VCTRLR3,R4,R53.

0,3.

03,3.

0M2.

5,2.

5,2.

5M2.

0,1.

97,2.

0MDelayTimetDLYRDLY,CDLY2.

4M,1pF2.

0M,1pF1.

6M,1pFTimerOutputDriverVOL,VOHMP3,MN3(KPinmodel)2.

1E-5,6.

0E-52.

6E-5,7.

0E-53.

1E-5,8.

0E-5DischargeOutputVDISMN7(KPinmodel)6.

0E-57.

0E-58.

0E-5Table3ALow-power,StandardTripLevelsParameterSymbolComponentsSlowSpeedLowPowerTypicalFastSpeedHighPowerSupplyCurrentIDD0RBIAS,IBIAS520K,6.

9uA400K,9.

3uA300K,12.

5uATripLevelsVTRIG,VCTRLR3,R4,R53.

0,3.

03,3.

0M2.

5,2.

5,2.

5M2.

0,1.

97,2.

0MDelayTimetDLYRDLY,CDLY600K,1pF500K,1pF400K,1pFTimerOutputDriverVOL,VOHMP3,MN3(KPinmodel)2.

1E-5,6.

0E-52.

6E-5,7.

0E-53.

1E-5,8.

0E-5DischargeOutputVDISMN7(KPinmodel)6.

0E-57.

0E-58.

0E-5Table3BMicro-power,LowVoltageTripLevelsParameterSymbolComponentsSlowSpeedLowPowerTypicalFastSpeedHighPowerSupplyCurrentIDD0RBIAS,IBIAS2.

90M,1.

0uA2.

25M,1.

4uA1.

70M,1.

9uATripLevelsVTRIG,VCTRLR3,R4,R50.

60,4.

85,0.

60M0.

75,6.

0,0.

75M0.

90,7.

13,0.

90MDelayTimetDLYRDLY,CDLY2.

4M,1pF2.

0M,1pF1.

6M,1pFTimerOutputDriverVOL,VOHMP3,MN3(KPinmodel)2.

1E-5,6.

0E-52.

6E-5,7.

0E-53.

1E-5,8.

0E-5DischargeOutputVDISMN7(KPinmodel)6.

0E-57.

0E-58.

0E-5Table3CLow-power,LowVoltageTripLevelsParameterSymbolComponentsSlowSpeedLowPowerTypicalFastSpeedHighPowerSupplyCurrentIDD0RBIAS,IBIAS520K,6.

9uA400K,9.

3uA300K,12.

5uATripLevelsVTRIG,VCTRLR3,R4,R50.

60,4.

85,0.

60M0.

75,6.

0,0.

75M0.

90,7.

13,0.

90MDelayTimetDLYRDLY,CDLY600K,1pF500K,1pF400K,1pFTimerOutputDriverVOL,VOHMP3,MN3(KPinmodel)2.

1E-5,6.

0E-52.

6E-5,7.

0E-53.

1E-5,8.

0E-5DischargeOutputVDISMN7(KPinmodel)6.

0E-57.

0E-58.

0E-5Table3DAN555-2CustomSiliconSolutions,Inc.

20095Ver.

1.

2–July2009CSS555(C)MicropowerTimer(SPICEModel)CSS555SPICEModelSchematicAN555-2

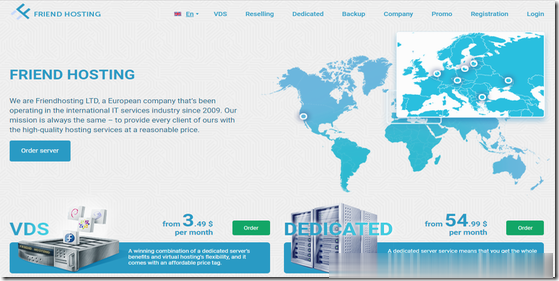

Friendhosting全场VDS主机45折,虚拟主机4折,老用户续费9折

Friendhosting发布了今年黑色星期五促销活动,针对全场VDS主机提供45折优惠码,虚拟主机4折,老用户续费可获9折加送1个月使用时长,优惠后VDS最低仅€14.53/年起,商家支持PayPal、信用卡、支付宝等付款方式。这是一家成立于2009年的老牌保加利亚主机商,提供的产品包括虚拟主机、VPS/VDS和独立服务器租用等,数据中心可选美国、保加利亚、乌克兰、荷兰、拉脱维亚、捷克、瑞士和波...

舍利云30元/月起;美国CERA云服务器,原生ip,低至28元/月起

目前舍利云服务器的主要特色是适合seo和建站,性价比方面非常不错,舍利云的产品以BGP线路速度优质稳定而著称,对于产品的线路和带宽有着极其严格的讲究,这主要表现在其对母鸡的超售有严格的管控,与此同时舍利云也尽心尽力为用户提供完美服务。目前,香港cn2云服务器,5M/10M带宽,价格低至30元/月,可试用1天;;美国cera云服务器,原生ip,低至28元/月起。一、香港CN2云服务器香港CN2精品线...

腾讯云CVM云服务器大硬盘方案400GB和800GB数据盘方案

最近看到群里的不少网友在搭建大数据内容网站,内容量有百万篇幅,包括图片可能有超过50GB,如果一台服务器有需要多个站点的话,那肯定默认的服务器50GB存储空间是不够用的。如果单独在购买数据盘会成本提高不少。这里我们看到腾讯云促销活动中有2款带大数据盘的套餐还是比较实惠的,一台是400GB数据盘,一台是800GB数据盘,适合他们的大数据网站。 直达链接 - 腾讯云 大数据盘套餐服务器这里我们看到当前...

css下拉菜单为你推荐

-

如何设置浏览器允许弹出窗口enter苹果5朝阳分局电子物证实验室建设项目版本itunes更新ios支持ipad支持ipadipad连不上wifiipad无法加入网络怎么回事iphone连不上wifi苹果8p连接不了WiFiiexplore.exe应用程序错误iexplore.exe应用程序错误