batterywww.22hhh.com

www.22hhh.com 时间:2021-04-07 阅读:()

CDC3S04www.

ti.

comSCAS883C–OCTOBER2009–REVISEDAUGUST2012QuadSine-WaveClockBufferWithLDOCheckforSamples:CDC3S041FEATURESDESCRIPTIONTheCDC3S04isafour-channellow-powerlow-jitter1:4Low-JitterClockBuffersine-waveclockbuffer.

ItcanbeusedtobufferaSingle-EndedSine-WaveClockInputandsinglemasterclocktomultipleperipherals.

ThefourOutputssine-waveoutputs(CLK1–CLK4)aredesignedforUltralowPhaseNoiseandStandbyCurrentminimalchannel-to-channelskewandultralowadditiveoutputjitter.

IndividualClockRequestInputsforEachOutputEachoutputhasitsownclockrequestinputswhichenablesthededicatedclockoutput.

TheseclockOn-ChipLow-DropoutOutput(LDO)forLow-requestsareactive-high(canalsobechangedtobeNoiseTCXOSupplyactive-lowviaI2C),andanoutputsignalisgeneratedSerialI2CInterface(CompatibleWithHigh-thatcanbesentbacktothemasterclocktorequestSpeedMode,3.

4Mbit/s)theclock(MCLK_REQ).

MCKL_REQisanopen-1.

8-VDevicePowerSupplysourceoutputandsupportsthewired-ORfunction(defaultmode).

Itneedsanexternalpulldownresistor.

WideTemperatureRange,–40°Cto85°CMCKL_REQcanbechangedtowired-ANDorpush-ESDProtection:2KVHBM,750VCDM,andpullfunctionalityviaI2C.

100VMMTheCDC3S04alsoprovidesanI2Cinterface(Hs-Small20-PinChip-ScalePackage:0.

4-mmmode)thatcanbeusedtoenableordisablethePitchWCSP(1.

6mm*2mm)outputs,selectthepolarityoftheREQinputs,andallowcontrolofinternaldecoding.

APPLICATIONSTheCDC3S04featuresanon-chiphigh-performanceCellularPhonesLDOthatacceptsvoltagesfrom2.

3Vto5.

5VandSmartPhonesoutputsa1.

8-Vsupply.

This1.

8-Vsupplycanbeusedtopoweranexternal1.

8-VTCXO.

ItcanbeMobileHandsetsenabledordisabledforpowersavingattheTCXO.

PortableSystemsWirelessModemsIncludingGPS,WLAN,W-BT,D-TV,DVB-H,FMRadio,WiMAX,andSystemClock1Pleasebeawarethatanimportantnoticeconcerningavailability,standardwarranty,anduseincriticalapplicationsofTexasInstrumentssemiconductorproductsanddisclaimerstheretoappearsattheendofthisdatasheet.

PRODUCTIONDATAinformationiscurrentasofpublicationdate.

Copyright2009–2012,TexasInstrumentsIncorporatedProductsconformtospecificationsperthetermsoftheTexasInstrumentsstandardwarranty.

Productionprocessingdoesnotnecessarilyincludetestingofallparameters.

CDC3S04SCAS883C–OCTOBER2009–REVISEDAUGUST2012www.

ti.

comThisintegratedcircuitcanbedamagedbyESD.

TexasInstrumentsrecommendsthatallintegratedcircuitsbehandledwithappropriateprecautions.

Failuretoobserveproperhandlingandinstallationprocedurescancausedamage.

ESDdamagecanrangefromsubtleperformancedegradationtocompletedevicefailure.

Precisionintegratedcircuitsmaybemoresusceptibletodamagebecauseverysmallparametricchangescouldcausethedevicenottomeetitspublishedspecifications.

DESCRIPTION(CONTINUED)AlowsignalattheRESETinputswitchestheoutputsCLK1andCLK4intothedefaultstate.

Inthisconfiguration,CLK1andCLK4areON(seeTable1);theremainingdevicefunctionisnotaffected.

Also,theRESETinputprovidesaglitchfilterwhichrejectsspikesoftypical300nsontheRESETlinetopreservefalsereset.

Acompletedeviceresettothedefaultconditioncanbeinitiatedbyapower-upcycleofVDD_DIG.

TheCDC3S04operatesfromtwo1.

8-Vsupplies.

Thereisacoresupply(VDD_DIG/GND_DIG)forthecorelogicandalow-noiseanalogsupply(VDD_ANA/GND_ANA)forthesine-waveoutputs.

TheCDC3S04isdesignedforsequence-lesspowerup.

Bothsupplyvoltagesmaybeappliedinanyorder.

TheCDC3S04isofferedina0.

4-mmpitchWCSPpackage(1.

6mm*2mm)andisoptimizedforlowstandbycurrent(0.

5A).

Itischaracterizedforoperationfrom–40°Cto85°C.

DEVICEINFORMATIONPINFUNCTIONSNAMEBALLNO.

TYPEFUNCTIONADR_A0D4InputSelectableaddressbitA0ofslave-addressregister;internal500-kΩpulldownresistorCLK1A4OutputClockoutput1CLK2A2OutputClockoutput2CLK3C4OutputClockoutput3CLK4C2OutputClockoutput4GND_ANAB4GroundGroundforsine-wavebufferGND_DIGD2GroundGroundforcorelogicMCLK_INB1InputMasterclockinputMCLK_REClockrequesttothemasterclocksource;active-high;open-sourceoutputforwired-ORD3OutputQconnection(defaultcondition).

Canbechangedtopush-pulloutputorwired-ANDoutputviaI2C.

REQ1A3InputClockrequestfromperipheral1;internal500-kΩpulldownresistorREQ2A1InputClockrequestfromperipheral2;internal500-kΩpulldownresistorREQ3C3InputClockrequestfromperipheral3;internal500-kΩpulldownresistorREQ4C1InputClockrequestfromperipheral4;internal500-kΩpulldownresistorPeripheralresetsignalprovidedbyapplicationprocessor.

Thesignalisactive-lowandswitchesRESETB2InputCLK1andCLK4outputstoON(seeTable1).

On-chipLDOisenabled.

Internal1-MΩpullupresistorand300-ns(typ)glitchfilter.

SCLHE4InputI2Cclockinput–Hs-mode.

Internal1-MΩpullupresistorSDAHE3Input/outputI2Cdatainput/output–Hs-mode.

Internal1-MΩpullupresistorVBATE2PowerSupplypintointernalLDOVDD_ANAB3Power1.

8-Vpowersupplyforsine-wavebuffer1.

8-Vpowersupplyforcorelogic.

PowerupofVDD_DIGresetsthewholedevicetothedefaultVDD_DIGD1Powercondition.

1.

8-VsupplyforexternalTCXO;LDOisenabledifRESET(defaultmode)orREQxisactive.

VLDOE1OutputLDOisnotenabledifonlyVBATison.

2SubmitDocumentationFeedbackCopyright2009–2012,TexasInstrumentsIncorporatedProductFolderLinks:CDC3S04CDC3S04www.

ti.

comSCAS883C–OCTOBER2009–REVISEDAUGUST2012FUNCTIONSELECTIONTABLESTable1.

ResetandRequest(REQx)ConditionsforClockOutputs(1)RESET(2)PRIORITYBIT(3)CLK1CLK2CLK3CLK40ControlledbyREQ2ControlledbyREQ30OnOn1ControlledbyREQ2INTControlledbyREQ3INT0ControlledbyREQ1ControlledbyREQ2ControlledbyREQ3ControlledbyREQ411ControlledbyREQ1INTControlledbyREQ2INTControlledbyREQ3INTControlledbyREQ4INT(1)Shadedcellsshowthedefaultsettingafterpowerup.

(2)RESETresetsREQ1PRIO/REQ4PRIOandREQ1INT/REQ4INTbitstotheirdefaultvalues(CLK1/4isON)butdoesnotchangetheremaininginternalSWbits.

DuringRESET,anyI2CoperationisblockeduntilRESETisdeactivated.

Aminimumpulsedurationof500nsmustbeappliedtoactivateRESET(theinternalglitch-filtersuppressesspikesoftypical300ns).

(3)Prioritybitdefinesiftheexternalcontrolpins(HWcontrolled)ortheSWbits(SWcontrolled)havepriority.

Itcanbesetintheconfigurationregister,Byte2,Bits0–3.

Table2.

RequestSignalConditionforClockOutputs(1)REQxCLKxREQ-Signals(2)MCLK_REQLDO(3)(REQ1/2/3/4)(CLK1/2/3/4)Active-low0ClockHighOn1DisabledtohighLow(ifallREQxarehigh)Off(ifallREQxarehigh)0Disabledtohigh(4)Low(ifallREQxarelow)Off(ifallREQxarelow)Active-high1Clock(4)HighOn(1)Shadedcellsshowthedefaultsettingafterpowerup.

(2)PolarityofREQ1,REQ2,REQ3,andREQ4areregister-configurableviaI2C(seeTable3,Byte0,Bits0–3).

Defaultsettingisactive-high.

(3)TheLDOiscontrolledbyanon-chipdecoder,butcanalsobeSWcontrolled(seeTable3,Byte2,Bits4–5).

(4)CLK1andCLK4areONafterdevicepowerup(defaultcondition).

CLK2andCLK3arecontrolledbyexternalREQ2andREQ3,respectively.

POWERGROUPSNAMEDESCRIPTIONVBATSupplypinforLDOprovidedbymainbattery.

LDOisnotworkingifonlyVBATison.

1.

8-Vlow-dropoutputvoltageforexternalTCXO.

LDOisenabledifVBATandVDD_DIGareonandREQxorRESETisVLDOactive(seeTable2).

1.

8-VpowersupplyforcorelogicandI2Clogic.

VDD_DIGmustbesuppliedforcorrectdeviceoperation.

PowerupofVDD_DIGVDD_DIGresetsthewholedevicetothedefaultcondition.

1.

8-Vpowersupplyforsine-wavebuffers.

Forcorrectsine-wavebufferfunction,allthreepowersupplies(VBAT,VDD_DIGVDD_ANAandVDD_ANA)mustbeon.

But,VDD_ANAcanbeswitchedonandoffatanytime.

Ifoff,thesine-waveoutputsareswitchedtohigh-impedance.

POWER-UPSEQUENCETheCDC3S04isdesignedforsequence-lesspowerup.

VBAT,VDD_DIG,andVDD_ANAmaybeappliedinanyorder.

Recommendedpower-onsequenceisVBATfirst,followedbyVDD_DIGandVDD_ANA.

Recommendedpower-offsequenceisinreverseorder.

Copyright2009–2012,TexasInstrumentsIncorporatedSubmitDocumentationFeedback3ProductFolderLinks:CDC3S04CDC3S04SCAS883C–OCTOBER2009–REVISEDAUGUST2012www.

ti.

comABSOLUTEMAXIMUMRATINGSoveroperatingfree-airtemperaturerange(unlessotherwisenoted)(1)VALUEUNITVDD_ANASupplyvoltagerange–0.

5to2.

5VVDD_DIGVBATBatterysupplyvoltagerange–0.

5to6.

5VVIInputvoltagerange(2)(3)–0.

5toVDD+0.

5VVOOutputvoltagerange(2)(3)–0.

5toVDD+0.

5VVLDOOutputvoltagerange–0.

5toVBAT+0.

5VInputcurrent(VIVDD)±20mAIOContinuousoutputcurrent±20mAILDOContinuousoutputcurrent±20mATstgStoragetemperaturerange–65to150°C(1)Stressesbeyondthoselistedunderabsolutemaximumratingsmaycausepermanentdamagetothedevice.

Thesearestressratingsonlyandfunctionaloperationofthedeviceattheseoranyotherconditionsbeyondthoseindicatedunderrecommendedoperatingconditionsisnotimplied.

Exposuretoabsolute–maximum–ratedconditionsforextendedperiodsmayaffectdevicereliability.

(2)Theinputandoutputnegativevoltageratingsmaybeexceedediftheinputandoutputclamp-currentratingsareobserved.

(3)TheinputVIandoutputVOpositivevoltagesarelimitedtotheabsolutemaximumratingforVDD=2.

5V.

THERMALCHARACTERISTICSfor20-pinWCSP(YFF)(1)AIRFLOW20-PINPARAMETERUNIT(lfm)WCSP071TJAThermalresistance,junction-to-ambient20062°C/W40059TJCThermalresistance,junction-to-case–17.

5°C/WTJBThermalresistance,junction-to-board–20.

5°C/WTJMaximumjunctiontemperature–125°C(1)ThepackagethermalimpedanceiscalculatedinaccordancewithJESD51andJEDEC2S2P(high-kboard).

RECOMMENDEDOPERATINGCONDITIONSMINNOMMAXUNITVDD_ANADevicesupplyvoltage1.

651.

81.

95VVDD_DIGDevicesupplyvoltage1.

651.

81.

95VVIH0.

65VDD_DIGVInputvoltageADR_A0,REQx,RESETVIL0.

35VDD_DIGVVISSine-waveinputvoltage–MCLK_IN;ac-coupledamplitude0.

51.

2VPPCLSine-waveoutputload(1)1030pFCOUTLDOoutputcapacitance(stabilizetheinternalcontrolloop)0.

82.

2FTAOperatingfree-airtemperature–4085°C(1)10pFisthetypicalload-drivingcapability.

Thedrivecapabilitycanbeoptimizedfor30pFbytheI2Cregister(Byte3,Bits7–4).

4SubmitDocumentationFeedbackCopyright2009–2012,TexasInstrumentsIncorporatedProductFolderLinks:CDC3S04CDC3S04www.

ti.

comSCAS883C–OCTOBER2009–REVISEDAUGUST2012ELECTRICALCHARACTERISTICSoverrecommendedoperatingfree-airtemperaturerange(unlessotherwisenoted)PARAMETERTESTCONDITIONSMINTYPMAXUNITOVERALLPARAMETERVBAT=5.

5V;Off(noREQ)0.

10.

2VDD_ANA=1.

95V;Analogsupplycurrent(1)IDD_ANALDOison;VIS=1VPP;mA(seeFigure8throughFigure12)Peroutput22.

6fMCLK_IN=38.

4MHz;RL=10kΩ;CL=10pF(2)VBAT=5.

5V;VDD_DIG=1.

95V;VDD_ANA=off;DigitalsupplycurrentIDD_DIG(seeFigure8through0.

1mALDO=off;VIS=1Vpp;fMCLK_IN=38.

4Figure12)MHz;CL=10pF;RL=10kΩVBAT=5.

5V;VDD_DIG/VDD_ANA=1.

95V;Alloutputsdisabled(noinputclock;LDOISBStandbycurrentoff;noREQ;RESETisinactive;I2Cisin0.

510Aidlemode);includes1-MΩpullupatI2CandRESETfMCLK_INInputfrequencySinewave0.

0138.

452MHzWired-ORoutput;IOH=–2mA;VDD_DIG=1.

65V(SeeVDD_DIG–0.

45MCLK_REQhigh-leveloutputFigure3.

)VOHVvoltagePush-pulloutput;VDD_DIG=1.

65V,VDD_DIG–0.

45IOH=–2mAWired-ANDoutput;IOL=2mA0.

45VDD_DIG=1.

65VMCLK_REQlow-leveloutputVOLVvoltagePush-pulloutput;VDD_DIG=1.

65V,0.

45IOL=2mAVIKLVCMOSinputvoltageVDD_DIG=1.

65V;II=–18mA–1.

2VInputcurrentADR_A0,REQx6(500-kΩpulldown)IIHVI=VDD_DIG;VDD_DIG=1.

95VAInputcurrentRESET(1-MΩ2pullup)InputcurrentADR_A0,REQx–2(500-kΩpulldown)IILVI=0V;VDD_DIG=1.

95VAInputcurrentRESET(1-MΩ–3pullup)InputcapacitanceADR_A0,CIVI=0VorVDD_DIG3pFREQx,RESETSDAH/SCLHPARAMETER(Hs-Mode)SCLH/SDAHinputclampVIKVDD_DIG=1.

65V;II=–18mA–1.

2VvoltageIISCLH/SDAHinputcurrent0.

1VDD_DIG1MHzOutputvoltageVIS=0.

5VPP445490500mVPP10Hzto10MHz;fOUT=38.

4MHz0.

30.

6tjitadd(rms)Additivermsjitter(4)psRMS10kHzto10MHz;fOUT=38.

4MHz0.

10.

2Atoffset=1kHz–142–135AdditivephasenoiseatfOUT=pnaddAtoffset=10kHz–152–145dBc/Hz38.

4MHz(5)Atoffset=100kHz–157–150RINInputresistanceAtdclevel1215kΩCINInputcapacitancefMCLK_IN=38.

4MHz57pFELECTRICALCHARACTERISTICofLDO(COUT=0.

8to2.

7F)(6)VBATInputvoltagerange2.

35.

5VVLDOLDOoutputvoltage(7)2.

3V5V,lLOAD=5mA1.

721.

81.

9VMaximumlineregulation2.

3V5V,lLOAD=5mA0.

5%ΔVLDO03Vor5.

5V;Maximumloadregulation0.

5%TJ=25°CILOADLoadcurrentCOUT=0.

8Fto2.

7F05mAILCLLDOoutputcurrentlimitVLDO=0.

9*VLDO(TYP)1060mAILGNDLDOgroundpincurrent(8)VBAT=3.

6V;03V5V0.

2A100Hz60681kHz5562VBAT=2.

3V(formin)VBAT=2.

5V(fortyp)10kHz4552Power-supplyrejectionratioPSRRdBVLDO=1.

8V(ripplerejection)(seeFigure20)100kHz3340ILOAD=5mAVripple=0.

1Vpp1MHz374610MHz6067Outputnoisevoltage(seeBW=10Hzto100kHz;VLDO=1.

8V;VN30VRMSFigure21)ILOAD=5mA(4)Additivermsjitteristheintegratedrmsjitterthatthedeviceaddstothesignalchain.

Itiscalculatedby(5)Additivephasenoiseistheamountofphasenoisethatthedeviceaddstothesignalchain.

ItiscalculatedbyLadd(dB)=10log(100.

1Lout–100.

1Lin).

(6)MinimumCOUTshouldbe100nFtoallowforstableLDOoperation.

(7)LDOoutputvoltageincludesmaximumlineandloadregulation.

(8)LDOgroundpincurrentdoesnotchangeoverVBAT.

6SubmitDocumentationFeedbackCopyright2009–2012,TexasInstrumentsIncorporatedProductFolderLinks:CDC3S04CDC3S04www.

ti.

comSCAS883C–OCTOBER2009–REVISEDAUGUST2012TIMINGREQUIREMENTSoveroperatingfree-airtemperaturerange(unlessotherwisenoted)VLDO=1.

8V;CL=10pF;RL=10kΩPARAMETERTESTCONDITIONSMINTYP(1)MAXUNITTIMINGPARAMETERtPDPropagationdelaytimeMCLK_IN-to-CLKx;fMCLK_IN=38.

4MHz3nstLHREQx-to-MCLK_REQ(wired-OR,CL=15pF,Propagationdelaytime,low-to-high15nsRL=10kΩ);CLKxon-time–REQ-to-CLKx0.

30.

4sfMCLK_IN=38.

4MHz;VVDD_ANAison;CLKxon-time–RESET-to-CLKx(3)VIS=1V;VOS=–1dB(seeFigure5and0.

60.

8sFigure6)CLKxoff-time–REQ-to-CLKx25nstCLK(2)CLKxon-time–VDD_ANAto-CLKxfMCLK_IN=38.

4MHz;VIS=1V;2050sVOS=–1dB;measurementstartswhenVDD_ANAis90%of1.

7V(seeFigure7)PulsedurationofspikesthatmustbetSPsuppressedbytheinputfilterfor100nsRESET(3)tsk(o)Outputskew(4)fMCLK_IN=38.

4MHz;CLK1-to-CLK42550psLDOon-time(5)VLDO=1.

7V,ILDO=5mA,tLDO–REQ-to-LDO;100300s2.

3V5V;COUT=2.

7F–RESET-to-LDO(1)AlltypicalvaluesareatnominalVDD_ANAandVDD_DIG.

(2)CLKon-timeismeasuredwithvalidinputsignal(VIS=1Vpp).

IncaseaTXCOisused,theLDOandTCXOarealreadyon.

(3)Pulsesabove500nsareinterpretedasavalidresetsignal.

TotaltimefromRESET-to-CLKxisthesumoftSP+tCLK_/RESET.

(4)OutputskewiscalculatedasthegreaterofthedifferencebetweenthefastestandtheslowesttPLHorthedifferencebetweenthefastestandtheslowesttPHL.

(5)LDOoff-timedependsonthedischargetimeoftheR-Ccomponents(seeFigure4).

PARAMETERMINMAXUNITSDAH/SCLHTIMINGREQUIREMENTS,Hs-Mode(CBUS=100pFforeachI2Cline;seeFigure24andFigure25)fSCLHSCLHclockfrequency03.

4MHztsu(START)STARTsetuptime(SCLHhighbeforeSDAHlow)160nsth(START)STARTholdtime(SCLHlowafterSDAHlow)160nstLOWLowperiodoftheSCLHclock160nstHIGHHighperiodoftheSCLHclock60nsth(SDAH)SDAHholdtime(SDAHvalidafterSCLHlow)0(1)70nstsu(SDAH)SDAHsetuptime10nsSCLHrisetime1040nstrSDAHrisetime1080SCLHfalltime1040nstfSDAHfalltime1080tsu(STOP)STOPsetuptime160nsPulsedurationofspikesthatmustbesuppressedbytheinputfilterforSDAHandtSP010nsSCLH(1)AdevicemustinternallyprovideadataholdtimetobridgetheundefinedperiodbetweenVIHandVILofthefallingedgeoftheSCLHsignal.

AninputcircuitwithathresholdaslowaspossibleforthefallingedgeoftheSCLHsignalminimizesthisholdtime.

Copyright2009–2012,TexasInstrumentsIncorporatedSubmitDocumentationFeedback7ProductFolderLinks:CDC3S04CDC3S04SCAS883C–OCTOBER2009–REVISEDAUGUST2012www.

ti.

comPARAMETERMEASUREMENTINFORMATIONFigure1.

InputCircuitFigure2.

OutputCircuitFigure3.

WiredORFigure4.

LDOOutputCircuit8SubmitDocumentationFeedbackCopyright2009–2012,TexasInstrumentsIncorporatedProductFolderLinks:CDC3S04CDC3S04www.

ti.

comSCAS883C–OCTOBER2009–REVISEDAUGUST2012TYPICALCHARACTERISTICSFigure5.

CLKxOn-TimeFromRESETOff-to-OnFigure6.

CLKxOn-TimeFromREQOff-to-OnFigure7.

CLKxOn-TimeFromVDD_ANAOff-to-OnCopyright2009–2012,TexasInstrumentsIncorporatedSubmitDocumentationFeedback9ProductFolderLinks:CDC3S04CDC3S04SCAS883C–OCTOBER2009–REVISEDAUGUST2012www.

ti.

comTYPICALCHARACTERISTICS(continued)SUPPLYCURRENT(IDD_ANA,IDD_DIG)vsOUTPUTLOAD(CL)AT38.

4MHzINPUTCLOCKFigure8.

SUPPLYCURRENT(IDD_ANA,IDD_DIG)vsOUTPUTLOAD(CL)AT26MHzINPUTCLOCKFigure9.

SUPPLYCURRENT(IDD_ANA,IDD_DIG)vsINPUTFREQUENCY(MCLK_IN)Figure10.

10SubmitDocumentationFeedbackCopyright2009–2012,TexasInstrumentsIncorporatedProductFolderLinks:CDC3S04CDC3S04www.

ti.

comSCAS883C–OCTOBER2009–REVISEDAUGUST2012TYPICALCHARACTERISTICS(continued)SUPPLYCURRENT(IDD_ANA,IDD_DIG)vsINPUTVOLTAGELEVELAT38.

4MHzINPUTCLOCKFigure11.

SUPPLYCURRENT(IDD_ANA,IDD_DIG)vsINPUTVOLTAGELEVELAT26MHzINPUTCLOCKFigure12.

TCXOINPUTCLOCKvsOUTPUTCLOCKAT38.

4MHzFigure13.

Copyright2009–2012,TexasInstrumentsIncorporatedSubmitDocumentationFeedback11ProductFolderLinks:CDC3S04CDC3S04SCAS883C–OCTOBER2009–REVISEDAUGUST2012www.

ti.

comTYPICALCHARACTERISTICS(continued)TCXOINPUTCLOCKvsOUTPUTCLOCKAT26MHzFigure14.

SINEWAVEINPUTCLOCKvsOUTPUTCLOCKAT38.

4MHzFigure15.

12SubmitDocumentationFeedbackCopyright2009–2012,TexasInstrumentsIncorporatedProductFolderLinks:CDC3S04CDC3S04www.

ti.

comSCAS883C–OCTOBER2009–REVISEDAUGUST2012TYPICALCHARACTERISTICS(continued)SINEWAVEINPUTCLOCKvsOUTPUTCLOCKAT26MHzFigure16.

OUTPUTGAINvsINPUTFREQUENCY(MCLK_IN)Figure17.

Copyright2009–2012,TexasInstrumentsIncorporatedSubmitDocumentationFeedback13ProductFolderLinks:CDC3S04CDC3S04SCAS883C–OCTOBER2009–REVISEDAUGUST2012www.

ti.

comTYPICALCHARACTERISTICS(continued)INPUTvsOUTPUTPHASE-NOISEPERFORMANCEWITH38.

4-MHzTCXOFigure18.

INPUTvsOUTPUTPHASE-NOISEPERFORMANCEWITH26-MHzTCXOFigure19.

LDOPOWERSUPPLYREJECTIONvsFREQUENCY(PSRR)Figure20.

14SubmitDocumentationFeedbackCopyright2009–2012,TexasInstrumentsIncorporatedProductFolderLinks:CDC3S04CDC3S04www.

ti.

comSCAS883C–OCTOBER2009–REVISEDAUGUST2012TYPICALCHARACTERISTICS(continued)LDOOUTPUTSPECTRALNOISEDENSITYvsFREQUENCYFigure21.

Copyright2009–2012,TexasInstrumentsIncorporatedSubmitDocumentationFeedback15ProductFolderLinks:CDC3S04CDC3S04SCAS883C–OCTOBER2009–REVISEDAUGUST2012www.

ti.

comDETAILEDDESCRIPTIONSDAH/SCLHSERIALINTERFACE(Hs-Mode)ThissectiondescribestheSDAH/SCLHinterfaceoftheCDC3S04device.

TheCDC3S04operatesasaslavedeviceofthetwo-wireserialSDAH/SCLHbus,compatiblewiththepopularI2Cspecification(UM10204-I2C-busspecificationandusermanualRev.

03–19June2007).

Itoperatesinthehigh-speedmode(upto3.

4Mbit/s)andsupports7-bitaddressing.

TheCDC3S04isfullydownwardcompatiblewithfast-andstandard-mode(F/S)devicesforbidirectionalcommunicationinamixed-speedbussystem.

DataProtocolThedevicesupportsbyte-writeandbyte-readoperationsonly.

Thereisnoblock-writeorblock-readoperationsupported;therefore,nocommandcodebyteisneeded.

Whenabytehasbeensent,itiswrittenintotheinternalregisterandisimmediatelyeffective.

SlaveReceiverAddress(7bits)DeviceA6A5A4A3A2A1A0(1)R/WCDC3S0411011001/0(1)AddressbitA0isselectablebytheADR_A0input(pinD1).

ThisallowsaddressingoftwodevicesconnectedtothesameI2Cbus.

Thedefaultvalueis0,setbyaninternalpulldownresistor.

Byte-WriteProgrammingSequenceFigure22.

Byte-WriteProtocolByte-ReadProgrammingSequenceFigure23.

Byte-ReadProtocol16SubmitDocumentationFeedbackCopyright2009–2012,TexasInstrumentsIncorporatedProductFolderLinks:CDC3S04CDC3S04www.

ti.

comSCAS883C–OCTOBER2009–REVISEDAUGUST2012(1)FirstrisingedgeoftheSCLHsignalafterSrandaftereachacknowledgebit.

Figure24.

DefinitionofTimingforaCompleteHs-ModeTransferThefollowingdiagramshowshowtheCDC3S04clockbufferisconnectedtotheSDAH/SCLHserialinterfacebus.

Multipledevicescanbeconnectedtothebus,butthespeedmayneedtobereduced(3.

4MHzisthemaximum)ifmanydevicesareconnected.

Notethatthepullupresistors(RP)dependonthesupplyvoltage,buscapacitance,andnumberofconnecteddevices.

Formoredetails,seetheI2Cbusspecification.

Figure25.

SDAH/SCLHHardwareInterfaceSDAH/SCLHConfigurationRegistersTheoutputstagesareuserconfigurable.

Table3explainstheprogrammablefunctionsoftheCDC3S04.

Copyright2009–2012,TexasInstrumentsIncorporatedSubmitDocumentationFeedback17ProductFolderLinks:CDC3S04CDC3S04SCAS883C–OCTOBER2009–REVISEDAUGUST2012www.

ti.

comTable3.

ConfigurationRegister(ShadedCellsMarksPower-Up/DefaultSetting)OffsetBIT(1)AcronymDefault(2)RESET(3)Description01Type7REQ4INT1b1bCLK4off/on(4)OffOn6REQ3INT0b–CLK3off/on(4)OffOn5REQ2INT0b–CLK2off/on(4)OffOn4REQ1INT1b1bCLK1off/on(4)OffOn00hR/W3REQ4POL1b–SelectspolarityofREQ4Active-lowActive-high2REQ3POL1b–SelectspolarityofREQ3Active-lowActive-high1REQ2POL1b–SelectspolarityofREQ2Active-lowActive-high0REQ1POL1b–SelectspolarityofREQ1Active-lowActive-highDefinesifREQ4isusedtodecode7MREQ41b–MCLK_REQDefinesifREQ3isusedtodecode6MREQ31b–MCLK_REQNotusedforUsedfordecodingdecodingDefinesifREQ2isusedtodecode5MREQ21b–MCLK_REQ01hR/WDefinesifREQ1isusedtodecode4MREQ11b–MCLK_REQ3MCLKOUT1SelectsMCLK_REQoutputtype00=wired-OR(defaultsetting)00b–01=wired-AND2MCLKOUT01x=push-pull0–1–00b–Reserved7MREQCTRL1MCLK_REQgeneration(seeFigure27)0x=decodercontrolled(defaultsetting)00b–10=low6MREQCTRL011=high5LDOEN1SwitchesLDOonoroff:00=LDOison(defaultsetting)00b–01=LDOisoff4LDOEN002hR/W1x=decodercontrolled(seeFigure27)3REQ4PRIO1b1bDefinesexternalvsinternalREQ4priorityREQ4REQ4INT2REQ3PRIO0b–DefinesexternalvsinternalREQ3priorityREQ3REQ3INT1REQ2PRIO0b–DefinesexternalvsinternalREQ2priorityREQ2REQ2INT0REQ1PRIO1b1bDefinesexternalvsinternalREQ1priorityREQ1REQ1INT7HIGHDRIVE40b–Enableshigh-drivecapabilityCLK4TypicalHigh6HIGHDRIVE30b–Enableshigh-drivecapabilityCLK3TypicalHigh03h5HIGHDRIVE20b–Enableshigh-drivecapabilityCLK2TypicalHighR/W4HIGHDRIVE10b–Enableshigh-drivecapabilityCLK1TypicalHigh0–3–0b–Reserved04h–Bh(5)––ReservedR/W(1)AlldataistransferredwiththeMSBfirst.

(2)AdeviceresettodefaultconditionisinitiatedbyaVDD_DIGpower-upsequence.

(3)"–"meansthatdedicatedbitsdonotchangeatRESET.

(4)InactiveaslongastheREQxPRIObitislow,externalREQxpinsarevalid(seeFigure26)(5)Writingdatabeyond03hmayaffectdevicefunction.

18SubmitDocumentationFeedbackCopyright2009–2012,TexasInstrumentsIncorporatedProductFolderLinks:CDC3S04CDC3S04www.

ti.

comSCAS883C–OCTOBER2009–REVISEDAUGUST2012Figure26.

ClockOutputEnableSignal(ShadedLineMarksPower-Up/DefaultSetting)Figure27.

DecodingSchemeforMCLK_REQandLDOEN(ShadedLineMarksPower-Up/DefaultSetting)Copyright2009–2012,TexasInstrumentsIncorporatedSubmitDocumentationFeedback19ProductFolderLinks:CDC3S04CDC3S04SCAS883C–OCTOBER2009–REVISEDAUGUST2012www.

ti.

comAPPLICATIONINFORMATIONFigure28.

ClockDistributionScheme20SubmitDocumentationFeedbackCopyright2009–2012,TexasInstrumentsIncorporatedProductFolderLinks:CDC3S04CDC3S04www.

ti.

comSCAS883C–OCTOBER2009–REVISEDAUGUST2012REVISIONHISTORYChangesfromOriginal(October2009)toRevisionAPageChangedtheformatonpage1(moved2paragraphsfrompage2topage1)1ChangedtheXaxisfrom0.

1usto100us.

.

.

.

900us9ChangedOffset00hBit4Defaultvaluefrom0hto1b18ChangesfromRevisionA(July2010)toRevisionBPageChangedTable3"Offset"valueslistedin"Default"and"RESET"columnsfrom"h"to"b"18ChangesfromRevisionB(May2011)toRevisionCPageChangedfromRevB,2011toRevC,20121Changedthe8thFeatureitemfrom–30°Cto–40°C1Changedinthelastparagraphofdescriptionfrom–30°Cto–40°C2ChangedintheROCtablelastrow,from–30°Cto–40°C4Copyright2009–2012,TexasInstrumentsIncorporatedSubmitDocumentationFeedback21ProductFolderLinks:CDC3S04PACKAGEOPTIONADDENDUMwww.

ti.

com22-Jan-2014Addendum-Page1PACKAGINGINFORMATIONOrderableDeviceStatus(1)PackageTypePackageDrawingPinsPackageQtyEcoPlan(2)Lead/BallFinish(6)MSLPeakTemp(3)OpTemp(°C)DeviceMarking(4/5)SamplesCDC3S04YFFRACTIVEDSBGAYFF203000Green(RoHS&noSb/Br)SNAGCULevel-1-260C-UNLIM-40to85CDC3S04(1)Themarketingstatusvaluesaredefinedasfollows:ACTIVE:Productdevicerecommendedfornewdesigns.

LIFEBUY:TIhasannouncedthatthedevicewillbediscontinued,andalifetime-buyperiodisineffect.

NRND:Notrecommendedfornewdesigns.

Deviceisinproductiontosupportexistingcustomers,butTIdoesnotrecommendusingthispartinanewdesign.

PREVIEW:Devicehasbeenannouncedbutisnotinproduction.

Samplesmayormaynotbeavailable.

OBSOLETE:TIhasdiscontinuedtheproductionofthedevice.

(2)EcoPlan-Theplannedeco-friendlyclassification:Pb-Free(RoHS),Pb-Free(RoHSExempt),orGreen(RoHS&noSb/Br)-pleasecheckhttp://www.

ti.

com/productcontentforthelatestavailabilityinformationandadditionalproductcontentdetails.

TBD:ThePb-Free/Greenconversionplanhasnotbeendefined.

Pb-Free(RoHS):TI'sterms"Lead-Free"or"Pb-Free"meansemiconductorproductsthatarecompatiblewiththecurrentRoHSrequirementsforall6substances,includingtherequirementthatleadnotexceed0.

1%byweightinhomogeneousmaterials.

Wheredesignedtobesolderedathightemperatures,TIPb-Freeproductsaresuitableforuseinspecifiedlead-freeprocesses.

Pb-Free(RoHSExempt):ThiscomponenthasaRoHSexemptionforeither1)lead-basedflip-chipsolderbumpsusedbetweenthedieandpackage,or2)lead-baseddieadhesiveusedbetweenthedieandleadframe.

ThecomponentisotherwiseconsideredPb-Free(RoHScompatible)asdefinedabove.

Green(RoHS&noSb/Br):TIdefines"Green"tomeanPb-Free(RoHScompatible),andfreeofBromine(Br)andAntimony(Sb)basedflameretardants(BrorSbdonotexceed0.

1%byweightinhomogeneousmaterial)(3)MSL,PeakTemp.

-TheMoistureSensitivityLevelratingaccordingtotheJEDECindustrystandardclassifications,andpeaksoldertemperature.

(4)Theremaybeadditionalmarking,whichrelatestothelogo,thelottracecodeinformation,ortheenvironmentalcategoryonthedevice.

(5)MultipleDeviceMarkingswillbeinsideparentheses.

OnlyoneDeviceMarkingcontainedinparenthesesandseparatedbya"~"willappearonadevice.

IfalineisindentedthenitisacontinuationofthepreviouslineandthetwocombinedrepresenttheentireDeviceMarkingforthatdevice.

(6)Lead/BallFinish-OrderableDevicesmayhavemultiplematerialfinishoptions.

Finishoptionsareseparatedbyaverticalruledline.

Lead/BallFinishvaluesmaywraptotwolinesifthefinishvalueexceedsthemaximumcolumnwidth.

ImportantInformationandDisclaimer:TheinformationprovidedonthispagerepresentsTI'sknowledgeandbeliefasofthedatethatitisprovided.

TIbasesitsknowledgeandbeliefoninformationprovidedbythirdparties,andmakesnorepresentationorwarrantyastotheaccuracyofsuchinformation.

Effortsareunderwaytobetterintegrateinformationfromthirdparties.

TIhastakenandcontinuestotakereasonablestepstoproviderepresentativeandaccurateinformationbutmaynothaveconducteddestructivetestingorchemicalanalysisonincomingmaterialsandchemicals.

TIandTIsuppliersconsidercertaininformationtobeproprietary,andthusCASnumbersandotherlimitedinformationmaynotbeavailableforrelease.

InnoeventshallTI'sliabilityarisingoutofsuchinformationexceedthetotalpurchasepriceoftheTIpart(s)atissueinthisdocumentsoldbyTItoCustomeronanannualbasis.

PACKAGEOPTIONADDENDUMwww.

ti.

com22-Jan-2014Addendum-Page2TAPEANDREELINFORMATION*AlldimensionsarenominalDevicePackageTypePackageDrawingPinsSPQReelDiameter(mm)ReelWidthW1(mm)A0(mm)B0(mm)K0(mm)P1(mm)W(mm)Pin1QuadrantCDC3S04YFFRDSBGAYFF203000180.

08.

41.

632.

080.

694.

08.

0Q1PACKAGEMATERIALSINFORMATIONwww.

ti.

com17-Jun-2015PackMaterials-Page1*AlldimensionsarenominalDevicePackageTypePackageDrawingPinsSPQLength(mm)Width(mm)Height(mm)CDC3S04YFFRDSBGAYFF203000182.

0182.

020.

0PACKAGEMATERIALSINFORMATIONwww.

ti.

com17-Jun-2015PackMaterials-Page2D:Max=E:Max=1.

99mm,Min=1.

59mm,Min=1.

93mm1.

53mmIMPORTANTNOTICEANDDISCLAIMERTIPROVIDESTECHNICALANDRELIABILITYDATA(INCLUDINGDATASHEETS),DESIGNRESOURCES(INCLUDINGREFERENCEDESIGNS),APPLICATIONOROTHERDESIGNADVICE,WEBTOOLS,SAFETYINFORMATION,ANDOTHERRESOURCES"ASIS"ANDWITHALLFAULTS,ANDDISCLAIMSALLWARRANTIES,EXPRESSANDIMPLIED,INCLUDINGWITHOUTLIMITATIONANYIMPLIEDWARRANTIESOFMERCHANTABILITY,FITNESSFORAPARTICULARPURPOSEORNON-INFRINGEMENTOFTHIRDPARTYINTELLECTUALPROPERTYRIGHTS.

TheseresourcesareintendedforskilleddevelopersdesigningwithTIproducts.

Youaresolelyresponsiblefor(1)selectingtheappropriateTIproductsforyourapplication,(2)designing,validatingandtestingyourapplication,and(3)ensuringyourapplicationmeetsapplicablestandards,andanyothersafety,security,orotherrequirements.

Theseresourcesaresubjecttochangewithoutnotice.

TIgrantsyoupermissiontousetheseresourcesonlyfordevelopmentofanapplicationthatusestheTIproductsdescribedintheresource.

Otherreproductionanddisplayoftheseresourcesisprohibited.

NolicenseisgrantedtoanyotherTIintellectualpropertyrightortoanythirdpartyintellectualpropertyright.

TIdisclaimsresponsibilityfor,andyouwillfullyindemnifyTIanditsrepresentativesagainst,anyclaims,damages,costs,losses,andliabilitiesarisingoutofyouruseoftheseresources.

TI'sproductsareprovidedsubjecttoTI'sTermsofSale(www.

ti.

com/legal/termsofsale.

html)orotherapplicabletermsavailableeitheronti.

comorprovidedinconjunctionwithsuchTIproducts.

TI'sprovisionoftheseresourcesdoesnotexpandorotherwisealterTI'sapplicablewarrantiesorwarrantydisclaimersforTIproducts.

MailingAddress:TexasInstruments,PostOfficeBox655303,Dallas,Texas75265Copyright2019,TexasInstrumentsIncorporated

ti.

comSCAS883C–OCTOBER2009–REVISEDAUGUST2012QuadSine-WaveClockBufferWithLDOCheckforSamples:CDC3S041FEATURESDESCRIPTIONTheCDC3S04isafour-channellow-powerlow-jitter1:4Low-JitterClockBuffersine-waveclockbuffer.

ItcanbeusedtobufferaSingle-EndedSine-WaveClockInputandsinglemasterclocktomultipleperipherals.

ThefourOutputssine-waveoutputs(CLK1–CLK4)aredesignedforUltralowPhaseNoiseandStandbyCurrentminimalchannel-to-channelskewandultralowadditiveoutputjitter.

IndividualClockRequestInputsforEachOutputEachoutputhasitsownclockrequestinputswhichenablesthededicatedclockoutput.

TheseclockOn-ChipLow-DropoutOutput(LDO)forLow-requestsareactive-high(canalsobechangedtobeNoiseTCXOSupplyactive-lowviaI2C),andanoutputsignalisgeneratedSerialI2CInterface(CompatibleWithHigh-thatcanbesentbacktothemasterclocktorequestSpeedMode,3.

4Mbit/s)theclock(MCLK_REQ).

MCKL_REQisanopen-1.

8-VDevicePowerSupplysourceoutputandsupportsthewired-ORfunction(defaultmode).

Itneedsanexternalpulldownresistor.

WideTemperatureRange,–40°Cto85°CMCKL_REQcanbechangedtowired-ANDorpush-ESDProtection:2KVHBM,750VCDM,andpullfunctionalityviaI2C.

100VMMTheCDC3S04alsoprovidesanI2Cinterface(Hs-Small20-PinChip-ScalePackage:0.

4-mmmode)thatcanbeusedtoenableordisablethePitchWCSP(1.

6mm*2mm)outputs,selectthepolarityoftheREQinputs,andallowcontrolofinternaldecoding.

APPLICATIONSTheCDC3S04featuresanon-chiphigh-performanceCellularPhonesLDOthatacceptsvoltagesfrom2.

3Vto5.

5VandSmartPhonesoutputsa1.

8-Vsupply.

This1.

8-Vsupplycanbeusedtopoweranexternal1.

8-VTCXO.

ItcanbeMobileHandsetsenabledordisabledforpowersavingattheTCXO.

PortableSystemsWirelessModemsIncludingGPS,WLAN,W-BT,D-TV,DVB-H,FMRadio,WiMAX,andSystemClock1Pleasebeawarethatanimportantnoticeconcerningavailability,standardwarranty,anduseincriticalapplicationsofTexasInstrumentssemiconductorproductsanddisclaimerstheretoappearsattheendofthisdatasheet.

PRODUCTIONDATAinformationiscurrentasofpublicationdate.

Copyright2009–2012,TexasInstrumentsIncorporatedProductsconformtospecificationsperthetermsoftheTexasInstrumentsstandardwarranty.

Productionprocessingdoesnotnecessarilyincludetestingofallparameters.

CDC3S04SCAS883C–OCTOBER2009–REVISEDAUGUST2012www.

ti.

comThisintegratedcircuitcanbedamagedbyESD.

TexasInstrumentsrecommendsthatallintegratedcircuitsbehandledwithappropriateprecautions.

Failuretoobserveproperhandlingandinstallationprocedurescancausedamage.

ESDdamagecanrangefromsubtleperformancedegradationtocompletedevicefailure.

Precisionintegratedcircuitsmaybemoresusceptibletodamagebecauseverysmallparametricchangescouldcausethedevicenottomeetitspublishedspecifications.

DESCRIPTION(CONTINUED)AlowsignalattheRESETinputswitchestheoutputsCLK1andCLK4intothedefaultstate.

Inthisconfiguration,CLK1andCLK4areON(seeTable1);theremainingdevicefunctionisnotaffected.

Also,theRESETinputprovidesaglitchfilterwhichrejectsspikesoftypical300nsontheRESETlinetopreservefalsereset.

Acompletedeviceresettothedefaultconditioncanbeinitiatedbyapower-upcycleofVDD_DIG.

TheCDC3S04operatesfromtwo1.

8-Vsupplies.

Thereisacoresupply(VDD_DIG/GND_DIG)forthecorelogicandalow-noiseanalogsupply(VDD_ANA/GND_ANA)forthesine-waveoutputs.

TheCDC3S04isdesignedforsequence-lesspowerup.

Bothsupplyvoltagesmaybeappliedinanyorder.

TheCDC3S04isofferedina0.

4-mmpitchWCSPpackage(1.

6mm*2mm)andisoptimizedforlowstandbycurrent(0.

5A).

Itischaracterizedforoperationfrom–40°Cto85°C.

DEVICEINFORMATIONPINFUNCTIONSNAMEBALLNO.

TYPEFUNCTIONADR_A0D4InputSelectableaddressbitA0ofslave-addressregister;internal500-kΩpulldownresistorCLK1A4OutputClockoutput1CLK2A2OutputClockoutput2CLK3C4OutputClockoutput3CLK4C2OutputClockoutput4GND_ANAB4GroundGroundforsine-wavebufferGND_DIGD2GroundGroundforcorelogicMCLK_INB1InputMasterclockinputMCLK_REClockrequesttothemasterclocksource;active-high;open-sourceoutputforwired-ORD3OutputQconnection(defaultcondition).

Canbechangedtopush-pulloutputorwired-ANDoutputviaI2C.

REQ1A3InputClockrequestfromperipheral1;internal500-kΩpulldownresistorREQ2A1InputClockrequestfromperipheral2;internal500-kΩpulldownresistorREQ3C3InputClockrequestfromperipheral3;internal500-kΩpulldownresistorREQ4C1InputClockrequestfromperipheral4;internal500-kΩpulldownresistorPeripheralresetsignalprovidedbyapplicationprocessor.

Thesignalisactive-lowandswitchesRESETB2InputCLK1andCLK4outputstoON(seeTable1).

On-chipLDOisenabled.

Internal1-MΩpullupresistorand300-ns(typ)glitchfilter.

SCLHE4InputI2Cclockinput–Hs-mode.

Internal1-MΩpullupresistorSDAHE3Input/outputI2Cdatainput/output–Hs-mode.

Internal1-MΩpullupresistorVBATE2PowerSupplypintointernalLDOVDD_ANAB3Power1.

8-Vpowersupplyforsine-wavebuffer1.

8-Vpowersupplyforcorelogic.

PowerupofVDD_DIGresetsthewholedevicetothedefaultVDD_DIGD1Powercondition.

1.

8-VsupplyforexternalTCXO;LDOisenabledifRESET(defaultmode)orREQxisactive.

VLDOE1OutputLDOisnotenabledifonlyVBATison.

2SubmitDocumentationFeedbackCopyright2009–2012,TexasInstrumentsIncorporatedProductFolderLinks:CDC3S04CDC3S04www.

ti.

comSCAS883C–OCTOBER2009–REVISEDAUGUST2012FUNCTIONSELECTIONTABLESTable1.

ResetandRequest(REQx)ConditionsforClockOutputs(1)RESET(2)PRIORITYBIT(3)CLK1CLK2CLK3CLK40ControlledbyREQ2ControlledbyREQ30OnOn1ControlledbyREQ2INTControlledbyREQ3INT0ControlledbyREQ1ControlledbyREQ2ControlledbyREQ3ControlledbyREQ411ControlledbyREQ1INTControlledbyREQ2INTControlledbyREQ3INTControlledbyREQ4INT(1)Shadedcellsshowthedefaultsettingafterpowerup.

(2)RESETresetsREQ1PRIO/REQ4PRIOandREQ1INT/REQ4INTbitstotheirdefaultvalues(CLK1/4isON)butdoesnotchangetheremaininginternalSWbits.

DuringRESET,anyI2CoperationisblockeduntilRESETisdeactivated.

Aminimumpulsedurationof500nsmustbeappliedtoactivateRESET(theinternalglitch-filtersuppressesspikesoftypical300ns).

(3)Prioritybitdefinesiftheexternalcontrolpins(HWcontrolled)ortheSWbits(SWcontrolled)havepriority.

Itcanbesetintheconfigurationregister,Byte2,Bits0–3.

Table2.

RequestSignalConditionforClockOutputs(1)REQxCLKxREQ-Signals(2)MCLK_REQLDO(3)(REQ1/2/3/4)(CLK1/2/3/4)Active-low0ClockHighOn1DisabledtohighLow(ifallREQxarehigh)Off(ifallREQxarehigh)0Disabledtohigh(4)Low(ifallREQxarelow)Off(ifallREQxarelow)Active-high1Clock(4)HighOn(1)Shadedcellsshowthedefaultsettingafterpowerup.

(2)PolarityofREQ1,REQ2,REQ3,andREQ4areregister-configurableviaI2C(seeTable3,Byte0,Bits0–3).

Defaultsettingisactive-high.

(3)TheLDOiscontrolledbyanon-chipdecoder,butcanalsobeSWcontrolled(seeTable3,Byte2,Bits4–5).

(4)CLK1andCLK4areONafterdevicepowerup(defaultcondition).

CLK2andCLK3arecontrolledbyexternalREQ2andREQ3,respectively.

POWERGROUPSNAMEDESCRIPTIONVBATSupplypinforLDOprovidedbymainbattery.

LDOisnotworkingifonlyVBATison.

1.

8-Vlow-dropoutputvoltageforexternalTCXO.

LDOisenabledifVBATandVDD_DIGareonandREQxorRESETisVLDOactive(seeTable2).

1.

8-VpowersupplyforcorelogicandI2Clogic.

VDD_DIGmustbesuppliedforcorrectdeviceoperation.

PowerupofVDD_DIGVDD_DIGresetsthewholedevicetothedefaultcondition.

1.

8-Vpowersupplyforsine-wavebuffers.

Forcorrectsine-wavebufferfunction,allthreepowersupplies(VBAT,VDD_DIGVDD_ANAandVDD_ANA)mustbeon.

But,VDD_ANAcanbeswitchedonandoffatanytime.

Ifoff,thesine-waveoutputsareswitchedtohigh-impedance.

POWER-UPSEQUENCETheCDC3S04isdesignedforsequence-lesspowerup.

VBAT,VDD_DIG,andVDD_ANAmaybeappliedinanyorder.

Recommendedpower-onsequenceisVBATfirst,followedbyVDD_DIGandVDD_ANA.

Recommendedpower-offsequenceisinreverseorder.

Copyright2009–2012,TexasInstrumentsIncorporatedSubmitDocumentationFeedback3ProductFolderLinks:CDC3S04CDC3S04SCAS883C–OCTOBER2009–REVISEDAUGUST2012www.

ti.

comABSOLUTEMAXIMUMRATINGSoveroperatingfree-airtemperaturerange(unlessotherwisenoted)(1)VALUEUNITVDD_ANASupplyvoltagerange–0.

5to2.

5VVDD_DIGVBATBatterysupplyvoltagerange–0.

5to6.

5VVIInputvoltagerange(2)(3)–0.

5toVDD+0.

5VVOOutputvoltagerange(2)(3)–0.

5toVDD+0.

5VVLDOOutputvoltagerange–0.

5toVBAT+0.

5VInputcurrent(VIVDD)±20mAIOContinuousoutputcurrent±20mAILDOContinuousoutputcurrent±20mATstgStoragetemperaturerange–65to150°C(1)Stressesbeyondthoselistedunderabsolutemaximumratingsmaycausepermanentdamagetothedevice.

Thesearestressratingsonlyandfunctionaloperationofthedeviceattheseoranyotherconditionsbeyondthoseindicatedunderrecommendedoperatingconditionsisnotimplied.

Exposuretoabsolute–maximum–ratedconditionsforextendedperiodsmayaffectdevicereliability.

(2)Theinputandoutputnegativevoltageratingsmaybeexceedediftheinputandoutputclamp-currentratingsareobserved.

(3)TheinputVIandoutputVOpositivevoltagesarelimitedtotheabsolutemaximumratingforVDD=2.

5V.

THERMALCHARACTERISTICSfor20-pinWCSP(YFF)(1)AIRFLOW20-PINPARAMETERUNIT(lfm)WCSP071TJAThermalresistance,junction-to-ambient20062°C/W40059TJCThermalresistance,junction-to-case–17.

5°C/WTJBThermalresistance,junction-to-board–20.

5°C/WTJMaximumjunctiontemperature–125°C(1)ThepackagethermalimpedanceiscalculatedinaccordancewithJESD51andJEDEC2S2P(high-kboard).

RECOMMENDEDOPERATINGCONDITIONSMINNOMMAXUNITVDD_ANADevicesupplyvoltage1.

651.

81.

95VVDD_DIGDevicesupplyvoltage1.

651.

81.

95VVIH0.

65VDD_DIGVInputvoltageADR_A0,REQx,RESETVIL0.

35VDD_DIGVVISSine-waveinputvoltage–MCLK_IN;ac-coupledamplitude0.

51.

2VPPCLSine-waveoutputload(1)1030pFCOUTLDOoutputcapacitance(stabilizetheinternalcontrolloop)0.

82.

2FTAOperatingfree-airtemperature–4085°C(1)10pFisthetypicalload-drivingcapability.

Thedrivecapabilitycanbeoptimizedfor30pFbytheI2Cregister(Byte3,Bits7–4).

4SubmitDocumentationFeedbackCopyright2009–2012,TexasInstrumentsIncorporatedProductFolderLinks:CDC3S04CDC3S04www.

ti.

comSCAS883C–OCTOBER2009–REVISEDAUGUST2012ELECTRICALCHARACTERISTICSoverrecommendedoperatingfree-airtemperaturerange(unlessotherwisenoted)PARAMETERTESTCONDITIONSMINTYPMAXUNITOVERALLPARAMETERVBAT=5.

5V;Off(noREQ)0.

10.

2VDD_ANA=1.

95V;Analogsupplycurrent(1)IDD_ANALDOison;VIS=1VPP;mA(seeFigure8throughFigure12)Peroutput22.

6fMCLK_IN=38.

4MHz;RL=10kΩ;CL=10pF(2)VBAT=5.

5V;VDD_DIG=1.

95V;VDD_ANA=off;DigitalsupplycurrentIDD_DIG(seeFigure8through0.

1mALDO=off;VIS=1Vpp;fMCLK_IN=38.

4Figure12)MHz;CL=10pF;RL=10kΩVBAT=5.

5V;VDD_DIG/VDD_ANA=1.

95V;Alloutputsdisabled(noinputclock;LDOISBStandbycurrentoff;noREQ;RESETisinactive;I2Cisin0.

510Aidlemode);includes1-MΩpullupatI2CandRESETfMCLK_INInputfrequencySinewave0.

0138.

452MHzWired-ORoutput;IOH=–2mA;VDD_DIG=1.

65V(SeeVDD_DIG–0.

45MCLK_REQhigh-leveloutputFigure3.

)VOHVvoltagePush-pulloutput;VDD_DIG=1.

65V,VDD_DIG–0.

45IOH=–2mAWired-ANDoutput;IOL=2mA0.

45VDD_DIG=1.

65VMCLK_REQlow-leveloutputVOLVvoltagePush-pulloutput;VDD_DIG=1.

65V,0.

45IOL=2mAVIKLVCMOSinputvoltageVDD_DIG=1.

65V;II=–18mA–1.

2VInputcurrentADR_A0,REQx6(500-kΩpulldown)IIHVI=VDD_DIG;VDD_DIG=1.

95VAInputcurrentRESET(1-MΩ2pullup)InputcurrentADR_A0,REQx–2(500-kΩpulldown)IILVI=0V;VDD_DIG=1.

95VAInputcurrentRESET(1-MΩ–3pullup)InputcapacitanceADR_A0,CIVI=0VorVDD_DIG3pFREQx,RESETSDAH/SCLHPARAMETER(Hs-Mode)SCLH/SDAHinputclampVIKVDD_DIG=1.

65V;II=–18mA–1.

2VvoltageIISCLH/SDAHinputcurrent0.

1VDD_DIG1MHzOutputvoltageVIS=0.

5VPP445490500mVPP10Hzto10MHz;fOUT=38.

4MHz0.

30.

6tjitadd(rms)Additivermsjitter(4)psRMS10kHzto10MHz;fOUT=38.

4MHz0.

10.

2Atoffset=1kHz–142–135AdditivephasenoiseatfOUT=pnaddAtoffset=10kHz–152–145dBc/Hz38.

4MHz(5)Atoffset=100kHz–157–150RINInputresistanceAtdclevel1215kΩCINInputcapacitancefMCLK_IN=38.

4MHz57pFELECTRICALCHARACTERISTICofLDO(COUT=0.

8to2.

7F)(6)VBATInputvoltagerange2.

35.

5VVLDOLDOoutputvoltage(7)2.

3V

721.

81.

9VMaximumlineregulation2.

3V

5%ΔVLDO0

5V;Maximumloadregulation0.

5%TJ=25°CILOADLoadcurrentCOUT=0.

8Fto2.

7F05mAILCLLDOoutputcurrentlimitVLDO=0.

9*VLDO(TYP)1060mAILGNDLDOgroundpincurrent(8)VBAT=3.

6V;0

2A100Hz60681kHz5562VBAT=2.

3V(formin)VBAT=2.

5V(fortyp)10kHz4552Power-supplyrejectionratioPSRRdBVLDO=1.

8V(ripplerejection)(seeFigure20)100kHz3340ILOAD=5mAVripple=0.

1Vpp1MHz374610MHz6067Outputnoisevoltage(seeBW=10Hzto100kHz;VLDO=1.

8V;VN30VRMSFigure21)ILOAD=5mA(4)Additivermsjitteristheintegratedrmsjitterthatthedeviceaddstothesignalchain.

Itiscalculatedby(5)Additivephasenoiseistheamountofphasenoisethatthedeviceaddstothesignalchain.

ItiscalculatedbyLadd(dB)=10log(100.

1Lout–100.

1Lin).

(6)MinimumCOUTshouldbe100nFtoallowforstableLDOoperation.

(7)LDOoutputvoltageincludesmaximumlineandloadregulation.

(8)LDOgroundpincurrentdoesnotchangeoverVBAT.

6SubmitDocumentationFeedbackCopyright2009–2012,TexasInstrumentsIncorporatedProductFolderLinks:CDC3S04CDC3S04www.

ti.

comSCAS883C–OCTOBER2009–REVISEDAUGUST2012TIMINGREQUIREMENTSoveroperatingfree-airtemperaturerange(unlessotherwisenoted)VLDO=1.

8V;CL=10pF;RL=10kΩPARAMETERTESTCONDITIONSMINTYP(1)MAXUNITTIMINGPARAMETERtPDPropagationdelaytimeMCLK_IN-to-CLKx;fMCLK_IN=38.

4MHz3nstLHREQx-to-MCLK_REQ(wired-OR,CL=15pF,Propagationdelaytime,low-to-high15nsRL=10kΩ);CLKxon-time–REQ-to-CLKx0.

30.

4sfMCLK_IN=38.

4MHz;VVDD_ANAison;CLKxon-time–RESET-to-CLKx(3)VIS=1V;VOS=–1dB(seeFigure5and0.

60.

8sFigure6)CLKxoff-time–REQ-to-CLKx25nstCLK(2)CLKxon-time–VDD_ANAto-CLKxfMCLK_IN=38.

4MHz;VIS=1V;2050sVOS=–1dB;measurementstartswhenVDD_ANAis90%of1.

7V(seeFigure7)PulsedurationofspikesthatmustbetSPsuppressedbytheinputfilterfor100nsRESET(3)tsk(o)Outputskew(4)fMCLK_IN=38.

4MHz;CLK1-to-CLK42550psLDOon-time(5)VLDO=1.

7V,ILDO=5mA,tLDO–REQ-to-LDO;100300s2.

3V

7F–RESET-to-LDO(1)AlltypicalvaluesareatnominalVDD_ANAandVDD_DIG.

(2)CLKon-timeismeasuredwithvalidinputsignal(VIS=1Vpp).

IncaseaTXCOisused,theLDOandTCXOarealreadyon.

(3)Pulsesabove500nsareinterpretedasavalidresetsignal.

TotaltimefromRESET-to-CLKxisthesumoftSP+tCLK_/RESET.

(4)OutputskewiscalculatedasthegreaterofthedifferencebetweenthefastestandtheslowesttPLHorthedifferencebetweenthefastestandtheslowesttPHL.

(5)LDOoff-timedependsonthedischargetimeoftheR-Ccomponents(seeFigure4).

PARAMETERMINMAXUNITSDAH/SCLHTIMINGREQUIREMENTS,Hs-Mode(CBUS=100pFforeachI2Cline;seeFigure24andFigure25)fSCLHSCLHclockfrequency03.

4MHztsu(START)STARTsetuptime(SCLHhighbeforeSDAHlow)160nsth(START)STARTholdtime(SCLHlowafterSDAHlow)160nstLOWLowperiodoftheSCLHclock160nstHIGHHighperiodoftheSCLHclock60nsth(SDAH)SDAHholdtime(SDAHvalidafterSCLHlow)0(1)70nstsu(SDAH)SDAHsetuptime10nsSCLHrisetime1040nstrSDAHrisetime1080SCLHfalltime1040nstfSDAHfalltime1080tsu(STOP)STOPsetuptime160nsPulsedurationofspikesthatmustbesuppressedbytheinputfilterforSDAHandtSP010nsSCLH(1)AdevicemustinternallyprovideadataholdtimetobridgetheundefinedperiodbetweenVIHandVILofthefallingedgeoftheSCLHsignal.

AninputcircuitwithathresholdaslowaspossibleforthefallingedgeoftheSCLHsignalminimizesthisholdtime.

Copyright2009–2012,TexasInstrumentsIncorporatedSubmitDocumentationFeedback7ProductFolderLinks:CDC3S04CDC3S04SCAS883C–OCTOBER2009–REVISEDAUGUST2012www.

ti.

comPARAMETERMEASUREMENTINFORMATIONFigure1.

InputCircuitFigure2.

OutputCircuitFigure3.

WiredORFigure4.

LDOOutputCircuit8SubmitDocumentationFeedbackCopyright2009–2012,TexasInstrumentsIncorporatedProductFolderLinks:CDC3S04CDC3S04www.

ti.

comSCAS883C–OCTOBER2009–REVISEDAUGUST2012TYPICALCHARACTERISTICSFigure5.

CLKxOn-TimeFromRESETOff-to-OnFigure6.

CLKxOn-TimeFromREQOff-to-OnFigure7.

CLKxOn-TimeFromVDD_ANAOff-to-OnCopyright2009–2012,TexasInstrumentsIncorporatedSubmitDocumentationFeedback9ProductFolderLinks:CDC3S04CDC3S04SCAS883C–OCTOBER2009–REVISEDAUGUST2012www.

ti.

comTYPICALCHARACTERISTICS(continued)SUPPLYCURRENT(IDD_ANA,IDD_DIG)vsOUTPUTLOAD(CL)AT38.

4MHzINPUTCLOCKFigure8.

SUPPLYCURRENT(IDD_ANA,IDD_DIG)vsOUTPUTLOAD(CL)AT26MHzINPUTCLOCKFigure9.

SUPPLYCURRENT(IDD_ANA,IDD_DIG)vsINPUTFREQUENCY(MCLK_IN)Figure10.

10SubmitDocumentationFeedbackCopyright2009–2012,TexasInstrumentsIncorporatedProductFolderLinks:CDC3S04CDC3S04www.

ti.

comSCAS883C–OCTOBER2009–REVISEDAUGUST2012TYPICALCHARACTERISTICS(continued)SUPPLYCURRENT(IDD_ANA,IDD_DIG)vsINPUTVOLTAGELEVELAT38.

4MHzINPUTCLOCKFigure11.

SUPPLYCURRENT(IDD_ANA,IDD_DIG)vsINPUTVOLTAGELEVELAT26MHzINPUTCLOCKFigure12.

TCXOINPUTCLOCKvsOUTPUTCLOCKAT38.

4MHzFigure13.

Copyright2009–2012,TexasInstrumentsIncorporatedSubmitDocumentationFeedback11ProductFolderLinks:CDC3S04CDC3S04SCAS883C–OCTOBER2009–REVISEDAUGUST2012www.

ti.

comTYPICALCHARACTERISTICS(continued)TCXOINPUTCLOCKvsOUTPUTCLOCKAT26MHzFigure14.

SINEWAVEINPUTCLOCKvsOUTPUTCLOCKAT38.

4MHzFigure15.

12SubmitDocumentationFeedbackCopyright2009–2012,TexasInstrumentsIncorporatedProductFolderLinks:CDC3S04CDC3S04www.

ti.

comSCAS883C–OCTOBER2009–REVISEDAUGUST2012TYPICALCHARACTERISTICS(continued)SINEWAVEINPUTCLOCKvsOUTPUTCLOCKAT26MHzFigure16.

OUTPUTGAINvsINPUTFREQUENCY(MCLK_IN)Figure17.

Copyright2009–2012,TexasInstrumentsIncorporatedSubmitDocumentationFeedback13ProductFolderLinks:CDC3S04CDC3S04SCAS883C–OCTOBER2009–REVISEDAUGUST2012www.

ti.

comTYPICALCHARACTERISTICS(continued)INPUTvsOUTPUTPHASE-NOISEPERFORMANCEWITH38.

4-MHzTCXOFigure18.

INPUTvsOUTPUTPHASE-NOISEPERFORMANCEWITH26-MHzTCXOFigure19.

LDOPOWERSUPPLYREJECTIONvsFREQUENCY(PSRR)Figure20.

14SubmitDocumentationFeedbackCopyright2009–2012,TexasInstrumentsIncorporatedProductFolderLinks:CDC3S04CDC3S04www.

ti.

comSCAS883C–OCTOBER2009–REVISEDAUGUST2012TYPICALCHARACTERISTICS(continued)LDOOUTPUTSPECTRALNOISEDENSITYvsFREQUENCYFigure21.

Copyright2009–2012,TexasInstrumentsIncorporatedSubmitDocumentationFeedback15ProductFolderLinks:CDC3S04CDC3S04SCAS883C–OCTOBER2009–REVISEDAUGUST2012www.

ti.

comDETAILEDDESCRIPTIONSDAH/SCLHSERIALINTERFACE(Hs-Mode)ThissectiondescribestheSDAH/SCLHinterfaceoftheCDC3S04device.

TheCDC3S04operatesasaslavedeviceofthetwo-wireserialSDAH/SCLHbus,compatiblewiththepopularI2Cspecification(UM10204-I2C-busspecificationandusermanualRev.

03–19June2007).

Itoperatesinthehigh-speedmode(upto3.

4Mbit/s)andsupports7-bitaddressing.

TheCDC3S04isfullydownwardcompatiblewithfast-andstandard-mode(F/S)devicesforbidirectionalcommunicationinamixed-speedbussystem.

DataProtocolThedevicesupportsbyte-writeandbyte-readoperationsonly.

Thereisnoblock-writeorblock-readoperationsupported;therefore,nocommandcodebyteisneeded.

Whenabytehasbeensent,itiswrittenintotheinternalregisterandisimmediatelyeffective.

SlaveReceiverAddress(7bits)DeviceA6A5A4A3A2A1A0(1)R/WCDC3S0411011001/0(1)AddressbitA0isselectablebytheADR_A0input(pinD1).

ThisallowsaddressingoftwodevicesconnectedtothesameI2Cbus.

Thedefaultvalueis0,setbyaninternalpulldownresistor.

Byte-WriteProgrammingSequenceFigure22.

Byte-WriteProtocolByte-ReadProgrammingSequenceFigure23.

Byte-ReadProtocol16SubmitDocumentationFeedbackCopyright2009–2012,TexasInstrumentsIncorporatedProductFolderLinks:CDC3S04CDC3S04www.

ti.

comSCAS883C–OCTOBER2009–REVISEDAUGUST2012(1)FirstrisingedgeoftheSCLHsignalafterSrandaftereachacknowledgebit.

Figure24.

DefinitionofTimingforaCompleteHs-ModeTransferThefollowingdiagramshowshowtheCDC3S04clockbufferisconnectedtotheSDAH/SCLHserialinterfacebus.

Multipledevicescanbeconnectedtothebus,butthespeedmayneedtobereduced(3.

4MHzisthemaximum)ifmanydevicesareconnected.

Notethatthepullupresistors(RP)dependonthesupplyvoltage,buscapacitance,andnumberofconnecteddevices.

Formoredetails,seetheI2Cbusspecification.

Figure25.

SDAH/SCLHHardwareInterfaceSDAH/SCLHConfigurationRegistersTheoutputstagesareuserconfigurable.

Table3explainstheprogrammablefunctionsoftheCDC3S04.

Copyright2009–2012,TexasInstrumentsIncorporatedSubmitDocumentationFeedback17ProductFolderLinks:CDC3S04CDC3S04SCAS883C–OCTOBER2009–REVISEDAUGUST2012www.

ti.

comTable3.

ConfigurationRegister(ShadedCellsMarksPower-Up/DefaultSetting)OffsetBIT(1)AcronymDefault(2)RESET(3)Description01Type7REQ4INT1b1bCLK4off/on(4)OffOn6REQ3INT0b–CLK3off/on(4)OffOn5REQ2INT0b–CLK2off/on(4)OffOn4REQ1INT1b1bCLK1off/on(4)OffOn00hR/W3REQ4POL1b–SelectspolarityofREQ4Active-lowActive-high2REQ3POL1b–SelectspolarityofREQ3Active-lowActive-high1REQ2POL1b–SelectspolarityofREQ2Active-lowActive-high0REQ1POL1b–SelectspolarityofREQ1Active-lowActive-highDefinesifREQ4isusedtodecode7MREQ41b–MCLK_REQDefinesifREQ3isusedtodecode6MREQ31b–MCLK_REQNotusedforUsedfordecodingdecodingDefinesifREQ2isusedtodecode5MREQ21b–MCLK_REQ01hR/WDefinesifREQ1isusedtodecode4MREQ11b–MCLK_REQ3MCLKOUT1SelectsMCLK_REQoutputtype00=wired-OR(defaultsetting)00b–01=wired-AND2MCLKOUT01x=push-pull0–1–00b–Reserved7MREQCTRL1MCLK_REQgeneration(seeFigure27)0x=decodercontrolled(defaultsetting)00b–10=low6MREQCTRL011=high5LDOEN1SwitchesLDOonoroff:00=LDOison(defaultsetting)00b–01=LDOisoff4LDOEN002hR/W1x=decodercontrolled(seeFigure27)3REQ4PRIO1b1bDefinesexternalvsinternalREQ4priorityREQ4REQ4INT2REQ3PRIO0b–DefinesexternalvsinternalREQ3priorityREQ3REQ3INT1REQ2PRIO0b–DefinesexternalvsinternalREQ2priorityREQ2REQ2INT0REQ1PRIO1b1bDefinesexternalvsinternalREQ1priorityREQ1REQ1INT7HIGHDRIVE40b–Enableshigh-drivecapabilityCLK4TypicalHigh6HIGHDRIVE30b–Enableshigh-drivecapabilityCLK3TypicalHigh03h5HIGHDRIVE20b–Enableshigh-drivecapabilityCLK2TypicalHighR/W4HIGHDRIVE10b–Enableshigh-drivecapabilityCLK1TypicalHigh0–3–0b–Reserved04h–Bh(5)––ReservedR/W(1)AlldataistransferredwiththeMSBfirst.

(2)AdeviceresettodefaultconditionisinitiatedbyaVDD_DIGpower-upsequence.

(3)"–"meansthatdedicatedbitsdonotchangeatRESET.

(4)InactiveaslongastheREQxPRIObitislow,externalREQxpinsarevalid(seeFigure26)(5)Writingdatabeyond03hmayaffectdevicefunction.

18SubmitDocumentationFeedbackCopyright2009–2012,TexasInstrumentsIncorporatedProductFolderLinks:CDC3S04CDC3S04www.

ti.

comSCAS883C–OCTOBER2009–REVISEDAUGUST2012Figure26.

ClockOutputEnableSignal(ShadedLineMarksPower-Up/DefaultSetting)Figure27.

DecodingSchemeforMCLK_REQandLDOEN(ShadedLineMarksPower-Up/DefaultSetting)Copyright2009–2012,TexasInstrumentsIncorporatedSubmitDocumentationFeedback19ProductFolderLinks:CDC3S04CDC3S04SCAS883C–OCTOBER2009–REVISEDAUGUST2012www.

ti.

comAPPLICATIONINFORMATIONFigure28.

ClockDistributionScheme20SubmitDocumentationFeedbackCopyright2009–2012,TexasInstrumentsIncorporatedProductFolderLinks:CDC3S04CDC3S04www.

ti.

comSCAS883C–OCTOBER2009–REVISEDAUGUST2012REVISIONHISTORYChangesfromOriginal(October2009)toRevisionAPageChangedtheformatonpage1(moved2paragraphsfrompage2topage1)1ChangedtheXaxisfrom0.

1usto100us.

.

.

.

900us9ChangedOffset00hBit4Defaultvaluefrom0hto1b18ChangesfromRevisionA(July2010)toRevisionBPageChangedTable3"Offset"valueslistedin"Default"and"RESET"columnsfrom"h"to"b"18ChangesfromRevisionB(May2011)toRevisionCPageChangedfromRevB,2011toRevC,20121Changedthe8thFeatureitemfrom–30°Cto–40°C1Changedinthelastparagraphofdescriptionfrom–30°Cto–40°C2ChangedintheROCtablelastrow,from–30°Cto–40°C4Copyright2009–2012,TexasInstrumentsIncorporatedSubmitDocumentationFeedback21ProductFolderLinks:CDC3S04PACKAGEOPTIONADDENDUMwww.

ti.

com22-Jan-2014Addendum-Page1PACKAGINGINFORMATIONOrderableDeviceStatus(1)PackageTypePackageDrawingPinsPackageQtyEcoPlan(2)Lead/BallFinish(6)MSLPeakTemp(3)OpTemp(°C)DeviceMarking(4/5)SamplesCDC3S04YFFRACTIVEDSBGAYFF203000Green(RoHS&noSb/Br)SNAGCULevel-1-260C-UNLIM-40to85CDC3S04(1)Themarketingstatusvaluesaredefinedasfollows:ACTIVE:Productdevicerecommendedfornewdesigns.

LIFEBUY:TIhasannouncedthatthedevicewillbediscontinued,andalifetime-buyperiodisineffect.

NRND:Notrecommendedfornewdesigns.

Deviceisinproductiontosupportexistingcustomers,butTIdoesnotrecommendusingthispartinanewdesign.

PREVIEW:Devicehasbeenannouncedbutisnotinproduction.

Samplesmayormaynotbeavailable.

OBSOLETE:TIhasdiscontinuedtheproductionofthedevice.

(2)EcoPlan-Theplannedeco-friendlyclassification:Pb-Free(RoHS),Pb-Free(RoHSExempt),orGreen(RoHS&noSb/Br)-pleasecheckhttp://www.

ti.

com/productcontentforthelatestavailabilityinformationandadditionalproductcontentdetails.

TBD:ThePb-Free/Greenconversionplanhasnotbeendefined.

Pb-Free(RoHS):TI'sterms"Lead-Free"or"Pb-Free"meansemiconductorproductsthatarecompatiblewiththecurrentRoHSrequirementsforall6substances,includingtherequirementthatleadnotexceed0.

1%byweightinhomogeneousmaterials.

Wheredesignedtobesolderedathightemperatures,TIPb-Freeproductsaresuitableforuseinspecifiedlead-freeprocesses.

Pb-Free(RoHSExempt):ThiscomponenthasaRoHSexemptionforeither1)lead-basedflip-chipsolderbumpsusedbetweenthedieandpackage,or2)lead-baseddieadhesiveusedbetweenthedieandleadframe.

ThecomponentisotherwiseconsideredPb-Free(RoHScompatible)asdefinedabove.

Green(RoHS&noSb/Br):TIdefines"Green"tomeanPb-Free(RoHScompatible),andfreeofBromine(Br)andAntimony(Sb)basedflameretardants(BrorSbdonotexceed0.

1%byweightinhomogeneousmaterial)(3)MSL,PeakTemp.

-TheMoistureSensitivityLevelratingaccordingtotheJEDECindustrystandardclassifications,andpeaksoldertemperature.

(4)Theremaybeadditionalmarking,whichrelatestothelogo,thelottracecodeinformation,ortheenvironmentalcategoryonthedevice.

(5)MultipleDeviceMarkingswillbeinsideparentheses.

OnlyoneDeviceMarkingcontainedinparenthesesandseparatedbya"~"willappearonadevice.

IfalineisindentedthenitisacontinuationofthepreviouslineandthetwocombinedrepresenttheentireDeviceMarkingforthatdevice.

(6)Lead/BallFinish-OrderableDevicesmayhavemultiplematerialfinishoptions.

Finishoptionsareseparatedbyaverticalruledline.

Lead/BallFinishvaluesmaywraptotwolinesifthefinishvalueexceedsthemaximumcolumnwidth.

ImportantInformationandDisclaimer:TheinformationprovidedonthispagerepresentsTI'sknowledgeandbeliefasofthedatethatitisprovided.

TIbasesitsknowledgeandbeliefoninformationprovidedbythirdparties,andmakesnorepresentationorwarrantyastotheaccuracyofsuchinformation.

Effortsareunderwaytobetterintegrateinformationfromthirdparties.

TIhastakenandcontinuestotakereasonablestepstoproviderepresentativeandaccurateinformationbutmaynothaveconducteddestructivetestingorchemicalanalysisonincomingmaterialsandchemicals.

TIandTIsuppliersconsidercertaininformationtobeproprietary,andthusCASnumbersandotherlimitedinformationmaynotbeavailableforrelease.

InnoeventshallTI'sliabilityarisingoutofsuchinformationexceedthetotalpurchasepriceoftheTIpart(s)atissueinthisdocumentsoldbyTItoCustomeronanannualbasis.

PACKAGEOPTIONADDENDUMwww.

ti.

com22-Jan-2014Addendum-Page2TAPEANDREELINFORMATION*AlldimensionsarenominalDevicePackageTypePackageDrawingPinsSPQReelDiameter(mm)ReelWidthW1(mm)A0(mm)B0(mm)K0(mm)P1(mm)W(mm)Pin1QuadrantCDC3S04YFFRDSBGAYFF203000180.

08.

41.

632.

080.

694.

08.

0Q1PACKAGEMATERIALSINFORMATIONwww.

ti.

com17-Jun-2015PackMaterials-Page1*AlldimensionsarenominalDevicePackageTypePackageDrawingPinsSPQLength(mm)Width(mm)Height(mm)CDC3S04YFFRDSBGAYFF203000182.

0182.

020.

0PACKAGEMATERIALSINFORMATIONwww.

ti.

com17-Jun-2015PackMaterials-Page2D:Max=E:Max=1.

99mm,Min=1.

59mm,Min=1.

93mm1.

53mmIMPORTANTNOTICEANDDISCLAIMERTIPROVIDESTECHNICALANDRELIABILITYDATA(INCLUDINGDATASHEETS),DESIGNRESOURCES(INCLUDINGREFERENCEDESIGNS),APPLICATIONOROTHERDESIGNADVICE,WEBTOOLS,SAFETYINFORMATION,ANDOTHERRESOURCES"ASIS"ANDWITHALLFAULTS,ANDDISCLAIMSALLWARRANTIES,EXPRESSANDIMPLIED,INCLUDINGWITHOUTLIMITATIONANYIMPLIEDWARRANTIESOFMERCHANTABILITY,FITNESSFORAPARTICULARPURPOSEORNON-INFRINGEMENTOFTHIRDPARTYINTELLECTUALPROPERTYRIGHTS.

TheseresourcesareintendedforskilleddevelopersdesigningwithTIproducts.

Youaresolelyresponsiblefor(1)selectingtheappropriateTIproductsforyourapplication,(2)designing,validatingandtestingyourapplication,and(3)ensuringyourapplicationmeetsapplicablestandards,andanyothersafety,security,orotherrequirements.

Theseresourcesaresubjecttochangewithoutnotice.

TIgrantsyoupermissiontousetheseresourcesonlyfordevelopmentofanapplicationthatusestheTIproductsdescribedintheresource.

Otherreproductionanddisplayoftheseresourcesisprohibited.

NolicenseisgrantedtoanyotherTIintellectualpropertyrightortoanythirdpartyintellectualpropertyright.

TIdisclaimsresponsibilityfor,andyouwillfullyindemnifyTIanditsrepresentativesagainst,anyclaims,damages,costs,losses,andliabilitiesarisingoutofyouruseoftheseresources.

TI'sproductsareprovidedsubjecttoTI'sTermsofSale(www.

ti.

com/legal/termsofsale.

html)orotherapplicabletermsavailableeitheronti.

comorprovidedinconjunctionwithsuchTIproducts.

TI'sprovisionoftheseresourcesdoesnotexpandorotherwisealterTI'sapplicablewarrantiesorwarrantydisclaimersforTIproducts.

MailingAddress:TexasInstruments,PostOfficeBox655303,Dallas,Texas75265Copyright2019,TexasInstrumentsIncorporated

- batterywww.22hhh.com相关文档

- 温度www.22hhh.com

- www.themegallery.com

- 东海www.22hhh.com

- Homewww.22hhh.com

- 基金www

PacificRack(年付低至19美元),夏季促销PR-M系列和多IP站群VPS主机

这几天有几个网友询问到是否有Windows VPS主机便宜的VPS主机商。原本他们是在Linode、Vultr主机商挂载DD安装Windows系统的,有的商家支持自定义WIN镜像,但是这些操作起来特别效率低下,每次安装一个Windows系统需要一两个小时,所以如果能找到比较合适的自带Windows系统的服务器那最好不过。这不看到PacificRack商家有提供夏季促销活动,其中包括年付便宜套餐的P...

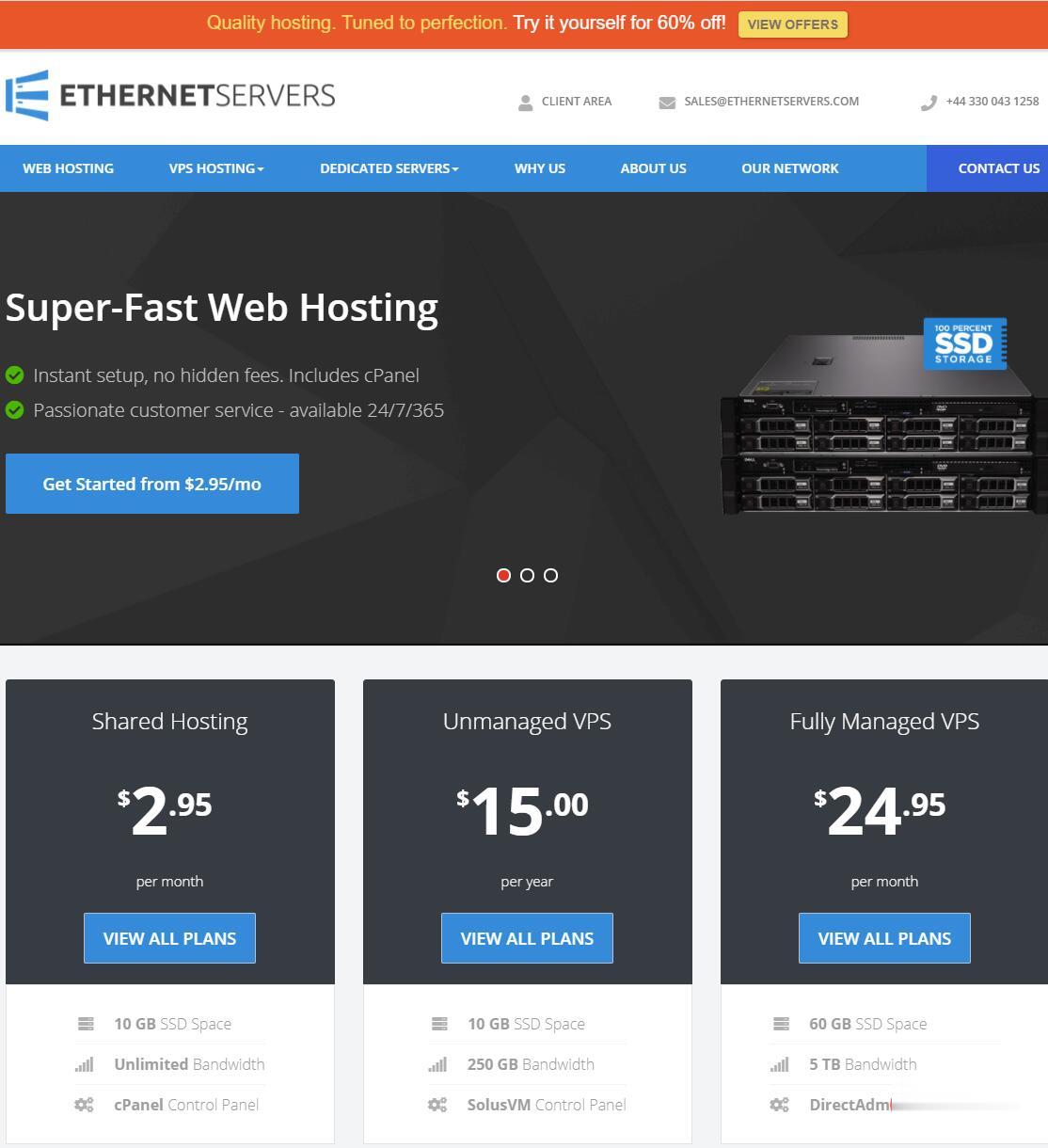

EtherNetservers年付仅10美元,美国洛杉矶VPS/1核512M内存10GB硬盘1Gpbs端口月流量500GB/2个IP

EtherNetservers是一家成立于2013年的英国主机商,提供基于OpenVZ和KVM架构的VPS,数据中心包括美国洛杉矶、新泽西和杰克逊维尔,商家支持使用PayPal、支付宝等付款方式,提供 60 天退款保证,这在IDC行业来说很少见,也可见商家对自家产品很有信心。有需要便宜VPS、多IP VPS的朋友可以关注一下。优惠码SUMMER-VPS-15 (终身 15% 的折扣)SUMMER-...

spinservers春节优惠:$149/月10Gbps圣何塞服务器-2*E5-2630Lv3 CPU,256G内存,2*1.6T SSD硬盘

spinservers是Majestic Hosting Solutions LLC旗下站点,商家提供国外服务器租用和Hybrid Dedicated等产品,数据中心包括美国达拉斯和圣何塞机房,机器默认10Gbps端口带宽,高配置硬件,支持使用PayPal、信用卡、支付宝或者微信等付款方式。农历春节之际,商家推出了几款特别促销配置,最低双路E5-2630Lv3机器每月149美元起,下面列出几款机器...

www.22hhh.com为你推荐

-

neworiental我国最好的英语学校是在哪里?敬汉卿姓名被抢注12306身份证名字被注册怎么办网红名字被抢注球星名字被抢注合法合理吗?硬盘工作原理数据存储的原理是什么杨紫别祝我生日快乐祝我生日快乐的歌词巨星prince去世作者为什么把伏尔泰的逝世说成是巨星陨落access数据库ACCESS数据库和SQL有什么区别?原代码什么叫源代码,源代码有什么作用月神谭给点人妖。变身类得小说。www.55125.cn如何登录www.jbjy.cn