芯片嵌入式1394总线接口的设计和实现

嵌入式1394总线接口的设计和实现http://www.yunyo ub ar.c o m/邮件群发

一、 引言

IEEE1394是1986年由苹果电脑公司针对高速数据传输开发的一种总线接口并于1995年由美国电气和电子工程师协会IEEE制定成标准 旨在取代并行SCSI接口。 目前为止它主要发展为IEEE1394-1995 1394a 1394b等系列标准。 1394作为一个工业标准的高速串行总线 已经被广泛应用于数字摄像机、数字照相机、 电视机顶盒、计算机及其外围设备、DVD设备等等甚至在航天军事领域也有一定的应用潜力。这些设备便携性的需求加快了它们集成度的提高这些都将使1394总线与嵌入式处理器的结合有很广阔的应用前景。

等时传输模式的优越性使1394总线广泛应用于图像传输领域而数字信号处理器DSP在图像等信号处理方面具有很大优势 因此基于DSP实现的1394总线接口在图像传输和处理领域有着广泛的应用需求但是 DSP芯片与1394总线芯片时序一般不能直接匹配。本文提出了一种基于DSP的1394总线接口实现方案能在基于DSP处理器的嵌入式系统上方便地实现1394总线接口具有较强的现实意义。

二、 设计方案

1394总线协议包括物理层链路层传输层应用层以及串行总线管理器。目前已经有很多厂家能提供1394总线接口的协议芯片可以很容易地实现1394总线接口本身。本文主要介绍如何通过FPGA实现嵌入式处理器与1394总线链路层控制器芯片的匹配嵌入式处理器把1394总线设备作为外设实现数据读取和写入。整体结构框图如图1。其中DSP是本文使用的嵌入式处理器类型 1394链路层控制器和1394物理层控制器是1394总线协议芯片。 FPGA是现场可编程门阵列是本文用于实现DSP与1394链路层控制器匹配的主要芯片与分立器件相比它具有可擦除、功耗小、体积小和调试方便等优势。本文选用AC TE L公司生产的APA300芯片来完成设计,它有30万门阵列资源 已经远远满足本设计的需求。

2.1 TMS320V33

德州仪器TI在DSP设计厂商中具有领先优势 TMS320V33是TI推出的TMS320系列的第三代处理器的升级版本的32位浮点运算数字信号处理器也是

目前国内外使用最为广泛的浮点DSP芯片之一。它有24位地址总线和32位数据总线本设计中使用高17位地址信号作为选通信号低7位地址信号作为输出给链路层芯片的有效地址信号低16位数据总线作为有效数据信号 H 1是37.5Mhz时钟信号。 TMS320V33读写外部寄存器时序如图2。

2.2链路层控制器

目前能提供1394a链路层控制器芯片的厂商有很多芯片种类也很多。而其中TI公司生产的TSB12LV32功能全面应用广泛。它是一款高性能通用1394a链路层控制器它主要实现1394链路层协议。 图3和图4是1394链路层芯片TSB12LV32的握手模式读写时序图。其中BCLK代表时钟信号输入最大工作频率是60MhzMWR代表读写使能信号输入高电平时读使能有效低电平时写使能有效MCS代表选通信号输入低电平有效MCA代表选通应答信号输出低电平有效MA代表地址信号输入M D代表双向数据信号另外

COLDFIRE,M8BIT/SIZ0,MCMODE/SIZ1为设置工作模式专用信号。在本设计中我们选用握手工作模式。

2.3方案选择

链路层控制器最高仅60Mhz的理论工作频率使得高性能的TMS 320V33必须增加自己的读写周期才能与之很好的配合 TM S 320 V33的读写周期可以通过RD Y信号或者增加可编程等待状态改变。在本设计中我们对TMS 320 V33使用RDY信号的方法来配合它与链路层芯片的读写时序。两种方法没有好坏之分区别仅在于DSP可编程等待状态的数量是有限的但是大部分情况下增加有限的等待状态已经足够。

我们可以选择使用组合逻辑和时序逻辑来完成此FPGA设计虽然组合逻辑设计方法简单、 占用资源少但是它仅仅是让DSP和链路层芯片的读写时序“凑”到一起很难实现完全配合而且会在读写过程中存在很多“毛刺”、 “竞争”和“冒险”不适合应用在性能要求比较高的场合。有限状态机是时序逻辑的一种它由状态、状态转换条件和状态输出组成。它具有以下优点 1.它是同步时序电路克服了组合逻辑顺序控制不灵活的缺点便于与CPU配合 2.状态机容易构成性能良好的同步时序逻辑模块只需要将“毛刺”控制在下一个状态到来之前这对于对

付设计中的“竞争冒险”现象无疑是一个较好的办法 3.状态机的结构模式相对简单设计方案相对固定设计方法具有通用性。

基于以上情况本设计中使用“有限状态机”的方法实现嵌入式处理器与链路层芯片的时序匹配保证在处理器的一次读写操作中数据能正确有效地传送。结合图

2、 图3和图4的读写时序给出状态转换图如图5。此状态机一共由6个状态组成分别为IDLE、 S TART、 RD0、 RDi、WR0、WRi。在RESET信号有效时设计进入复位阶段复位后状态机进入IDLE状态在IDLE状态中如果片选信号有效状态机进入START状态 同时输出给链路层控制器MCS端口低信号选通链路层芯片寄存器状态机进入START状态后开始检测读写使能信号如果读

写信号有效则进入RD0 WR0状态 同时向链路层控制器芯片读写的地址在RD0 WR0状态中检测链路层控制器芯片的MCA管脚信号在MCA有效时读写有效数据并向DSP输出RDY有效信号状态机进入RDi

WRi状态经过一个时钟后释放数据和地址总线返回ID LE状态。

三、 设计实现

目前用于FPGA设计的主流硬件描述语言主要有VHDL和verilog HDL本设计借助VHDL语言实现。下面简要列出实现状态机的VHDL代码结构

将此设计方法实现的电路下载到实际系统中进行验证试验结果表明该设计能成功完成TMS320V33对TS B12LV32芯片读写控制功能。接口后仿真时序如图6所示包括一次写操作和三次读操作。

四、 结论

本设计实现的TMS320V33与1394总线链路层芯片TS B 12LV32的接口设计方法设计思路清晰时序准确并且具有一定的灵活性和通用性其他类似处理器与1394总线链路层芯片的接口都可以采用类似的设计方法。

本文的设计方法为其它各种处理器与外设接口的匹配设计实现提供了有益的参考。

- 芯片嵌入式1394总线接口的设计和实现相关文档

- 接口1394采集卡接口介绍

- 总线带1394接口的笔记本 1394卡

- 描述1394总线接口设计与实现[Word文档]

- 接口1394接口(1394 interface)

- 接口1394采集卡接口介绍

- 接口数据传输接口1394接口优缺点和技术特点简介

瓜云互联:全场9折优惠,香港CN2、洛杉矶GIA高防vps套餐,充值最高返300元

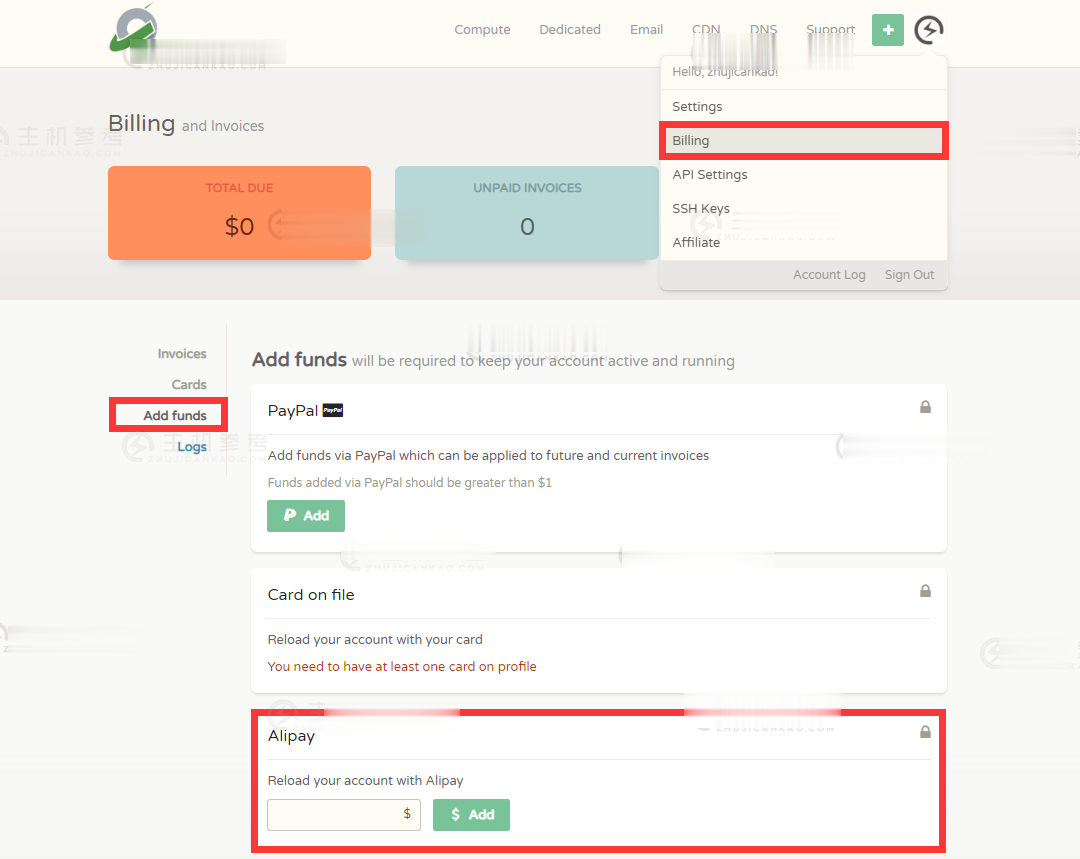

瓜云互联怎么样?瓜云互联之前商家使用的面板为WHMCS,目前商家已经正式更换到了魔方云的面板,瓜云互联商家主要提供中国香港和美国洛杉矶机房的套餐,香港采用CN2线路直连大陆,洛杉矶为高防vps套餐,三网回程CN2 GIA,提供超高的DDOS防御,瓜云互联商家承诺打死退款,目前商家提供了一个全场9折和充值的促销,有需要的朋友可以看看。点击进入:瓜云互联官方网站瓜云互联促销优惠:9折优惠码:联系在线客...

青云互联:美国洛杉矶CN2弹性云限时八折,15元/月起,可选Windows/可自定义配置

青云互联怎么样?青云互联是一家成立于2020年6月的主机服务商,致力于为用户提供高性价比稳定快速的主机托管服务,目前提供有美国免费主机、香港主机、香港服务器、美国云服务器,让您的网站高速、稳定运行。美国cn2弹性云主机限时8折起,可选1-20个IP,仅15元/月起,附8折优惠码使用!点击进入:青云互联官方网站地址青云互联优惠码:八折优惠码:ltY8sHMh (续费同价)青云互联活动方案:美国洛杉矶...

VPS云服务器GT线路,KVM虚vps消息CloudCone美国洛杉矶便宜年付VPS云服务器补货14美元/年

近日CloudCone发布了最新的补货消息,针对此前新年闪购年付便宜VPS云服务器计划方案进行了少量补货,KVM虚拟架构,美国洛杉矶CN2 GT线路,1Gbps带宽,最低3TB流量,仅需14美元/年,有需要国外便宜美国洛杉矶VPS云服务器的朋友可以尝试一下。CloudCone怎么样?CloudCone服务器好不好?CloudCone值不值得购买?CloudCone是一家成立于2017年的美国服务器...

-

淘宝客推广淘宝客推广有用吗?qq讨论组QQ群和讨论组的区别在哪里百度抢票浏览器手机百度浏览器抢票版根本就没预约抢票。噱头而已!微信如何建群在微信里怎么创建一个群别人可以加入扫描二维码的加入迅雷云点播账号求一个迅雷云点播vip的账号,只是看的,绝不动任何手脚。安装迅雷看看播放器怎样安装迅雷看看播放器免费免费建站我想建一个自己的免费网站,但不知道那里有..ios系统苹果手机的系统是什么?网站优化方案网站优化方案怎么写?rewritebase为什么我写.htaccess这个 rewriterule 进入死循环了,高手帮忙修改